Professional Documents

Culture Documents

Uploaded by

pathmakerpkOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Uploaded by

pathmakerpkCopyright:

Available Formats

18th European Signal Processing Conference (EUSIPCO-2010)

Aalborg, Denmark, August 23-27, 2010

AN FPGA-BASED PHYSICAL LAYER IMPLEMENTATION FOR VEHICLE-TO-VEHICLE (V2V) COMMUNICATION

Angelos Amditis1, George C. Kiokes1, Nikolaos K. Uzunoglu2

I-SENSE Group, Institute of Communication and Computer Systems (ICCS), Iroon Polytechniou St. 9, 15773 Athens, Greece, Tel: (30-210) 7722398, Fax: (30-210) 7723557 a.amditis.iccs.gr, gkiokes@iccs.gr, http://i-sense.iccs.gr 2 Microwaves and Optics Lab, School of Electrical and Computer Engineering, National Technical University of Athens, Iroon Polytechniou St. 9, 15773 Athens, Greece, Tel: (30-210) 7722292, Fax: (30-210) 7723557 nuzu@ece.ntua.gr

1

ABSTRACT This paper presents the design and implementation results for IEEE 802.11p Wireless Access in Vehicular Environment Physical layer using Field-Programmable Gate Array (FPGA) hardware. IEEE 802.11p defines modifications of IEEE 802.11a to support Intelligent Transportation Systems applications such as supporting public safety and licensed private operations over communication channels. Towards this objective our implementation goes through two phases. Firstly, a highlevel design tool was used for the Forward Error Correction (FEC) coding chain. Xilinx System Generator is a system-level modeling tool that runs under MatLab Simulink and facilitates FPGA hardware design. Secondly, the use of Very High Speed Integrated Circuit Hardware Description Language (VHDL) was required for the design of the OFDM system. Finally the transmitter and the receiver were implemented into two identical FPGA boards provided by Nallatech using RF evaluation boards from Analog Devices in order to configure our system in 5.9 GHz.

1. INTRODUCTION To begin with, in October 1999 the Federal Communications Commission (FCC), allocated the 5.9 GHz band for DSRC (Dedicated Short Range Communications) - based intelligent transportation systems (ITS) applications and adopted basic technical rules for DSRC operation. IEEE 802.11p standard has been endorsed by ASTM (American Society for Testing and Materials) [1] as the platform of the PHY and MAC layers

for DSRC. The standard has been defined precisely for vehicular communications where high data transfer rates are required in circumstances where minimizing latency in the communication link is important. At first, the standard was designed for Vehicle to Infrastructure (V2I) systems but it was market demand that has caused the adaption with the V2V communications systems. The overall goal is the same: creating a network design useful for vehicle applications, but obviously taking into account the requirements of a safety system. Main purpose of the system is to provide drivers with real-time information beyond what is available through the senses alone. Furthermore, vehicular communication will offer a wide range of applications such as providing traffic management with a real time data for responding to road congestions. FPGA devices are becoming a critical part of every system design and provide a flexible platform to accelerate performance-critical functions in hardware because of the configurability of the devices logic resources. The FPGAs are customized by loading configuration data into the internal memory cells. Our contribution in this paper is to present the design and the implementation of the 802.11p physical layer in Radio Frequency zone. This work divides the design into two functional systems: the FEC coding chain and the OFDM system model. The former was designed using Xilinx System Generator design tool and the latter was designed using VHDL programming language. At the end the transceiver was targeted to Nallatech XtremeDsp Development Kit [2] with Virtex-4 FPGA provided by Xilinx and the configuration in 5.9GHz was carried out with RF evaluation boards from Analog Devices [3].

EURASIP, 2010 ISSN 2076-1465

214

Figure 1 - IEEE 802.11p PHY block diagram

2. OFDM IEEE 802.11P ARCHITECTURE IEEE 802.11p standard specifies an OFDM Physical Layer (Fig. 1) that employs 64 subcarriers. 52 out of the 64 subcarriers are used for actual transmission consisting of 48 data subcarriers and 4 pilot subcarriers to provide transmission of data at rate 3, 4.5, 6, 9, 12, 18, 24, or 27 Mbps. The basic principal of operation is to divide a highspeed binary signal to be transmitted into a number of lower data rate subcarriers. The system uses pilot subcarriers as a reference to disregard frequency or phase shifts of the signal during transmission. Orthogonality amongst the carriers is achieved by separating the carriers by an integer multiples of the inverse of symbol duration of the parallel bit streams. 802.11p specifies seven 10 MHz channels consisting of one control channel and six service channels. Four complex modulation methods (BPSK, QPSK, 16QAM, and 64QAM) are employed, depending on the data rate that can be supported by channel conditions. The maximum antenna input power for some DSRC mandatory channels is 28.8 dBm (750 mW) that enables long range. The PHY layer structure of 802.11p standard is divided into two entities: the Physical Layer Convergence Protocol (PLCP) and the Physical Medium Dependent (PMD) sublayers. PLCP is one convergence procedure to map MAC PDU into a frame format designed for radio transceiver of corresponding PMD layer. PMD layer interacts with PLCP layer and provides the actual means to transmit data on medium.

from the Xilinx Blockset can be integrated seamlessly in Simulink models and are simulated in the same way. The tool provides high-level abstractions that are automatically compiled into an FPGA and access to underlying FPGA resources through low-level abstractions, allowing the construction of highly efficient FPGA designs. We developed a model which is based on an OFDM Library v1.0 FEC Blockset and the WIMAX 802.16-2004 demonstration design kindly offered by Xilinx, and we have simulated Forward Error Correction Coding Chain of the transmitter and the receiver for 802.11p standard. After simulating the model, VHDL code was generated accordingly to our standard defined system parameters and synthesized for specific FPGA device. The coding chain (Fig. 2) of the transmitter consists of the following functional subsystems Randomizer Convolutional Encoder Interleaver Symbol Mapper

3. FEC CODING CHAIN DESIGN In this paper, we have used System Generator to generate VHDL source code from the Xilinx Blockset in Simulink environment for the FEC coding chain. Blocks

At the beginning data are imported serially into the data scrambler. The data scrambler using a 127 bits sequence generator scrambles all bits in the data field to randomize the bit patterns in order to avoid long streams of 1 and 0. After that, the data field shall be coded with a convolutional encoder of coding rate R = 1/2, 2/3, or 3/4, corresponding to the desired data rate. The output bits of the encoder are interleaved using the block interleaver within one OFDM symbol. The interleaved bits are then modulated using BPSK, QPSK, 16QAM, 64QAM modulator.

215

1 In1 2 In2

Rand_Data_IP DataIn

DataOut DataOut RS_Data_OP DataIn

wrData DataIn

In3 Rand_Enable DataOut DataValid Rand_Data_OP

BSID BSID DIUC Rand_OP_Enable DataValid Frm_No FrameNumber Init_Rand Init_Rand Init_Ty pe Init_Type Rand_DIUC_OP DIUC Add_Tail Add_Tail

Dout DataOut

Data DataIn

I I DataOut

1 Out1

4 In4 5 In5

DOutValid DataValid RS_En_OP DataValid

DataVaild DataValid DataValid DataValid dataType DataType Valid DataValid Q Q DataOut

2 Out2

6 In6 7 In7 8 In8

DType DataType DataType DIUC StartSym SymbolStart

StartPulse SymbolStart

DataType DataType

Data Type DataType

Valid_O DataValid

3 Out3

802.11p OFDM PHY Randomiser 9 In9

Newburst BurstStart EndSym SymbolEnd

EndSymbol SymbolEnd

FirstBit SymbolStart

New Symbol SymbolStart

DataType DataType

4 Out4

10 In10

NewFrame FrameStart StartBurst BurstStart

NewBurst BurstStart BurstStart BurstStart NewFrame FrameStart StartFrame FrameStart New Burst New Symbol Out BurstStart SymbolStart

5 Out5

11 In11

rst Reset

802.11p OFDM PHY Convolutional Encoder

12 In12

rst Reset

FrameStart FrameStart

New Frame FrameStart

newBurstOut BurstStart

6 Out6

802.11p OFDM PHY Interleaver 13 In13

rst Reset

newFrameOut FrameStart

7 Out7

802.11p OFDM PHY Symbol Mapper

Figure 2 - IEEE 802.11p transmitter coding chain Xilinx Blockset

4. OFDM HARDWARE DESIGN OFDM modulation is exploiting the fact that multiple data signals can be carried out from the same carry signal. The time space between the data signals which are carried from the carry signal is defined from the ratio 1/f0, where f0 is the transmission duration of an OFDM symbol (symbol=wavelet). During the OFDM data modulation, every data sequence is considered to be available for transmission at any time and they are just separately distributed in the phase spectrum. Then, data spectrums are carried from the frequency to the time field through the inverse Fourier transform and they are transmitted in a wavelet sequence. During the OFDM demodulation, each wavelet is collected in serial sequence and after their transformation to parallel form, they are carried out into the frequency field through the Fourier transformation. A crucial contribution in the modulation and demodulation procedure is given by the serial-to-parallel and parallel-to-serial modules. These modules are implemented in parallel.vhd and serial.vhd files respectively. The parallel component is converting serial data to parallel accepting as input sequential bits and producing bit arrays as output. Analogically, the parallelto-serial component is using the same technique in order to accomplish the bit array to sequential bit transformation. Obviously, in order to implement the different digital data transmission through the same analog transmission signal, a transformation must be occurred so that the transmitted digital data could be safely carried through the carry signal. In this paper, the BPSK modulation is selected, created from the FEC coding chain mostly for simplicity and implementation reasons.

The main component of the OFDM project (Fig.3) is the modem component because it has the role of data receiver-transmitter but also the role of OFDM modulatordemodulator. The receiver - transmitter property is implemented with the coordination of three subcompoments: the txmodem, trx and the the rxmodem modules. The txmodem component is responsible for modulating data through the OFDM modulation and transmitting them. The rxmodem component is responsible for receiving data and demodulation them. Finally, the txrx component is responsible for the data passing through the BPSK modulator-demodulator and also for the communication with systems inputs and outputs. The txmodem implementation is achieved with the presence of two submodules: the input component and the OFDM component. The input component is accepting the modulated through BPSK modulation data and passing them to the OFDM component. The OFDM component accepts the data coming from the input component as data bit arrays (12 bit length) and modulate the incoming data through OFDM modulation. The rxmodem module is operating in analogically way with the txmodem and it is consisted from the OFDM and the output subsystem. The OFDM subsystem is operating as a demodulator and the demodulated data are driven in the output subcomponent. The output subcomponent is responsible for the proper transfer of the OFDM demodulated data to the BPSK demodulator. 5. PHY FPGA IMPLEMENTATION In hardware programming, XILINX ISE [4] software was used to perform the implementation. The Xilinx ISE system is an integrated design environment that that consists of a set of programs to create (capture), simulate and implement digital designs in a FPGA or CPLD target device. All the tools use a graphical user interface (GUI) that allows all programs to be executed from toolbars, menus or icons [5]. All the designs were targeted in two XtremeDSP Developments boards with Xilinx Virtex-4 XC4VSX35-10FF668 FPGA for the transmitter and the receiver respectively. The XtremeDSP Development Kit-IV from Nallatech serves is an ideal development platform for the Virtex-4 FPGA technology and provides an entry into the scalable DIME-II systems. Its dual channel high performance ADCs and DACs, as well as the user programmable Virtex-4 device are ideal to implement high performance signal processing applications such as Software Defined Radio, 3G Wireless, Networking.

216

Figure 3 - OFDM schematic algorithm diagram

Nallatech's FUSE System Software [6] is a Java-based application that provides configuration, control and communications functionality between host systems and Nallatech FPGA computing hardware. This enables developers to design complex processing systems, with seamless integration between software, hardware and FPGA applications. FUSE provides several interfaces, including the FUSE Probe Tool which is ideal for configuration of the FPGA. The XtremeDSP Development Kit-IV features three Xilinx FPGAs - a Virtex-4 User FPGA, a Virtex-II FPGA for clock management and a Spartan-II Interface FPGA. The Virtex-4 device is available exclusively for user designs whilst the Spartan-II is supplied preconfigured with firmware for PCI/USB interfacing. The Virtex-4 XC4VSX35-10FF668 device is intended to be used for the main part of a users design. The Virtex-II XC2V80-4CS144 is intended to be used as a clock configuration device in a design. To connect the development platform at the computer, three options exists, the Joint Test Action Group (JTAG) interface, the Universal Serial Bus (USB) and finally the Peripheral Component Interconnect (PCI) interface can be used. The User FPGA connects to this interface through the Interface FPGA. Analog Devices offers several high-performance modulators and demodulators for operation at frequencies up to 6 GHz. ADL5375 [7] is a Broadband Quadrature Modulator designed for operation from 400 MHz to 6

GHz. Its excellent phase accuracy and amplitude balance enable high performance intermediate frequency or direct radio frequency modulation for communication systems. The ADL5380 [8] is a Broadband Quadrature I-Q demodulator that covers an RF/IF input frequency range from 400 MHz to 6 GHz. ADL5380 demodulator offers outstanding dynamic range suitable for the demanding infrastructure direct-conversion requirements. The differential RF inputs provide a well-behaved broadband input impedance of 50 and are best driven from a 1:1 balun for optimum performance. At the beginning the design run through synthesis, place and route stages, in ISE software and finally the programming bit file and the schematic symbols were generated. After that with FUSE software we located the XtremeDSP Motherboard through USB interface and finally we assigned two bitfiles to the devices for the Virtex-4 and Virtex-2 configuration. The test bed for the transmitter configuration is depicted in Fig 4. The outputs on the Fluke PM3380B oscilloscope for the input signal and the demodulated signal are depicted in Fig. 5 after connected the MCX-BNC cables from the DAC outputs on the board to channels on the oscilloscope. The development kit achieves a top frequency of 105 MHz which means tclk = 9.5ns while utilizing 17% of the occupied slices, 13% of the D Flip-flops and 14% of the dedicated LUTs for the transmitter and the receiver.

217

Low Density Parity Check codes in order to enhance system performance. Extending this work we will develop the whole PHY transmitter and receiver with antennas for real time implementations in fading environment.

INPUT SIGNAL

DEMODULATED SIGNAL

Figure 4 - Test bed using Nallatech XtremeDSP kit, Analog Device RF module and notebook with Fuse software for the transmitter configuration.

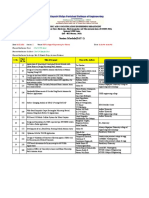

Implementation results for BPSK modulation with code rate are shown in table I. Table I lists speed and resource usage (in terms of the building blocks of an FPGA) results under the following columns: a) Period, the critical path of the circuit in ns, b) LUT, the number of 4-input Look-Up Table function generators required, c) FF, the number of 1bit flip-flops required, d) Slice, the number of FPGA slices required given that an FPGA slice has 2 LUTs and 2 FFs.

Figure 5 - Fluke PM3380B oscilloscope outputs. In channel 1is depicted the generator pulse and in channel 2 is depicted the demodulated signal

REFERENCES [1] ASTM E2213-03 Standard Specification for Telecommunications and Information Exchange Between Roadside and Vehicle Systems 5 GHz Band Dedicated Short Range Communications (DSRC) Medium Access Control (MAC) and Physical Layer (PHY) Specifications [2] Nallatech XtremeDSP Development kit-iv user guide http://www.xilinx.com/support/documentation/boards _and_kits/ug_xtremedsp_devkitIV.pdf [3] http://www.analog.com/en/index.html [4] http://www.xilinx.com/tools/designtools.htm [5] University of Pennsylvania Digital Design Laboratory, Introduction to Xilinx ISE 8.2i http://www.seas.upenn.edu/~ese201/ise/ISEIntroducti on.pdf [6] FUSE System Software User Guide http://www.nallatech.com/indexx.php/productbriefs.html [7] http://www.analog.com/en/rfifcomponents/modulatorsdemodulators/adl5375/ products/product.html [8] http://www.analog.com/en/rfifcomponents/modulatorsdemodulators/adl5380/ products/product.html

IMPLEMENTATION RESULTS OFDM TRANSMITTER OFDM RECEIVER

PERIOD 14534ns 14628ns

LUT 2944 3088

FF 2450 2566

SLICES 1882 1976

TABLE I Implementation results for the transceiver

6. CONCLUSIONS AND FUTURE WORK Taking everything into consideration, this article presents results regarding the design and the implementation of the transceiver for the IEEE 802.11p PHY. The transceiver was successfully developed using two identical Nallatech Development boards. Several modules have been designed and testing is required to obtain the result. Connecting the output of the transmitter to the input of the receiver the preliminary results shows high accuracy between measurements. In the future we intend to perform further experiments examining the 802.11p transceiver with different coding schemes such as

218

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Mathematics For Machine LearningDocument417 pagesMathematics For Machine LearningLê Mạnh93% (28)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Receiver Design Minimum Detectable SignalDocument49 pagesReceiver Design Minimum Detectable SignalpathmakerpkNo ratings yet

- John White Videos of Spooky2 InterfaceDocument24 pagesJohn White Videos of Spooky2 InterfaceTimothy M HallNo ratings yet

- WipAir 8000 Configuration ManualDocument50 pagesWipAir 8000 Configuration ManualFernando Rodriguez80% (5)

- Case Version 6.5 Service ManualDocument276 pagesCase Version 6.5 Service ManualFauza Aryagus80% (5)

- 03 - Inductive Sensors. BALLUFpdf PDFDocument302 pages03 - Inductive Sensors. BALLUFpdf PDFMoisesNo ratings yet

- EE213 Course Outline Ver 2Document6 pagesEE213 Course Outline Ver 2pathmakerpkNo ratings yet

- Two-Line Element Set: Simplified Perturbations Models SGP ModelsDocument7 pagesTwo-Line Element Set: Simplified Perturbations Models SGP ModelspathmakerpkNo ratings yet

- Data StructuresDocument5 pagesData StructurespathmakerpkNo ratings yet

- Two-Line Element Set: Simplified Perturbations Models SGP ModelsDocument7 pagesTwo-Line Element Set: Simplified Perturbations Models SGP ModelspathmakerpkNo ratings yet

- DS/CDMA Near-Far Problem Power ControlDocument7 pagesDS/CDMA Near-Far Problem Power ControlpathmakerpkNo ratings yet

- UMTS/GPRS System Overview From An IP Addressing PerspectiveDocument27 pagesUMTS/GPRS System Overview From An IP Addressing PerspectivefollajNo ratings yet

- Provisioning of 5G Services Employing MachineDocument6 pagesProvisioning of 5G Services Employing MachinepathmakerpkNo ratings yet

- HEC TelecomDocument84 pagesHEC TelecomkarmanNo ratings yet

- Mehran University of Engineering and Technology, Jamshoro Department of Software EngineeringDocument2 pagesMehran University of Engineering and Technology, Jamshoro Department of Software EngineeringpathmakerpkNo ratings yet

- Introduction To WCDMA PDFDocument70 pagesIntroduction To WCDMA PDFMohamed Abdel MonemNo ratings yet

- 09 SpreadSpectrumDocument28 pages09 SpreadSpectrumChandan SasamalNo ratings yet

- Ai Ssuet 2018 FinalDocument13 pagesAi Ssuet 2018 FinalpathmakerpkNo ratings yet

- University NameDocument18 pagesUniversity NamepathmakerpkNo ratings yet

- SDN 5g Ssuet 2019Document8 pagesSDN 5g Ssuet 2019pathmakerpkNo ratings yet

- List of Chinese Universities Without Application FeeDocument1 pageList of Chinese Universities Without Application FeesaminaNo ratings yet

- Rent Receipt: Dated: - Land LordDocument2 pagesRent Receipt: Dated: - Land LordpathmakerpkNo ratings yet

- Cloud Mobile 2018 SSUETDocument3 pagesCloud Mobile 2018 SSUETpathmakerpkNo ratings yet

- Multi RateDocument1 pageMulti RatepathmakerpkNo ratings yet

- Python BookDocument669 pagesPython Bookpathmakerpk0% (1)

- PR Slide Spring 2017Document5 pagesPR Slide Spring 2017pathmakerpkNo ratings yet

- Complete Course Outline for Telecommunication Engineering DegreeDocument5 pagesComplete Course Outline for Telecommunication Engineering DegreepathmakerpkNo ratings yet

- Design of The 11011 Sequence Detector: Slide 1 of 23 Slides Revised 9/28/2009Document23 pagesDesign of The 11011 Sequence Detector: Slide 1 of 23 Slides Revised 9/28/2009sgoshi84No ratings yet

- User Input 1Document1 pageUser Input 1pathmakerpkNo ratings yet

- VSWR and Reflection Coefficient ExplainedDocument5 pagesVSWR and Reflection Coefficient ExplainedpathmakerpkNo ratings yet

- Os Midterm Answers 2011Document3 pagesOs Midterm Answers 2011pathmakerpkNo ratings yet

- Lesson 01 - Iit - Iartificial Intelligence 2 AI PDFDocument11 pagesLesson 01 - Iit - Iartificial Intelligence 2 AI PDFVille4everNo ratings yet

- FM PMDocument3 pagesFM PMpathmakerpkNo ratings yet

- Control of Real and Reactive Power Using A Novel SVC Feedback System For Load Sharing in Grid Connected PV Power SystemDocument9 pagesControl of Real and Reactive Power Using A Novel SVC Feedback System For Load Sharing in Grid Connected PV Power SystemOlanshileNo ratings yet

- WinnerDocument26 pagesWinnerNguyễn Tấn PhátNo ratings yet

- 2.4a Synchronous Buck-Boost DC DC Converter Ic DatasheetDocument21 pages2.4a Synchronous Buck-Boost DC DC Converter Ic Datasheetsilvanna alvarez castroNo ratings yet

- SXTWL2WH-17/17-65/65V-iVT Multi-band Base Station AntennaDocument4 pagesSXTWL2WH-17/17-65/65V-iVT Multi-band Base Station Antennakai tangNo ratings yet

- 1.5KE Series: 1500W Transient Voltage SuppressorDocument6 pages1.5KE Series: 1500W Transient Voltage SuppressorjefriNo ratings yet

- Concept Strengthening Sheet CSS 03 Based On AIATS 03 CF+OYM PhysicsDocument7 pagesConcept Strengthening Sheet CSS 03 Based On AIATS 03 CF+OYM PhysicsJIDNESH BHERENo ratings yet

- ICMEET Paper Presentations Schedule PDFDocument6 pagesICMEET Paper Presentations Schedule PDFKrishna ChaitanyaNo ratings yet

- Digikey Part # MFG Part # Description Qty Cost Line Cost Designator Total CostDocument1 pageDigikey Part # MFG Part # Description Qty Cost Line Cost Designator Total CostSmit BhenjaliyaNo ratings yet

- Jadual Peperiksaan Akhir Semester Ii Sesi Akademik 2020/2021 Bagi Program Ijazah Sarjana Muda Dan Diploma (Draf 1)Document127 pagesJadual Peperiksaan Akhir Semester Ii Sesi Akademik 2020/2021 Bagi Program Ijazah Sarjana Muda Dan Diploma (Draf 1)Amirul AdamNo ratings yet

- Technical Solution: Hebei Kaixiang Electrical Technology Co., LTDDocument10 pagesTechnical Solution: Hebei Kaixiang Electrical Technology Co., LTDanon_579053479No ratings yet

- Freescale MC9S08SH8 Hoja de DatosDocument341 pagesFreescale MC9S08SH8 Hoja de DatosfcoparraortizNo ratings yet

- Test ShortDocument52 pagesTest Shortsaikiran loyaNo ratings yet

- EMW - Module - 3Document50 pagesEMW - Module - 3ROHITH MYSURUNo ratings yet

- Transformer Protection Final Rev.01 PDFDocument2 pagesTransformer Protection Final Rev.01 PDFNader Asgar Pangarungan MamarobaNo ratings yet

- Texasinstruments Ds90ub960q1evm Datasheets 4805Document60 pagesTexasinstruments Ds90ub960q1evm Datasheets 4805BB minNo ratings yet

- 1SFC132094M0201 PSTX AB ProfinetDocument28 pages1SFC132094M0201 PSTX AB ProfinetJovanyNo ratings yet

- Lesson in RoboticsDocument10 pagesLesson in RoboticsScottie PollardNo ratings yet

- Fault Code P1830 (Controlled Manual Gearbox ECU)Document2 pagesFault Code P1830 (Controlled Manual Gearbox ECU)thierry.fifieldoutlook.comNo ratings yet

- Milenium Carlyle PDFDocument21 pagesMilenium Carlyle PDFvickers100% (1)

- Pneumatic Sensing Elements and Self-Balancing InstrumentsDocument29 pagesPneumatic Sensing Elements and Self-Balancing InstrumentsAlessio ScarabelliNo ratings yet

- Simulation Development of Microcontroller Based Triggering Circuit Using Proteus SoftwareDocument4 pagesSimulation Development of Microcontroller Based Triggering Circuit Using Proteus SoftwareVincent RonaldoNo ratings yet

- Heatmasters: Mobile Heat Treatment EquipmentDocument2 pagesHeatmasters: Mobile Heat Treatment EquipmentAnand SankarNo ratings yet

- SIL3 24/220Vdc/Vac Transistor-Out Detector: Technical DataDocument2 pagesSIL3 24/220Vdc/Vac Transistor-Out Detector: Technical DataMohamed OmarNo ratings yet

- AsdDocument69 pagesAsdcatruzzNo ratings yet

- CNC Lesson PlanDocument8 pagesCNC Lesson Planmagesh.mxNo ratings yet

- Bafco BrochDocument12 pagesBafco BrochBadrian BadbadNo ratings yet