Professional Documents

Culture Documents

Actel Device Architecture

Uploaded by

Uday KumarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Actel Device Architecture

Uploaded by

Uday KumarCopyright:

Available Formats

Introduction to Actel FPGA Architecture Actel Device Architecture

Architecture of an Actel FPGA is very similar to that of a conventional gate array. The core of the device consists of simple logic modules used to implement the required logic gates and storage elements. These logic modules are interconnected with an abundance of segmented routing tracks. Surrounding the logic core is the interface to the I/O pads of the devices. This interface consists of I/O modules that translate and interconnect the logic signals from the core of the device to the FPGA output pads.

The major elements of the Actel FPGA architecture are: I/O modules Interconnect resources Clocking resources Logic modules

Figure 1 Basic Actel FPGA Architecture

1

Table 1 Quick Summary of Key Architectural Features of Actel FPGA Families

Logic Module Descriptions The optimal logic module should provide the user with the correct mix of performance, efficiency, and ease of design required to implement the application. Simple Logic Module The first Actel logic module was the Simple Logic Module used in the ACT 1 family. It is a multiplexer-based logic module. Logic functions are implemented by interconnecting signals from the routing tracks to the data inputs and select lines of the multiplexers. Inputs can also be tied to a logical 1 or 0 if required, since these signals are always available in the routing channel.

Figure 2 Simple Logic Module

An example logic function implemented with the Actel Simple Logic Module.

Figure 3 Example of a Logic Function Implemented with the ACT 1 Simple Logic Module Combinatorial Logic Module Some improvements were made to the Simple Logic Module when the second generation ACT 2 family was developed. The Simple Logic Module was replaced with two different logic modules, one for implementing combinatorial logic, (the Combinatorial Logic Module) and one for implementing storage elements (the Sequential Logic Module).

Figure 4 Combinatorial Logic Module

Figure 5 Example of a Logic Function Implemented with the Combinatorial Logic Module Sequential Logic Module The Sequential Logic Module, shown in the diagram in Figure 6, has a combinatorial logic front end with a dedicated storage element on the output of the logic module. The storage element can be either a register or a latch. The clock input can be selected to be either active high or active low. One of the logic gates is missing on the combinatorial logic section, making it slightly different from the Combinatorial Logic Module.

Figure 6 Sequential Logic Module

Enhanced Sequential Logic Module The Enhanced Sequential Logic Module used in the ACT 3 family is a refinement of the Sequential Logic Module. The reset input on the register in the sequential section is not shared with the combinatorial logic function, so the full combinatorial logic is available in the Combinatorial Logic Module to be used in front of the register. This makes all single module combinatorial logic functions usable in front of the storage element.

Figure 7 S-Module Diagram

Wide Decode Logic Module The Wide Decode Logic Module consists of a seven-input AND gate with selectable inversion on the output. The output of this module bypasses the normal routing network and connects directly to a particular output buffer. This feature minimizes the delay from the module output to the device pad and is ideal for implementing wide-decode functions typically implemented in small PLD devices. The Wide Decode Logic Module output is also available to the core logic modules, so it can be used in conjunction with other logic functions internal to the device. Embedded Dual-Port SRAM The SRAM blocks are arranged in 256-bit blocks, which can be configured as 32 x 8 or 64 x 4. SRAM blocks can be cascaded to form wider or deeper memory blocks. The SRAM is dual ported, with separate read and write addresses, a separate data input port (for writes), and a separate data output port (for reads). Reads and writes are controlled by separate clocked read and write enables, easing timing requirements for using the SRAM. The dual-port structure is ideal for implementing FIFO, burst buffers, and internal register storage for status, control, or constant data.

Channeled Interconnect All Actel devices use a channeled interconnect architecture to make connections between internal logic modules and device I/O pins. This architecture is similar to that of a channeled gate array, in that horizontal tracks span the length of the array with a variety of predefined segmentation lengths. In addition, tracks can be joined together to construct longer tracks, when required, by programming an interconnect fuse. Logic module outputs span four channels (two above and two below) and can be connected to any track. This means that most signals require only two fuses to connect any logic module output to any logic module input. There are enough routing resources available in Actel devices so that place and route is an automatic task. No hand routing is required. Clocking Resources Actel devices have a wide range of clocking flexibility. Every sequential elements clock input can be connected to regular interconnects within the channel, as well as to optimized clocking resources. Each Actel device also has dedicated clocking resources on-chip to improve clock performance and to simplify the design of sequential signals. Clocking resources can also be used, in most cases, as high-drive global signals like reset, output enable, or select signals. Routed Clocks All Actel FPGA families have one or two special buffers that provide high-drive, lowskew signals and that can be used to drive any signal requiring these characteristics. These routed clocks are distributed to every routing channel and are available to every logic module. This allows a routed clock signal to be used by both Sequential and Combinatorial Logic Dedicated Array Clock The ACT 3 family has an additional clocking resource consisting of a high-speed dedicated clock buffer optimized for driving the sequential modules in the core array. This clock buffer can be driven from an external pin or from an internal signal. Dedicated I/O Clock The ACT 3 family has another clocking resource consisting of a high-speed dedicated clock buffer optimized for driving the sequential modules in the I/O modules. The dedicated I/O clock is optimized for driving I/O modules and cant drive storage elements in the array. If all storage elements need to be driven from a common clock, the array clock and I/O clock can be connected together externally.

Quad Clocks Clocking resource consisting of four special high-drive buffers called quadrant clocks. Each buffer provides a high-drive signal that spans about one-quarter of the device (a quadrant). These buffers can be used for fast local clocks (perhaps for prescaled shifters or counters), for widewidth mux selects, or for I/O enables. I/O Module Descriptions Each Actel FPGA family has a slightly different I/O module. The Simple I/O Module, found in the ACT 1 family, is optimized for low cost, and the Latched I/O Module, found in the Integrator Series, offers a balance of speed and cost (value). The Registered I/O Module in ACT3 is optimized for high speed in synchronous applications. Simple I/O Module The Simple I/O Module (Figure 8) used in the ACT 1 family was the first I/O module developed by Actel and is a simple I/O buffer with interconnections to the logic array. All input, output, and three-state control signals are available to the array.

Figure 8 Simple I/O Module Latched I/O Module The Latched I/O Module, shown in the diagram in Figure 9, is used in the Integrator Series and is slightly more complicated than the Simple I/O Module. The Latched I/O Module contains input and output latches that can be used as such or combined with internal latches to construct input or output registers.

Figure 9 Latched I/O Module Registered I/O Module The Registered I/O Module, used in the ACT 3 family devices, is optimized for speed and functionality in synchronous system designs. It contains complete registers at both the input and output paths, as shown in the diagram in Figure 10. Data can be stored in the output register (under control of the ODE, output data enable, signal), or it can bypass the register if the OTB control bit is tied low. Both the output register and the input register can be cleared or preset via the global IOPCL signal, and both are clocked via the IOCLK global signal. The output of the output register can be selected as an input to the array (on the Y signal).

Figure 10 Registered I/O Module

You might also like

- PLD Architectures and TestingDocument37 pagesPLD Architectures and TestingParesh SawantNo ratings yet

- Spartan and Spartan-XL FPGA Families Data Sheet: Product SpecificationDocument83 pagesSpartan and Spartan-XL FPGA Families Data Sheet: Product SpecificationAkash ShejuleNo ratings yet

- Introduction To Actel FPGA Architecture PDFDocument8 pagesIntroduction To Actel FPGA Architecture PDFsaipranathiNo ratings yet

- FPGA Arquitectura BasicaDocument7 pagesFPGA Arquitectura BasicaJesus LeyvaNo ratings yet

- Single Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGADocument4 pagesSingle Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGAInternational Organization of Scientific Research (IOSR)No ratings yet

- Lec 2Document26 pagesLec 2sk2417No ratings yet

- Implementation of Digital Clock On FPGA: Industrial Training Report ONDocument26 pagesImplementation of Digital Clock On FPGA: Industrial Training Report ONAdeel HashmiNo ratings yet

- Spartan II FPGADocument18 pagesSpartan II FPGAA B ShindeNo ratings yet

- Manual WincuplDocument43 pagesManual WincuplRaul Alberto Lizarraga CuevasNo ratings yet

- Altera Epf8282alc84 4Document62 pagesAltera Epf8282alc84 4lim hyNo ratings yet

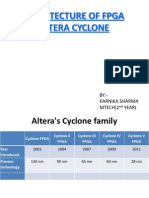

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Document29 pagesArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- FPGADocument20 pagesFPGANanda Ganesh Kumar KingNo ratings yet

- Implementing Security in Industrial AutomationDocument63 pagesImplementing Security in Industrial AutomationKeerthi KeethuNo ratings yet

- FPGA Architecture and ImplementationDocument59 pagesFPGA Architecture and ImplementationManas BhattNo ratings yet

- Metal Gas Detec RoboDocument37 pagesMetal Gas Detec RoboVijay SaiNo ratings yet

- Core8051 DsDocument41 pagesCore8051 DsMinh Trí KnightNo ratings yet

- CS305 M5 Ktunotes - inDocument29 pagesCS305 M5 Ktunotes - inAkshay SNo ratings yet

- The Xilinx VirtexDocument9 pagesThe Xilinx VirtexShreyas MaheshNo ratings yet

- FPGA Basics and Nios II Processor Intro: Week 2 Dr. Kimberly E. Newman Hybrid Embedded SystemsDocument22 pagesFPGA Basics and Nios II Processor Intro: Week 2 Dr. Kimberly E. Newman Hybrid Embedded Systemskanthi_thotaNo ratings yet

- Fpga Implimentation of LCD Display1Document77 pagesFpga Implimentation of LCD Display1praveen_banthiNo ratings yet

- Compact DeviceDocument57 pagesCompact Devicesriram kantipudiNo ratings yet

- Messenger Development Without Internet Using Zigbee TechnologyDocument89 pagesMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyNo ratings yet

- Programmable Logic Arrays (PLA) ExplainedDocument5 pagesProgrammable Logic Arrays (PLA) ExplainedSitotaw NigussieNo ratings yet

- Ep3c10 PDFDocument10 pagesEp3c10 PDFramNo ratings yet

- Antifuse-Based Fpgas: Actel & QuicklogicDocument38 pagesAntifuse-Based Fpgas: Actel & QuicklogicSaurabh KukretiNo ratings yet

- Field Programmable Gate ArrayDocument18 pagesField Programmable Gate ArrayTushar GargNo ratings yet

- PLC Industrial AutoDocument17 pagesPLC Industrial Autoselar7347No ratings yet

- The Altera Max 7000 Family of CPLDS: 1. Logic Array Blocks (Labs) 2. Macrocell Arrays Prefabricated Arrays of HigherDocument1 pageThe Altera Max 7000 Family of CPLDS: 1. Logic Array Blocks (Labs) 2. Macrocell Arrays Prefabricated Arrays of HigherMohammad SalmanNo ratings yet

- m10 HandbookDocument593 pagesm10 HandbookHChNo ratings yet

- Fpgas - Under The Hood: Figure 1. The Different Parts of An FpgaDocument14 pagesFpgas - Under The Hood: Figure 1. The Different Parts of An FpgaTolga KökalpNo ratings yet

- 8515 CompleteDocument101 pages8515 Completefiddu4bvNo ratings yet

- FpgaDocument6 pagesFpgaÁryâñ SinghNo ratings yet

- Remote LocatorDocument32 pagesRemote LocatorBhagya ShreeNo ratings yet

- C 789Document18 pagesC 789Ác QủyNo ratings yet

- Name Muhammad Ahsan Abbas Roll No. Sp-2018/BSCS/030 Assignment Digital Logic DesignDocument5 pagesName Muhammad Ahsan Abbas Roll No. Sp-2018/BSCS/030 Assignment Digital Logic DesignMuyammad Ahsan abbasNo ratings yet

- 8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash AT90S2313Document92 pages8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash AT90S2313nullsoft69No ratings yet

- AT89S52Document19 pagesAT89S52Nikhith ReddyNo ratings yet

- Lecture 2 - Introduction To FPGAs PDFDocument14 pagesLecture 2 - Introduction To FPGAs PDFVenkateswara ReddyNo ratings yet

- Design of Embedded ProcessorsDocument80 pagesDesign of Embedded ProcessorsSayan Kumar KhanNo ratings yet

- 2.1 Microcontroller: Embedded SystemsDocument23 pages2.1 Microcontroller: Embedded SystemspavanNo ratings yet

- Automatic Speed BreakerDocument69 pagesAutomatic Speed BreakerRohitesh KumarNo ratings yet

- 2nd CHAPTER MechatronicsDocument50 pages2nd CHAPTER MechatronicspremscrebdNo ratings yet

- Design and Implementation of Traffic Controller Using VHDL: Interim Project ReportDocument21 pagesDesign and Implementation of Traffic Controller Using VHDL: Interim Project ReportAugusto Germano da SilvaNo ratings yet

- Clock Skew Minimization During FPGA PlacementDocument6 pagesClock Skew Minimization During FPGA PlacementpnrgoudNo ratings yet

- FPGA TechnologyDocument26 pagesFPGA TechnologyvinaypantraNo ratings yet

- LAB04Document15 pagesLAB04زياد عبدالله عبدالحميدNo ratings yet

- Microprocessor 8085 - NotesDocument36 pagesMicroprocessor 8085 - NotesDr. N.Shanmugasundaram92% (72)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureFrom EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureRating: 1 out of 5 stars1/5 (1)

- PLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsFrom EverandPLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsRating: 5 out of 5 stars5/5 (1)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- FPGA Implementation of Diffie-Hellman Key Exchange for Zero Knowledge ProofDocument47 pagesFPGA Implementation of Diffie-Hellman Key Exchange for Zero Knowledge ProofUday KumarNo ratings yet

- MSC - 12 - Abstract - Implementation of Hold Enable BistcontrollerDocument1 pageMSC - 12 - Abstract - Implementation of Hold Enable BistcontrollerUday KumarNo ratings yet

- IBPS Specialist IT Officer Previous PaperDocument14 pagesIBPS Specialist IT Officer Previous PapermtkumarNo ratings yet

- Analog Devices India Hyderabad Design Center Address DetailsDocument1 pageAnalog Devices India Hyderabad Design Center Address DetailsUday KumarNo ratings yet

- Egate DDSDocument1 pageEgate DDSUday KumarNo ratings yet

- Figures TX MriDocument6 pagesFigures TX MriUday KumarNo ratings yet

- RF TX MRIDocument4 pagesRF TX MRIUday KumarNo ratings yet

- What Sorts of Jobs Does An Vlsi or Asic Engineer Do?Document10 pagesWhat Sorts of Jobs Does An Vlsi or Asic Engineer Do?Uday KumarNo ratings yet

- 42 DesignDocument13 pages42 DesignUday KumarNo ratings yet

- FIR CodeDocument2 pagesFIR CodeUday KumarNo ratings yet

- Researchpaper Novel Low Power and High Speed 8T Full AdderDocument5 pagesResearchpaper Novel Low Power and High Speed 8T Full AdderUday KumarNo ratings yet

- Xilinx 13x Modelsim 10Document5 pagesXilinx 13x Modelsim 10Uday KumarNo ratings yet

- Simulink TutorialDocument56 pagesSimulink TutorialUday KumarNo ratings yet

- Design and Implementation of Digital Signal Processing Hardware FDocument124 pagesDesign and Implementation of Digital Signal Processing Hardware FUday KumarNo ratings yet

- CIC Filter Specifications and TheoryDocument6 pagesCIC Filter Specifications and TheoryUday KumarNo ratings yet

- 455 1213 1 PBDocument7 pages455 1213 1 PBUday KumarNo ratings yet

- Parameters Value: Table 1. Wimax DDC Example Total Spectrum RequirementDocument1 pageParameters Value: Table 1. Wimax DDC Example Total Spectrum RequirementUday KumarNo ratings yet

- CIC Filter IntroductionDocument6 pagesCIC Filter IntroductionvvigyaNo ratings yet

- Fpga Job How To Get - 1Document3 pagesFpga Job How To Get - 1Uday KumarNo ratings yet

- Alberto QunchaOrDocument4 pagesAlberto QunchaOrUday KumarNo ratings yet

- 16.low Power Efficient Built in Self TestDocument5 pages16.low Power Efficient Built in Self TestUday KumarNo ratings yet

- 30Document8 pages30Uday KumarNo ratings yet

- AdcDocument4 pagesAdcUday KumarNo ratings yet

- Cpmans LisyDocument12 pagesCpmans LisyUday KumarNo ratings yet

- Verilog Basics in 15 PagesDocument14 pagesVerilog Basics in 15 PagesUday KumarNo ratings yet

- IJERTV2IS100479Document8 pagesIJERTV2IS100479Uday KumarNo ratings yet

- VLSI & ASIC Part2Document35 pagesVLSI & ASIC Part2Uday KumarNo ratings yet

- 594 1837 1 PBDocument14 pages594 1837 1 PBUday KumarNo ratings yet

- 6Document4 pages6Uday KumarNo ratings yet

- Lec11 Pipeline IntroductionDocument26 pagesLec11 Pipeline IntroductionUday KumarNo ratings yet

- BECS-C18 Computerized Embroidery Machine Owner's ManualDocument206 pagesBECS-C18 Computerized Embroidery Machine Owner's ManualSayantan RahaNo ratings yet

- Apple Net Names Refrence PDFDocument13 pagesApple Net Names Refrence PDFAlex LuzNo ratings yet

- How To Update Xperia X8 To Gingerbread or Froyo Custom ROMDocument25 pagesHow To Update Xperia X8 To Gingerbread or Froyo Custom ROMmail6989No ratings yet

- LNP ProjectDocument12 pagesLNP ProjectbugyourselfNo ratings yet

- RT Linux Vxworks Comparison WhitepaperDocument8 pagesRT Linux Vxworks Comparison WhitepapersayoneeNo ratings yet

- Assignment - Bca - Introduction To ItDocument16 pagesAssignment - Bca - Introduction To Itraj1182100% (1)

- Manual Part 2 Engineering & Technical References: REF 542 PlusDocument248 pagesManual Part 2 Engineering & Technical References: REF 542 PlusHatem HusseinNo ratings yet

- P/Q-Motherboards: User ManualDocument96 pagesP/Q-Motherboards: User ManualJulio César Palomino PláceresNo ratings yet

- COM100E DatasheetDocument1 pageCOM100E DatasheetJun OrtizNo ratings yet

- HP LED IPS Monitor N246v 23.8 Inch (1RM28AA)Document4 pagesHP LED IPS Monitor N246v 23.8 Inch (1RM28AA)Anonymous a8htUWB10No ratings yet

- Bcc201 SLM LibraryDocument432 pagesBcc201 SLM LibraryTusharr AhujaNo ratings yet

- Upgrade Instructions: Valid For Sinumerik 840D Software Version 07.04.36.00Document15 pagesUpgrade Instructions: Valid For Sinumerik 840D Software Version 07.04.36.00Sam eagle goodNo ratings yet

- MOST System On Chip: Final Product Data SheetDocument256 pagesMOST System On Chip: Final Product Data SheetRamil IsmayilovNo ratings yet

- De2u2134g 11312344Document4 pagesDe2u2134g 11312344Cristi IversonNo ratings yet

- ESPEC MVI56E MCMR ModbusDocument3 pagesESPEC MVI56E MCMR ModbusFelixWhiteNo ratings yet

- SHS-PRE-FINAL ExamDocument2 pagesSHS-PRE-FINAL ExamDante NavajaNo ratings yet

- LeafletDocument2 pagesLeafletrloopelectricalsolutionsNo ratings yet

- Compet I Do Resele CDocument8 pagesCompet I Do Resele CJorge A Rojas MNo ratings yet

- Fluid Dynamic Bearing Spindle Motors: Their Future in Hard Disk DrivesDocument3 pagesFluid Dynamic Bearing Spindle Motors: Their Future in Hard Disk DrivesMarlon SepilloNo ratings yet

- FPGA Simon Game With VGA Controller - Part 1Document46 pagesFPGA Simon Game With VGA Controller - Part 1Monique Kirkman-Bey75% (4)

- Eagle Server Installation GuideDocument21 pagesEagle Server Installation Guideoskrmkt0% (1)

- Architecture of 80386Document39 pagesArchitecture of 80386Jaimon JacobNo ratings yet

- HOW TO - Upgrade VNXe FirmwareDocument3 pagesHOW TO - Upgrade VNXe FirmwareVosak BoudaNo ratings yet

- CH 6 - Storage Virtualization-2Document35 pagesCH 6 - Storage Virtualization-2SALMAN ASIF SNo ratings yet

- Duplicated Avaya Aura Communication Manager On Vmware: Solution & Interoperability Test LabDocument32 pagesDuplicated Avaya Aura Communication Manager On Vmware: Solution & Interoperability Test LabDaniel SepulvedaNo ratings yet

- OpenScape Business V1, Service Documentation, Issue 20Document498 pagesOpenScape Business V1, Service Documentation, Issue 20Daniel German ArriagaNo ratings yet

- Toyota Key Programmer GuideDocument4 pagesToyota Key Programmer GuideRendy RedyNo ratings yet

- 8204 EnglishDocument44 pages8204 EnglishmarceluuNo ratings yet

- 2015-11-30 20.05.50 GraphicsDocument4 pages2015-11-30 20.05.50 GraphicsSilviu MunteanNo ratings yet

- 10 A. Addition of Two 16 - Bit Number Stored in Register Pair.Document4 pages10 A. Addition of Two 16 - Bit Number Stored in Register Pair.DeepakNo ratings yet