Professional Documents

Culture Documents

Lab

Uploaded by

ravi855885Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab

Uploaded by

ravi855885Copyright:

Available Formats

EC-2-5EC7-1

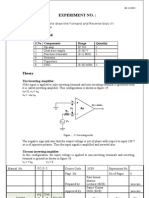

EXPERIMENT NO.1

Object:- Op-Amp characteristics and get data for input bias current, measure the outputoffset voltage and reduce it to zero and calculate slew rate.

Apparatus Required:S.no 1. 2. 3. 4. 5. 6 Components Op-amp Dual trace supply Function Generator Resistors Capacitors CRO (0-30) MHz 1 Range IC 741 (0-30) V (0-1) MHz 1 1 1 Quantity

Theory:An operational amplifier or op-amp is a linear integrated circuit that has a very high voltage gain, high input impedance and low output impedance. Op-amp is basically a differential amplifier whose basic function is to amplify the difference between two input signals. Op-amp has five basic terminals, that is, two input terminals, one o/p terminal and two power supply terminals. Pin2 is called the inverting input terminal and it gives opposite polarity at the output if a signal is applied to it. It produces a phase shift of 180o between input and output. Pin3 is called the non-inverting terminal that amplifies the input signal without inversion, i.e., there is no phase shift or i/p is in phase with o/p. The op-amp usually amplifies the difference between the voltages applied to its two input terminals. Two further terminals pins 7 and 4 are provided for the connection of positive and negative power supply voltages respectively. Terminals 1 and 5 are used for dc offset. The pin 8 marked NC indicates No Connection.

Manual No

EC-2-1

Course Code Page No Prepared by Approved by

5EC7 Kratika sharma Lecturer (ECE) Sanjiv Kumar HOD (ECE)

Name

Experiment No No of Pages

1 7

09-01-2013

09-01-2013

Name

sign Date Rev No

Sign

Date

Vivekananda Institute of Technology, Jaipur

EC-2-5EC7-1

Study of op-amp

Offset Null Inverting i/p Non Inverting i/p V-

1 2

8 7

N/C V+

IC 741

3 4 6

O/p

Offset Null

Block schematic of op-amp

V2 V1

-

Diff amp

Diff amp

Buffer & level translator

O/p driver

V0

Figure: - 1.1 Block diagram of Op. amp.

The block diagram of op-amp shows 2 difference amplifiers, a buffer for less loading, a level translator for adjusting operating point to original level and o/p stage. An ideal op-amp should have the following characteristics: 1. 2. 3. 4. 5. Infinite bandwidth infinite input resistance infinite open loop gain zero output resistance zero offset.

Op-amps have two operating configurations; open loop and closed loop. In open loop configuration, it can operate as a switch but gain is uncontrolled. In closed loop configuration, gain can controlled by feedback resistance Rf and input resistance Rin.

1.1 Parameters of OPAMP: Manual No EC-2-1 Course Code Page No Prepared by Approved by Name sign Date Rev No Kratika sharma Lecturer (ECE) Sanjiv Kumar HOD (ECE)

Name Sign

5EC7

Experiment No No of Pages

1 7

09-01-2013

09-01-2013

Date

Vivekananda Institute of Technology, Jaipur

EC-2-5EC7-1

The various important parameters of OPAMP are follows: 1.1.1 Input Offset Voltage: Input offset voltage is defined as the voltage that must be applied between the two input terminals of an OPAMP to null or zero the output figure 1.1, shows that two dc voltages are applied to input terminals to make the output zero. Vio = Vdc1 - Vdc2 Vdc1 and Vdc2 are dc voltages and RS represents the source resistance. Vio is the difference of Vdc1 and Vdc2. It may be positive or negative. For a 741C OPAMP the maximum value of Vio is 6mV. It means a voltage 6 mV is required to one of the input to reduce the output offset voltage to zero. The smaller the input offset voltage the better the differential amplifier, because its transistors are more closely matched. 1.1.2 Input offset Current: The input offset current Iio is the difference between the currents into inverting and noninverting terminals of a balanced amplifier. Iio = | IB1 - IB2 | The Iio for the 741C is 200nA maximum. As the matching between two input terminals is improved, the difference between IB1 and IB2 becomes smaller, i.e. the Iio value decreases further. For a precision OPAMP 741C, Iio is 6 nA 1.1.3 Input Bias Current: The input bias current IB is the average of the current entering the input terminals of a balanced amplifier i.e. IB = (IB1 + IB2 ) / 2 For 741C IB(max) = 700 nA and for precision 741C IB = 7 nA

Figure: - 1.1

1.1.4. Differential Input Resistance: (Ri) Ri is the equivalent resistance that can be measured at either the inverting or non-inverting Manual No EC-2-1 Course Code Page No Prepared by Approved by Name sign Date Rev No Kratika sharma Lecturer (ECE) Sanjiv Kumar HOD (ECE)

Name Sign

5EC7

Experiment No No of Pages

1 7

09-01-2013

09-01-2013

Date

Vivekananda Institute of Technology, Jaipur

EC-2-5EC7-1

input terminal with the other terminal grounded. For the 741C the input resistance is relatively high 2 M. For some OPAMP it may be up to 1000 G ohm. 1.1.5. Input Capacitance: (Ci) Ci is the equivalent capacitance that can be measured at either the inverting and non-inverting terminal with the other terminal connected to ground. A typical value of Ci is 1.4 pf for the 741C. 1.1.6. Offset Voltage Adjustment Range: 741 OPAMP have offset voltage null capability. Pins 1 and 5 are marked offset null for this purpose. It can be done by connecting 10 K ohm pot between 1 and 5 as shown in figure 21

Figure: - 1.2 Offset Voltage Adjustment

By varying the potentiometer, output offset voltage (with inputs grounded) can be reduced to zero volts. Thus the offset voltage adjustment range is the range through which the input offset voltage can be adjusted by varying 10 K pot. For the 741C the offset voltage adjustment range is 15 mV. 1.1.7. Input Voltage Range : Input voltage range is the range of a common mode input signal for which a differential amplifier remains linear. It is used to determine the degree of matching between the inverting and non-inverting input terminals. For the 741C, the range of the input common mode voltage is 13V maximum. This means that the common mode voltage applied at both input terminals can be as high as +13V or as low as 13V. 1.1.8. Common Mode Rejection Ratio (CMRR). CMRR is defined as the ratio of the differential voltage gain Ad to the common mode voltage gain ACM CMRR = Ad / ACM. For the 741C, CMRR is 90 dB typically. The higher the value of CMRR the better is the Manual No EC-2-1 Course Code Page No Prepared by Approved by Name sign Date Rev No Kratika sharma Lecturer (ECE) Sanjiv Kumar HOD (ECE)

Name Sign

5EC7

Experiment No No of Pages

1 7

09-01-2013

09-01-2013

Date

Vivekananda Institute of Technology, Jaipur

EC-2-5EC7-1

matching between two input terminals and the smaller is the output common mode voltage. 1.1.9. Supply voltage Rejection Ratio: (SVRR) SVRR is the ratio of the change in the input offset voltage to the corresponding change in power supply voltages. This is expressed in or in decibels, SVRR can be defined as SVRR io Where is the change in the input supply voltage and io is the corresponding change in the offset voltage. For the 741C, SVRR = 150 V / V. For 741C, SVRR is measured for both supply magnitudes increasing or decreasing simultaneously, with R3 10K. For same OPAMPS, SVRR is separately specified as positive SVRR and negative SVRR. 1.1.10. Large Signal Voltage Gain: Since the OPAMP amplifies difference voltage between two input terminals, the voltage gain of the amplifier is defined as

Because output signal amplitude is much larger than the input signal the voltage gain is commonly called large signal voltage gain. For 741C is voltage gain is 200,000 typically. 1.1.11. Output voltage Swing: The ac output compliance PP is the maximum unclipped peak to peak output voltage that an OPAMP can produce. Since the quiescent output is ideally zero, the ac output voltage can swing positive or negative. This also indicates the values of positive and negative saturation voltages of the OPAMP. The output voltage never exceeds these limits for a given supply voltages +VCC and ?VEE. For a 741C it is 13 V. 1.1.12. Output Resistance: (RO) RO is the equivalent resistance that can be measured between the output terminal of the OPAMP and the ground. It is 75 ohm for the 741C OPAMP. 1.1.13. Output Short circuit Current : In some applications, an OPAMP may drive a load resistance that is approximately zero. Even its output impedance is 75 ohm but cannot supply large currents. Since OPAMP is low power device and so its output current is limited. The 741C can supply a maximum short circuit output current of only 25mA.

1.1.14. Supply Current : IS is the current drawn by the OPAMP from the supply. For the 741C OPAMP the supply current is 2.8 m A. Manual No EC-2-1 Course Code Page No Prepared by Approved by Name sign Date Rev No Kratika sharma Lecturer (ECE) Sanjiv Kumar HOD (ECE)

Name Sign

5EC7

Experiment No No of Pages

1 7

09-01-2013

09-01-2013

Date

Vivekananda Institute of Technology, Jaipur

EC-2-5EC7-1

Design:

Vin = Vout [Unity Gain] & Rin = & Rf = 0

Circuit Diagram

+12V U1 6 IC 741 Vo

2 3 I1

4

1V/1KHz -12V

Figure: - 1.3 slew rate measurement Circuit

Result: We have successfully Op-Amp characteristics and get data for input bias current,

measure the output-offset voltage and reduce it to zero and calculate slew rate.

Viva Question

1. What is Slew Rate? 2. What is the golden rule of op-amps? 3. Is the golden rule always true? 4. How can the op-amp make its inputs equal, if it can only change its output? 5. What are parameters for op-amp? 6. Why do op-amps have a DC offset voltage? 7. How does a designer minimize the effects of the DC offset voltage? 8. Why do op-amps have a (input) bias current and (input) offset current? 9. How does a designer minimize the effects of the bias currents? 10. How does a designer minimize the effects of the offset currents? 11. How do the :A741, TL081 and TLE2037 op-amps compare with respect to DC offset characteristics? 12. How would a designer choose which op-amp to use for a particular DC signal application? What is the reference voltage for the comparator in the given circuit? Manual No EC-2-1 Course Code Page No Prepared by Approved by Name sign Date Rev No Kratika sharma Lecturer (ECE) Sanjiv Kumar HOD (ECE)

Name Sign

5EC7

Experiment No No of Pages

1 7

09-01-2013

09-01-2013

Date

Vivekananda Institute of Technology, Jaipur

EC-2-5EC7-1

Figure: - 1.4 13. Which kind of input makes the summing amplifier circuit possible? 14. What is the formula for power gain when input gain & output gain?

15. Explain pin diagram of Opm 741- IC.

Manual No

EC-2-1

Course Code Page No Prepared by Approved by

5EC7 Kratika sharma Lecturer (ECE) Sanjiv Kumar HOD (ECE)

Name

Experiment No No of Pages

1 7

09-01-2013

09-01-2013

Name

sign Date Rev No

Sign

Date

Vivekananda Institute of Technology, Jaipur

You might also like

- RhombicDocument7 pagesRhombicravi855885No ratings yet

- Tutorial 1 OPTICAL FIBERDocument1 pageTutorial 1 OPTICAL FIBERravi855885No ratings yet

- Dipole AntennaDocument2 pagesDipole Antennaravi855885No ratings yet

- CdmaDocument3 pagesCdmaravi855885No ratings yet

- LabDocument11 pagesLabravi855885No ratings yet

- Lab ManualDocument5 pagesLab Manualravi855885No ratings yet

- Phool Chand Kumawat: Career ObjectivesDocument2 pagesPhool Chand Kumawat: Career Objectivesravi855885No ratings yet

- AddressDocument5 pagesAddressravi855885No ratings yet

- MicroprocessorsDocument27 pagesMicroprocessorsravi855885No ratings yet

- Marketing BookDocument1 pageMarketing Bookravi855885No ratings yet

- Student InformationDocument2 pagesStudent Informationravi855885No ratings yet

- RecommendetionDocument1 pageRecommendetionravi855885No ratings yet

- SyllabusDocument2 pagesSyllabusravi855885No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Tait 2000 PDFDocument20 pagesTait 2000 PDFMutsa NdlovuNo ratings yet

- Analysis and Simulation of Variable Gain Bandwidth ProductDocument141 pagesAnalysis and Simulation of Variable Gain Bandwidth ProductM.Maidul IslamNo ratings yet

- AE MosfetDocument94 pagesAE MosfetDanish Habib Habib MasihNo ratings yet

- Infineon TLE4266 DataSheet v02 61 enDocument16 pagesInfineon TLE4266 DataSheet v02 61 enAnibalNo ratings yet

- HCA8C-4AD User's ManualDocument12 pagesHCA8C-4AD User's ManualHudson CostaNo ratings yet

- Ina 122Document14 pagesIna 122Wasang Juwi PracihnoNo ratings yet

- KAC-929 Service ManualDocument13 pagesKAC-929 Service ManualMarvin VegaNo ratings yet

- Infinite RGB LED CubeDocument9 pagesInfinite RGB LED CubemaurilioctbaNo ratings yet

- TM-D710A/D710E: Service Man UalDocument97 pagesTM-D710A/D710E: Service Man Ualcristi5855No ratings yet

- Signal Integrity and Power Integrity AnalysisDocument51 pagesSignal Integrity and Power Integrity AnalysisvietsangtaoNo ratings yet

- TI Maximizing SNRDocument58 pagesTI Maximizing SNRdhfsi7496No ratings yet

- Lab 1-Bjt AmplifierDocument8 pagesLab 1-Bjt Amplifierhasnain3257100% (1)

- A 16-Bit Carry-Lookahead Adder Using Reversible Energy Recovery Logic For Ultra-Low-Energy SystemsDocument6 pagesA 16-Bit Carry-Lookahead Adder Using Reversible Energy Recovery Logic For Ultra-Low-Energy SystemsAkhil RenukaNo ratings yet

- VCO Design For WLAN 2.4GDocument9 pagesVCO Design For WLAN 2.4GQuang Nguyen-TheNo ratings yet

- Scientech 2601Document58 pagesScientech 2601sarikapravinNo ratings yet

- Ti Ldo PresentationDocument22 pagesTi Ldo PresentationDebolina GhoshNo ratings yet

- EE 302 Final Exam and Histogram F12 PDFDocument4 pagesEE 302 Final Exam and Histogram F12 PDFAnonymous BKSqKEQhnuNo ratings yet

- 4000 Series CMOS Logic ICs - Electronics ClubDocument12 pages4000 Series CMOS Logic ICs - Electronics ClubCasey PowerNo ratings yet

- Interface VGA80x40: VHDL MacroDocument4 pagesInterface VGA80x40: VHDL MacroSwan RavindraNo ratings yet

- Trio Jr599custom ManualDocument34 pagesTrio Jr599custom Manualhaha2012No ratings yet

- VLSI Design TechniquesDocument119 pagesVLSI Design Techniquesrajesh26julyNo ratings yet

- LM13700Document26 pagesLM13700Thomas van SteeNo ratings yet

- The Integrating A/D Converter (ICL7135) : Application Note February 1999Document5 pagesThe Integrating A/D Converter (ICL7135) : Application Note February 1999ytnateNo ratings yet

- Fall 2019 PEE I LAB 5Document25 pagesFall 2019 PEE I LAB 5Andrew Park0% (1)

- 74HC HCT07 CNV 2Document11 pages74HC HCT07 CNV 2MUHAMMAD SISWANTORONo ratings yet

- Niko-Sem: Universal Switching BufferDocument8 pagesNiko-Sem: Universal Switching Bufferroger5858No ratings yet

- Electronics 1 Lab Manual PDFDocument30 pagesElectronics 1 Lab Manual PDFAnonymous 7y7TeR0% (1)

- Jfets: T N F, P 2: HE EW Rontiers ARTDocument5 pagesJfets: T N F, P 2: HE EW Rontiers ARTzarozeNo ratings yet

- Design of LNA Using On-Chip Inductor For Ku-Band ApplicationDocument5 pagesDesign of LNA Using On-Chip Inductor For Ku-Band ApplicationPranjal JalanNo ratings yet

- MegaBrute Leafcutter Mods 03 PDFDocument6 pagesMegaBrute Leafcutter Mods 03 PDFPierre-FrançoisLacenaireNo ratings yet