Professional Documents

Culture Documents

Byte Pattern Detector

Uploaded by

Bangon KaliCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Byte Pattern Detector

Uploaded by

Bangon KaliCopyright:

Available Formats

Johannah Mae D.

Abestano Four Byte Pattern Detector

// Description: // // // // Detects binary pattern in the input stream which is: 8'h56 8'hAB 8'h89 8'h7F

ECE 195

Finite State Machine Diagram

At IDLE state, if the input is 56, then it FSM moves to STATE 0. However, if input is something else, it remains at IDLE state. At STATE 0, if the input is 56, it remains there, however, if the input is AB it proceeds to STATE 1, if not among both, the FSM goes back to IDLE state. At STATE 1, if the input is 89, then the FSM moves to STATE 2, else if the input is 56 then it goes back to STATE 0, however if the input is not 89 nor 56 then it goes back to IDLE state. At state 2, if the input is 7F, the FSM moves to state 3, else if the input is 56 the FSM moves to STATE 0, otherwise if neither of both, the it goes back to STATE IDLE. At STATE 3, if the input is 56, then the output is 1, and the FSM moves to STATE 0. However, if the input is something else, then the output is still 1 but the FSM moves to STATE IDLE. This completes the cycle of the FSM Machine. 1 of 11

Wave Form Views

2 of 11

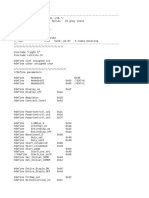

Source Code BytePattern_detector_tb.V

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: MSU-IIT // Engineer: Johannah Mae D. Abestano // // Create Date: 07:37:37 02/01/2013 // Design Name: // Module Name: BytePattern_detector_tb // Project Name: BytePattern_detector // Target Devices: Any // Tool versions: Any // Description: Detects binary pattern in the input stream which is: // 8'h56 // 8'hAB // 8'h89 // 8'h7F // // Test bench with embedded stimulus. // Dependencies: N/A // // Revision: 0001 // Revision 0.01 - File Created // Additional Comments: N/A // ////////////////////////////////////////////////////////////////////////////////// module BytePattern_detector_tb; // Inputs reg clk; reg[7:0] stream; reg rst; reg enable; // Outputs wire detected; // Instantiate the Unit Under Test (UUT) BytePattern_detector uut ( .clk(clk), .stream(stream), .rst(rst), .enable(enable), .detected(detected) ); initial begin // Initialize Inputs clk = 0; stream = 0; // since the enable variable is 0, then the device is in the off state. rst = 1; enable = 0; // Wait 4 ns for global rst to finish #4; // turn on the device. enable = 1; rst = 0; #1; // at 2 units time interval, input these stream values. // OUT #2 stream = 8'hAA; #2 stream = 8'hBB; #2 stream = 8'hCC; #2 stream = 8'hDD; // 0

3 of 11

#2 #2 #2 #2

stream stream stream stream

= = = =

8'h56; 8'hAE; 8'hAA; 8'h56;

#2 #2 #2 #2

stream stream stream stream

= = = =

8'hAB; 8'h11; 8'hBB; 8'hAB;

#2 #2 #2 #2

stream stream stream stream

= = = =

8'h89; 8'h22; 8'hCC; 8'h89;

#2 #2 #2 #2

stream stream stream stream

= = = =

8'h7F; 8'hD3; 8'hDD; 8'h7F;

// // // //

1 0 0 1

#2 stream = 8'hAE; #2 stream = 8'hAE; enable = 0; rst = 1; #2 stream = 8'hAE; #2 stream = 8'h11; #2 stream = 8'h22; #2 stream = 8'hD3; // 0 #2 stream = 8'h56; #2 stream = 8'hAB; #2 stream = 8'h89; #2 stream = 8'h7F; // 1 enable = 1; rst = 0; #2 stream = 8'h56; #2 stream = 8'hAB; #2 stream = 8'h89; #2 stream = 8'h7F; // 1 #2 stream = 8'hAE; #2 stream = 8'h11; #2 stream = 8'h22; #2 stream = 8'hD3; // 0 #2 stream = 8'hAA; #2 stream = 8'hBB; #2 stream = 8'hCC; #2 stream = 8'hDD; // 0 $finish; end // this block of code provides clock frequency for the device. always begin #1 clk = !clk; end endmodule

4 of 11

Source Code BytePattern_detector.V

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: MSU-IIT // Student: Johannah Mae D. Abestano // // Create Date: 07:37:37 02/01/2013 // Design Name: // Module Name: BytePattern_detector // Project Name: BytePattern_detector // Target Devices: Any // Tool versions: Any // Description: Detects binary pattern in the input stream which is: // 8'h56 // 8'hAB // 8'h89 // 8'h7F // Dependencies: N/A // // Revision: 0001 // Revision 0.01 - File Created // Additional Comments: N/A // ////////////////////////////////////////////////////////////////////////////////// module BytePattern_detector( clk, stream, rst, enable, detected ); input clk; input stream; input rst; input enable; output detected; // parameter settings for the current states. parameter SS_IDLE = 5'b00001; parameter STATE_0 = 5'b00010; parameter STATE_1 = 5'b00100; parameter STATE_2 = 5'b01000; parameter STATE_3 = 5'b10000; // paramter settings for the pattern of the input byte stream that must // be detected. parameter PATTERN_0 = 8'h56; parameter PATTERN_1 = 8'hAB; parameter PATTERN_2 = 8'h89; parameter PATTERN_3 = 8'h7F; // this is the input stream. declared as an 8bit wire. wire[7:0] stream; // this is the current state INTERNAL variable. This stores the current state // of the finite state machine. reg[4:0] state;

5 of 11

reg[4:0] nxt_state; assign detected = ((state==STATE_3 && nxt_state==SS_IDLE) || (state==STATE_3 && nxt_state==STATE_0)); // the code that follows is heavily based on the finite state machine diagram // in the documentation of this project. please refer to the diagram and its // following discussion on its operation. always@(posedge clk or negedge rst)begin if (rst) begin state <= SS_IDLE; end else begin state <= nxt_state; end end always @(stream) begin if (enable) begin case (state) SS_IDLE: if (stream == PATTERN_0) begin nxt_state = STATE_0; end else begin nxt_state = SS_IDLE; end STATE_0: if (stream == PATTERN_1) begin nxt_state = STATE_1; end else if (stream != PATTERN_0) begin nxt_state = SS_IDLE; end else begin nxt_state = STATE_0; end STATE_1: if (stream == PATTERN_2) begin nxt_state = STATE_2; end else if (stream != PATTERN_0) begin nxt_state = SS_IDLE; end else begin nxt_state = STATE_0; end STATE_2: if (stream == PATTERN_3) begin nxt_state = STATE_3; end else if (stream != PATTERN_0) begin nxt_state = SS_IDLE; end else begin nxt_state = STATE_0; end STATE_3: if (stream == PATTERN_0) begin nxt_state <= STATE_0; end else begin nxt_state <= SS_IDLE; end

6 of 11

default: nxt_state <= SS_IDLE; endcase end else begin state = SS_IDLE; nxt_state <= SS_IDLE; end end endmodule

7 of 11

Wave View using Memory File

In this simulation the test bench receives data from an external memory file containing testbench data.

8 of 11

Source Code BytePatternDetector_tb_mem.V

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 15:16:16 02/08/2013 // Design Name: BytePattern_detector // Module Name: C:/Users/Bangonkali/Downloads/BytePattern_detector/BytePattern_detector/BytePattern_detec tor_tb_mem.v // Project Name: BytePattern_detector // Target Device: // Tool versions: // Description: // // Verilog Test Fixture created by ISE for module: BytePattern_detector // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // //////////////////////////////////////////////////////////////////////////////// module BytePattern_detector_tb_mem; // Inputs reg clk; reg [7:0] stream; reg rst; reg enable; // Memory Blocks. Instantiate a memory space 8 bits wide and 92 // entries tall. reg [7:0] memory [92:0]; // the variable holding the number of memory entries to read from // an external file. integer mem_max; // a variable holding the current address of the memory being // pushed to the stream input. integer counter; // Outputs wire detected; // Instantiate the Unit Under Test (UUT) BytePattern_detector uut ( .clk(clk), .stream(stream), .rst(rst), .enable(enable), .detected(detected) ); initial begin

9 of 11

// Initialize number of memory locations to read from memory.mem mem_max = 50; // make sure the initial memory iterator is set to 0. this is the // beginning address. counter = 0; // instantiate the reading of the memory and store data to memory // variable. $readmemh("memory.mem", memory, 0, mem_max); // Initialize Inputs clk = 0; stream = 0; rst = 1; enable = 0; // Wait 3 ns for global rst to finish #3; // turn on the device by setting enable to high and reset to low. enable = 1; rst = 0; // loop at each memory location. then at each address push value to stream at 2 time // units interval. for (counter = 0; counter < mem_max; counter = counter + 1) begin #2 stream = memory[counter]; end $finish; end // block of code provides clock source for the device under test. always begin #1 clk = !clk; end endmodule

10 of 11

Source Code memory.mem AA 56 AB 89 7F AA 56 AB 89 7F 56 AB 89 7F 11 22 33 44 55 66 77 77 88 99 01 02 03 AA 56 AB 89 7F AA 56 AB 89 7F 56 AB 89 7F 11 22 33 44 55 66 77

11 of 11

You might also like

- Johannah Mae D. Abestano ECE 195 Binary Pattern Detector Finite State Machine Finite State DiagramDocument5 pagesJohannah Mae D. Abestano ECE 195 Binary Pattern Detector Finite State Machine Finite State DiagramBangon KaliNo ratings yet

- Bantam Earth Paludarium CodeDocument75 pagesBantam Earth Paludarium CodeBantam EarthNo ratings yet

- Spi Protocol Verilog Code ExplanationDocument15 pagesSpi Protocol Verilog Code Explanationgokul pNo ratings yet

- Arduino Pellet Boiler Data Logger v1 My Nerd StuffDocument36 pagesArduino Pellet Boiler Data Logger v1 My Nerd StuffmyEbooks0% (1)

- Led 123 DesimalDocument4 pagesLed 123 DesimalAmrie Abenq100% (1)

- UART Serial Communication GuideDocument6 pagesUART Serial Communication GuideteekamNo ratings yet

- VerilogDocument22 pagesVerilogSyurga FathonahNo ratings yet

- UART (Verilog Code) With FSMDocument24 pagesUART (Verilog Code) With FSMसौरभ शुक्ला0% (1)

- Keyboard - C: Programa en C USB PIC18FDocument11 pagesKeyboard - C: Programa en C USB PIC18FLuis GonzalesNo ratings yet

- EkrannDocument6 pagesEkrannBubbleNo ratings yet

- Asynchronous FIFODocument3 pagesAsynchronous FIFORoshan KumarNo ratings yet

- ERC16064-1 DemoCode 4 Wire SPIDocument19 pagesERC16064-1 DemoCode 4 Wire SPIDVTNo ratings yet

- Digital Design and Synthesis: Fall 09Document35 pagesDigital Design and Synthesis: Fall 09Lua Dinh ThiNo ratings yet

- Opamp CodeDocument22 pagesOpamp Codeapi-531846547No ratings yet

- Elevator Programming CodeDocument178 pagesElevator Programming Code100mphNo ratings yet

- File: F:/HARDWARE/Program Robot Manual 2011/manual 08-01-1011/SIC/manual/manual.c Date: 1/9/2011Document3 pagesFile: F:/HARDWARE/Program Robot Manual 2011/manual 08-01-1011/SIC/manual/manual.c Date: 1/9/2011Faizal Nur KarimNo ratings yet

- Sample Code For SHT21: Supporting Communication SoftwareDocument14 pagesSample Code For SHT21: Supporting Communication SoftwareMaiDungNo ratings yet

- Gyroscope LED Controller STM32F407 DiscoveryDocument21 pagesGyroscope LED Controller STM32F407 DiscoveryAndrei GeorgeNo ratings yet

- Cpu - Timer0 - Isr Initxintf: #Include "Dsp28X - Project.H"Document3 pagesCpu - Timer0 - Isr Initxintf: #Include "Dsp28X - Project.H"RajendraNo ratings yet

- UartDocument18 pagesUartapi-552271981No ratings yet

- LinefollowingsmDocument8 pagesLinefollowingsmapi-398062839No ratings yet

- H 1Document7 pagesH 1nilton_9365611No ratings yet

- ScriptDocument5 pagesScriptSilviuDragomirNo ratings yet

- Task and FunctionDocument6 pagesTask and FunctionsatheeshNo ratings yet

- Main Program MonitoringDocument10 pagesMain Program MonitoringBagus NugrohoNo ratings yet

- Lab 7Document6 pagesLab 7kenerkivah100% (1)

- Main CDocument10 pagesMain CTarcísio Souza de MeloNo ratings yet

- SpihsmDocument26 pagesSpihsmapi-438120791No ratings yet

- GamesmDocument12 pagesGamesmapi-438010548No ratings yet

- Analog ShieldDocument16 pagesAnalog ShieldTrung Manh HuynhNo ratings yet

- Test Verification GuideDocument7 pagesTest Verification GuideArchana KoreNo ratings yet

- Pic 18f452 Implementation of Digital FiltersDocument5 pagesPic 18f452 Implementation of Digital FiltersishakubalamiNo ratings yet

- Verilog FSM Design and ImplementationDocument8 pagesVerilog FSM Design and ImplementationEr Pradip PatelNo ratings yet

- CodigoDocument8 pagesCodigoGonzalo MoralesNo ratings yet

- Stepper Acceleration FreertosDocument9 pagesStepper Acceleration FreertosSourabh KumawatNo ratings yet

- Wifi Module Interfacing With AVRDocument33 pagesWifi Module Interfacing With AVRMH 108812No ratings yet

- Top Module / Module DPLL (SignalIn, SignalOutDocument10 pagesTop Module / Module DPLL (SignalIn, SignalOutbigjimmNo ratings yet

- Arduino 28BYj-48 Stepper Motor ControlDocument3 pagesArduino 28BYj-48 Stepper Motor ControlRejaul KarimNo ratings yet

- File: D:/Automation/oz8/ozonend.c, Date: 7/28/2011, Time: 4:20:33 PMDocument20 pagesFile: D:/Automation/oz8/ozonend.c, Date: 7/28/2011, Time: 4:20:33 PMPhan Truong HaiNo ratings yet

- Calling Demantra Workflow Using HTTP POSTDocument11 pagesCalling Demantra Workflow Using HTTP POSTKanchana SriramuluNo ratings yet

- AT89S52Document9 pagesAT89S52Aarthi GurunathanNo ratings yet

- A Division of Labor: B.1 Test Labkit.vDocument31 pagesA Division of Labor: B.1 Test Labkit.vraymar2kNo ratings yet

- Sequential Circuits and Seven Segment Display: Lab Assignment 10Document7 pagesSequential Circuits and Seven Segment Display: Lab Assignment 10Ahmed UzairNo ratings yet

- Programa SPI MestreDocument5 pagesPrograma SPI MestreAlan Robson100% (1)

- UART Communication GuideDocument22 pagesUART Communication GuideanjalisweNo ratings yet

- The Ultrasonic SensorDocument14 pagesThe Ultrasonic SensorAdalberto Sharpley100% (1)

- LLI RttTimer.VDocument4 pagesLLI RttTimer.Vkumarsanjeev.net9511No ratings yet

- UARTDocument9 pagesUARTBrainz on MobNo ratings yet

- TRIAC control with potentiometer tutorialDocument2 pagesTRIAC control with potentiometer tutorialJavier GuerreroNo ratings yet

- SHT1x and SHT7x Sample Code: Humidity & Temperature SensorDocument7 pagesSHT1x and SHT7x Sample Code: Humidity & Temperature Sensorer_gaurav_iceNo ratings yet

- MainDocument8 pagesMainEvelina JimenezNo ratings yet

- Verilog ReferenceDocument77 pagesVerilog ReferencePRANJAL SHRIVASTAVANo ratings yet

- EE312 Experiment 07: Objective 1Document18 pagesEE312 Experiment 07: Objective 1SAURABH RAJNo ratings yet

- Whatsapp Bloker and Haking Tool KitDocument2,359 pagesWhatsapp Bloker and Haking Tool KitAaditya KhannaNo ratings yet

- LSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 3 - DelayDocument8 pagesLSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 3 - DelayMerupu DebbaNo ratings yet

- Tester Code v1.1.08Document102 pagesTester Code v1.1.08Afrastt GasargeserNo ratings yet

- 12F683Document10 pages12F683Sanel LerićNo ratings yet

- TtaDocument5 pagesTtahenrikemateus1No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- ECE 195 Analog Electronics - Lab 03Document17 pagesECE 195 Analog Electronics - Lab 03Bangon KaliNo ratings yet

- Ultrasonic Distance SensorDocument1 pageUltrasonic Distance SensorBangon KaliNo ratings yet

- Satellite CommunicationsDocument77 pagesSatellite CommunicationsBangon KaliNo ratings yet

- Siemens Manual For PLC S7 300 and 400 ProgrammingDocument228 pagesSiemens Manual For PLC S7 300 and 400 ProgrammingBangon Kali100% (1)

- Information Retrieval Data Structures & Algorithms - William B. FrakesDocument630 pagesInformation Retrieval Data Structures & Algorithms - William B. FrakesHugoEnriqueNo ratings yet

- Video Sync GeneratorDocument6 pagesVideo Sync GeneratorBangon KaliNo ratings yet

- Verilog Binary Pattern Recognizer Finite State Machine ApplicationDocument5 pagesVerilog Binary Pattern Recognizer Finite State Machine ApplicationBangon KaliNo ratings yet

- Basic CVSLDocument5 pagesBasic CVSLBangon KaliNo ratings yet

- Verilog: A Simple UpDown Counter ImplemntationDocument4 pagesVerilog: A Simple UpDown Counter ImplemntationBangon KaliNo ratings yet

- Garbage Collection Algorithms For Automatic Dynamic Memory Management - Richard Jones PDFDocument203 pagesGarbage Collection Algorithms For Automatic Dynamic Memory Management - Richard Jones PDFBangon KaliNo ratings yet

- The Design and Analysis of Spatial Data Structures - Hanan Samet PDFDocument499 pagesThe Design and Analysis of Spatial Data Structures - Hanan Samet PDFBangon KaliNo ratings yet

- Trig Identities: sin2+cos2=1, sin(A+B), cos(A+BDocument3 pagesTrig Identities: sin2+cos2=1, sin(A+B), cos(A+Bvas_grNo ratings yet

- JMDADocument4 pagesJMDABangon KaliNo ratings yet

- Fundamentals of OOP and Data Structures in Java 2001Document508 pagesFundamentals of OOP and Data Structures in Java 2001anon-756859100% (1)

- ES 81exer4Document1 pageES 81exer4Bangon KaliNo ratings yet

- Managed DirectX 9 Kick Start - Graphics and Game ProgrammingDocument364 pagesManaged DirectX 9 Kick Start - Graphics and Game ProgrammingHitMAN010No ratings yet

- GMERDocument6 pagesGMERBangon KaliNo ratings yet

- An 7810Document10 pagesAn 7810Serch N RodriguezNo ratings yet

- Johannah Ece120Document5 pagesJohannah Ece120Bangon KaliNo ratings yet

- Datasheet 78xxxDocument16 pagesDatasheet 78xxxrikejiNo ratings yet

- Johannah Ece120Document5 pagesJohannah Ece120Bangon KaliNo ratings yet

- Load Curtailment Mar 1 - 31, 2012Document1 pageLoad Curtailment Mar 1 - 31, 2012Bangon KaliNo ratings yet

- Load Curtailment Mar 1 - 31, 2012Document1 pageLoad Curtailment Mar 1 - 31, 2012Bangon KaliNo ratings yet

- Laplace Transform Solution of ODEsDocument2 pagesLaplace Transform Solution of ODEsbedodsonNo ratings yet

- Crack ORCAD 16.3 for Windows 7 in Less Than 40 StepsDocument1 pageCrack ORCAD 16.3 for Windows 7 in Less Than 40 StepsBangon KaliNo ratings yet

- An 7810Document10 pagesAn 7810Serch N RodriguezNo ratings yet

- Practical Artificial Intelligence Programming in JavaDocument157 pagesPractical Artificial Intelligence Programming in JavaBruno SilvaNo ratings yet

- By LocationDocument54 pagesBy LocationBangon KaliNo ratings yet

- CCCCCCCCCCCCCCCCCCCCCCCCCCC: Simulation of Data StructuresDocument27 pagesCCCCCCCCCCCCCCCCCCCCCCCCCCC: Simulation of Data Structuresram242No ratings yet

- XLR UserDemoDocument27 pagesXLR UserDemoSobhy GendykhelaNo ratings yet

- KX-TES824 or KX-TA824 PC Programming Manual Up To Page 47 Out of 164Document47 pagesKX-TES824 or KX-TA824 PC Programming Manual Up To Page 47 Out of 164Lucas CoaquiraNo ratings yet

- Advant Controller 450 Product GuideDocument120 pagesAdvant Controller 450 Product Guidejulio_hanif100% (1)

- Bracketing Paradoxes in Italian (Daniele Virgillito, Università Di Bologna 2010)Document97 pagesBracketing Paradoxes in Italian (Daniele Virgillito, Università Di Bologna 2010)danielevirgillitoNo ratings yet

- BacktrackingDocument301 pagesBacktrackingDinesh Reddy Kommera100% (1)

- C6 & N97 Bazaraa CFW v IV ported with new features & fixesDocument7 pagesC6 & N97 Bazaraa CFW v IV ported with new features & fixesnarenczNo ratings yet

- PDF 9532Document158 pagesPDF 9532NenoNo ratings yet

- Video Encryption and Decryption Techniques ComparedDocument6 pagesVideo Encryption and Decryption Techniques ComparedKrishnamoorthy KumarNo ratings yet

- CV Manish IPDocument4 pagesCV Manish IPManish KumarNo ratings yet

- Open Source For You 2016Document108 pagesOpen Source For You 2016Eduardo Farías ReyesNo ratings yet

- How To Build A PIC16F84 Servo ControllerDocument5 pagesHow To Build A PIC16F84 Servo ControllerCảnh ManuNo ratings yet

- MIT6 0002F16 ProblemSet5Document13 pagesMIT6 0002F16 ProblemSet5DevendraReddyPoreddyNo ratings yet

- Upe CFX Config CommonDocument105 pagesUpe CFX Config Commonthatipamula sudhakarNo ratings yet

- 4 SOC ConsultingDocument54 pages4 SOC Consultingriadelidrissi100% (3)

- Django Model ReportDocument13 pagesDjango Model ReportWalter Angolar Da SilvaNo ratings yet

- Orcad PLDDocument8 pagesOrcad PLDmeeduma4582No ratings yet

- Benefits of Gantt ChartDocument4 pagesBenefits of Gantt ChartRavi KaniyawalaNo ratings yet

- Master Data Governance (MDG) Application Programming Interface (API) GuideDocument28 pagesMaster Data Governance (MDG) Application Programming Interface (API) Guidebandistechnology100% (3)

- AnswerDocument2 pagesAnswerkartikey jainNo ratings yet

- WaltographDocument3 pagesWaltographapi-26866651No ratings yet

- Chapter 9Document6 pagesChapter 9Talha Bin SaeedNo ratings yet

- Estimation and Detection Theory by Don H. JohnsonDocument214 pagesEstimation and Detection Theory by Don H. JohnsonPraveen Chandran C RNo ratings yet

- 1 Constrained Optimization: 1.1 Structure of The ProblemDocument4 pages1 Constrained Optimization: 1.1 Structure of The ProblemSam SmrdaNo ratings yet

- CPF Methodology PDFDocument395 pagesCPF Methodology PDFkishore kumar kota100% (2)

- Ipc/jedec 9703Document46 pagesIpc/jedec 9703metaballinNo ratings yet

- TSM4VE PresentationDocument34 pagesTSM4VE Presentationidu ipv6No ratings yet

- Actual Stored Procedure CodeDocument7 pagesActual Stored Procedure CodeJason HallNo ratings yet

- Practical Internet of Things With JavaScript - Build Standalone Exciting IoT Projects With Raspberry Pi 3 and JavaScriptDocument291 pagesPractical Internet of Things With JavaScript - Build Standalone Exciting IoT Projects With Raspberry Pi 3 and JavaScriptPaulo Rodrigues de LimaNo ratings yet

- Biorisk ManagementDocument11 pagesBiorisk ManagementJohn Marie IdavaNo ratings yet