Professional Documents

Culture Documents

Datasheet Fairchild UC3843

Uploaded by

Tina JohnsonOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet Fairchild UC3843

Uploaded by

Tina JohnsonCopyright:

Available Formats

www.fairchildsemi.

com

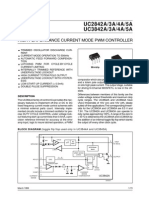

UC3842/UC3843/UC3844/UC3845

SMPS Controller

Features

Low Start up Current Maximum Duty Clamp UVLO With Hysteresis Operating Frequency up to 500KHz

Description

The UC3842/UC3843/UC3844/UC3845 are fixed frequencycurrent-mode PWM controller. They are specially designed for Off-Line and DC to DC converter applications with minimum external components. These integrated circuits feature a trimmed oscillator for precise duty cycle control, a temperature compensated reference, high gain error amplifier, current sensing comparator and a high current totempole output for driving a Power MOSFET. The UC3842 and UC3844 have UVLO thresholds of 16V (on) and 10V (off). The UC3843 and UC3845 are 8.5V(on) and 7.9V (off). The UC3842 and UC3843 can operate within 100% duty cycle. The UC3844 and UC3845 can operate with 50% duty cycle.

8-DIP 8-SOP

14-SOP

Internal Block Diagram

* NORMALLY 8DIP/8SOP PIN NO. * ( ) IS 14SOP PINNO. * TOGGLE FLIP FLOP USED ONLY IN UC3844, UC3845

Rev. 1.0.1

2002 Fairchild Semiconductor Corporation

UC3842/UC3843/UC3844/UC3845

Absolute Maximum Ratings

Parameter Supply Voltage Output Current Analog Inputs (Pin 2.3) Error Amp Output Sink Current Power Dissipation at TA25C (8DIP) Power Dissipation at TA25C (8SOP) Power Dissipation at TA25C (14SOP) Storage Temperature Range Lead Temperature (Soldering, 10sec) Symbol VCC IO V(ANA) ISINK (E.A) PD(Note1,2) PD(Note1,2) PD(Note1,2) TSTG TLEAD Value 30 1 -0.3 to 6.3 10 1200 460 680 -65 ~ +150 +300 Unit V A V mA mW mW mW C C

Note: 1. Board Thickness 1.6mm, Board Dimension 76.2mm 114.3mm, (Reference EIA / JSED51-3, 51-7) 2. Do not exceeed PD and SOA (Safe Operation Area)

Power Dissipation Curve

1200 8DIP 1100 POWER DISSIPATION (mW) 1000 900 800 700 600 500 400 300

0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150

14SOP

8SOP

AMBIENT TEMPERATURE ()

Thermal Data

Characteristic Thermal Resistance Junction-ambient Symbol Rthj-amb(MAX) 8-DIP 100 8-SOP 265 14-SOP 180 Unit C/W

Pin Array

8DIP,8SOP 14SOP

COMP 1

VREF

COMP 1

14 VREF

VFB 2

VCC

N/C

13

N/C

CURRENT SENSE

OUTPUT

VFB 3

12

VCC

RT/ CT 4

5 GND

N/C 4

11 PWR VC

CURRENT SENSE

10 OUTPUT

N/C

GND

RT/C T 7

PWR GND

UC3842/UC3843/UC3844/UC3845

Electrical Characteristics

(VCC=15V, RT=10k, CT=3.3nF, TA= 0C to +70C, unless otherwise specified) Parameter REFERENCE SECTION Reference Output Voltage Line Regulation Load Regulation Short Circuit Output Current OSCILLATOR SECTION Oscillation Frequency Frequency Change with Voltage Oscillator Amplitude ERROR AMPLIFIER SECTION Input Bias Current Input Voltage Open Loop Voltage Gain Power Supply Rejection Ratio Output Sink Current Output Source Current High Output Voltage Low Output Voltage CURRENT SENSE SECTION Gain Maximum Input Signal Power Supply Rejection Ratio Input Bias Current OUTPUT SECTION Low Output Voltage High Output Voltage Rise Time Fall Time Start Threshold Min. Operating Voltage (After Turn On) VOL ISINK = 20mA ISINK = 200mA VOH tR tF ISOURCE = 20mA ISOURCE = 200mA TJ = 25C, CL= 1nF (Note 3) TJ = 25C, CL= 1nF (Note 3) UC3842/UC3844 UC3843/UC3845 UC3842/UC3844 UC3843/UC3844 13 12 14.5 7.8 8.5 7.0 0.08 1.4 13.5 13.0 45 35 16.0 8.4 10.0 7.6 0.4 2.2 150 150 17.5 9.0 11.5 8.2 V V V V ns ns V V V V GV VI(MAX) PSRR IBIAS (Note 1 & 2) Vpin1 = 5V(Note 1) 12V VCC 25V (Note 1,3) 2.85 0.9 3 1 70 -3 3.15 1.1 -10 V/V V dB A IBIAS VI(E>A) GVO PSRR ISINK ISOURCE VOH VOL Vpin1 = 2.5V 2V VO 4V (Note3) 12V VCC 25V (Note3) Vpin2 = 2.7V, Vpin1 = 1.1V Vpin2 = 2.3V, Vpin1 = 5V Vpin2 = 2.3V, RL = 15k to GND Vpin2 = 2.7V, RL = 15k to Pin 8 2.42 65 60 2 -0.6 5 -0.1 2.50 90 70 7 -1.0 6 0.8 -2 2.58 1.1 A V dB dB mA mA V V f f/VCC VOSC TJ = 25C 12V VCC 25V 47 52 0.05 1.6 57 1 kHz % VP-P VREF VREF VREF ISC TJ = 25C, IREF = 1mA 12V VCC 25V 1mA IREF 20mA TA = 25C 4.90 5.00 6 6 -100 5.10 20 25 -180 V mV mV mA Symbol Conditions Min. Typ. Max. Unit

UNDER-VOLTAGE LOCKOUT SECTION VTH(ST) VOPR(MIN)

UC3842/UC3843/UC3844/UC3845

Electrical Characteristics (Continued)

(VCC=15V, RT=10k, CT=3.3nF, TA= 0C to +70C, unless otherwise specified) Parameter PWM SECTION Max. Duty Cycle Min. Duty Cycle TOTAL STANDBY CURRENT Start-Up Current Operating Supply Current Zener Voltage IST ICC(OPR) VZ ICC = 25mA Vpin3=Vpin2=ON 30 0.45 14 38 1 17 mA mA V D(Max) D(Max) D(MIN) UC3842/UC3843 UC3844/UC3845 95 47 97 48 100 50 0 % % % Symbol Conditions Min. Typ. Max. Unit

Adjust VCC above the start threshould before setting at 15V

Note: 1. Parameter measured at trip point of latch 2. Gain defined as: V pin1 A = ----------------- ,0 Vpin3 0.8V V pin3 3. These parameters, although guaranteed, are not 100 tested in production.

UC3842

Figure 1. Open Loop Test Circuit

High peak currents associated with capacitive loads necessitate careful grounding techniques Timing and bypass capacitors should be connected close to pin 5 in a single point ground. The transistor and 5k potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

UC3842/UC3843/UC3844/UC3845

UC3842/44 UC3843/45

Figure 2. Under Voltage Lockout

During Under-Voltage Lock-Out, the output driver is biased to a high impedance state. Pin 6 should be shunted to ground with a bleeder resistor to prevent activating the power switch with output leakage current.

Figure 3. Error Amp Configuration

Figure 4. Current Sense Circuit

Peak current (IS) is determined by the formula:

1.0V I S ( MAX ) = ----------RS

A small RC filter may be required to suppress switch transients.

UC3842/UC3843/UC3844/UC3845

Figure 5. Oscillator Waveforms and Maximum Duty Cycle

Oscillator timing capacitor, CT, is charged by VREF through RT and discharged by an internal current source. During the discharge time, the internal clock signal blanks the output to the low state. Selection of RT and CT therefore determines both oscillator frequency and maximum duty cycle. Charge and discharge times are determined by the formulas: tc = 0.55 RT CT

0.0063RT 2.7 t D = R T C T I n --------------------------------------- 0.0063R T 4

Frequency, then, is: f=(tc + td)-1

1.8 ForRT > 5K ,f = -------------RT CT

Figure 6. Oscillator Dead Time & Frequency

Figure 7. Timing Resistance vs Frequency

(Deadtime vs CT RT > 5k)

Figure 8. Shutdown Techniques

UC3842/UC3843/UC3844/UC3845

Shutdown of the UC3842 can be accomplished by two methods; either raise pin 3 above 1V or pull pin 1 below a voltage two diode drops above ground. Either method causes the output of the PWM comparator to be high (refer to block diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at pins 1 and/or 3 is removed. In one example, an externally latched shutdown may be accomplished by adding an SCR which will be reset by cycling VCC below the lower UVLO threshold. At this point the reference turns off, allowing the SCR to reset.

UC3842/UC3843

Figure 9. Slope Compensation

A fraction of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for converters requiring duty cycles over 50%. Note that capacitor, CT, forms a filter with R2 to suppress the leading edge switch spikes.

Temperature (C) Figure 10. Temperature Drift (Vref)

Temperature (C) Figure 11. Temperature Drift (Ist)

Temperature (C) Figure 12. Temperature Drift (Icc)

You might also like

- UC3845Document13 pagesUC3845roozbehxoxNo ratings yet

- UC3843 DatasheetDocument13 pagesUC3843 DatasheetBigbrain99No ratings yet

- Uc284xa Uc384xaDocument16 pagesUc284xa Uc384xayusufwpNo ratings yet

- UC3845ANDocument15 pagesUC3845ANMiloud ChouguiNo ratings yet

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocument16 pagesUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaNo ratings yet

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocument15 pagesUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceNo ratings yet

- Uc3842 Monitor Power Supply Regulator IcDocument7 pagesUc3842 Monitor Power Supply Regulator IcJoseph Sidhom SnadaNo ratings yet

- Current Mode PWM Controller: Features DescriptionDocument9 pagesCurrent Mode PWM Controller: Features DescriptionJozo ĆurčićNo ratings yet

- 8205Document16 pages8205sonytinNo ratings yet

- Uc3844 DDocument16 pagesUc3844 DankurmalviyaNo ratings yet

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75No ratings yet

- Lm555 555c TimerDocument12 pagesLm555 555c TimerAlexis Orellana VediaNo ratings yet

- Uc3844 DDocument16 pagesUc3844 DFaisalMalikNo ratings yet

- LMC555 CMOS Timer: General Description FeaturesDocument10 pagesLMC555 CMOS Timer: General Description FeaturesJeremy ObriotNo ratings yet

- KA3842BDocument12 pagesKA3842BLucio Sortija LuqueNo ratings yet

- IC 3842 para FonteDocument8 pagesIC 3842 para FonteTomNedscNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- LM555 Timer: General Description FeaturesDocument12 pagesLM555 Timer: General Description FeaturesMark J A. OkyoNo ratings yet

- Mc1455-d Timer IcDocument11 pagesMc1455-d Timer IcDecker JamesNo ratings yet

- LM555 Timer: Literature Number: SNAS548BDocument14 pagesLM555 Timer: Literature Number: SNAS548BKenly WallNo ratings yet

- SG3524 SMPS Control Circuit: Description Pin ConfigurationDocument5 pagesSG3524 SMPS Control Circuit: Description Pin ConfigurationNiko OlnicasaNo ratings yet

- MC1648 DataSheetDocument11 pagesMC1648 DataSheetKWojtekNo ratings yet

- MC34063AMDocument16 pagesMC34063AMSajjad4434No ratings yet

- LMC555 CMOS Timer: General Description FeaturesDocument12 pagesLMC555 CMOS Timer: General Description FeaturesNicolas FontanaNo ratings yet

- MC34063ADocument15 pagesMC34063AAlfredo Valencia RodriguezNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- MC1455Document13 pagesMC1455eduardolsNo ratings yet

- Isolated Flyback Switching Regulator W - 9V OutputDocument16 pagesIsolated Flyback Switching Regulator W - 9V OutputCasey DialNo ratings yet

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocument13 pagesMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorszocanNo ratings yet

- CA3059, CA3079: Description FeaturesDocument12 pagesCA3059, CA3079: Description FeaturesMiltongrimi GrimilNo ratings yet

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesDocument12 pagesPrecision Waveform Generator/Voltage Controlled Oscillator FeaturesCharles Tineo0% (1)

- S Feature D Escriptio: LTC1261 Switched Capacitor Regulated Voltage InverterDocument16 pagesS Feature D Escriptio: LTC1261 Switched Capacitor Regulated Voltage InverterFer CurtinoNo ratings yet

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNo ratings yet

- DatasheetDocument9 pagesDatasheetnipunkhatriNo ratings yet

- Thb7128 InstructionsDocument9 pagesThb7128 InstructionsanhxcoNo ratings yet

- Fan 7314Document14 pagesFan 7314Kamal NonekNo ratings yet

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocument14 pagesMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsVũ TưởngNo ratings yet

- AZ3842 PWM Controller Data Sheet SummaryDocument13 pagesAZ3842 PWM Controller Data Sheet SummaryEngr Khalid IqbalNo ratings yet

- Data SheetDocument14 pagesData SheetGavril GiurgiNo ratings yet

- lm555 DatasheetDocument11 pageslm555 DatasheetKhu GhingNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- 2SB688Document2 pages2SB688Porfirio J Gutierrez100% (1)

- 1.1.1.1 Video Explanation - What Is in A ComputerDocument2 pages1.1.1.1 Video Explanation - What Is in A ComputerZesorith ThunderNo ratings yet

- Amazon Kindle - WikipediaDocument54 pagesAmazon Kindle - WikipediaSubham SahuNo ratings yet

- S+ I/O: HAI805 & HAO805 HART I/O: Symphony PlusDocument4 pagesS+ I/O: HAI805 & HAO805 HART I/O: Symphony PlusMD. AL MUZAHIDNo ratings yet

- Instruction Manual: YokogawaDocument200 pagesInstruction Manual: YokogawaRaj yadavNo ratings yet

- Keystation 49: 49-Key Mobile USB MIDI ControllerDocument1 pageKeystation 49: 49-Key Mobile USB MIDI ControllerAlf MegsonNo ratings yet

- Xbox One Fat SchematicDocument72 pagesXbox One Fat Schematicstyle games100% (5)

- TCL 2 2015.00 LG 04Document8 pagesTCL 2 2015.00 LG 04kehrenNo ratings yet

- Circuit Diagram 43''Document12 pagesCircuit Diagram 43''Jorge Humberto DuqueNo ratings yet

- Python Interface Development User ManualDocument80 pagesPython Interface Development User ManualJordi Jardi BenedictoNo ratings yet

- Qoriq: Qoriq / Kɔ Raɪkju / Is A Brand of Arm-Based and Power Isa-BasedDocument9 pagesQoriq: Qoriq / Kɔ Raɪkju / Is A Brand of Arm-Based and Power Isa-BasedParasaram SrinivasNo ratings yet

- Algorithms and Data Structures Reader1Document85 pagesAlgorithms and Data Structures Reader1Aleksander JastrzębskiNo ratings yet

- LG 1511S Color Monitor Service ManualDocument28 pagesLG 1511S Color Monitor Service ManualJose AlbertoNo ratings yet

- Lionbridge-WP MobileApps2 PDFDocument13 pagesLionbridge-WP MobileApps2 PDFDuy Anh MilanoNo ratings yet

- Preparation Handbook for Azure FundamentalsDocument137 pagesPreparation Handbook for Azure FundamentalsPoojaShukla100% (1)

- Access Standalone and ReadersDocument14 pagesAccess Standalone and ReadersCatalin BailescuNo ratings yet

- Adjust parameters for Deep Sea generator control moduleDocument2 pagesAdjust parameters for Deep Sea generator control moduleMaicon KurthNo ratings yet

- NP SocketsDocument70 pagesNP Socketsom18sahuNo ratings yet

- Scheduled ClassicDocument33 pagesScheduled ClassicTu TuNo ratings yet

- 5G New Radio (NR) : Physical Layer Overview and PerformanceDocument5 pages5G New Radio (NR) : Physical Layer Overview and PerformanceHarikrishnaChinthalaboyinaNo ratings yet

- Connectrix Ds-6600B Switches: DS-6600B 32Gb/s Fibre Channel Switch ModelsDocument6 pagesConnectrix Ds-6600B Switches: DS-6600B 32Gb/s Fibre Channel Switch ModelsPinakini MothukuriNo ratings yet

- Download VirtualBox binaries and source codeDocument1 pageDownload VirtualBox binaries and source codeMaxNo ratings yet

- Platform Technologies ReviewerDocument9 pagesPlatform Technologies ReviewerRaissa GonzagaNo ratings yet

- ToadforOracle 115 DBA Suite Installation GuideDocument27 pagesToadforOracle 115 DBA Suite Installation GuideSyahmie RamleyNo ratings yet

- Field Installation Guide v4 - 5Document60 pagesField Installation Guide v4 - 5elcaso34No ratings yet

- RISc 2007 RAMBUS Paper QuestionsDocument4 pagesRISc 2007 RAMBUS Paper Questionsraghu dNo ratings yet

- Project of Electric Circuit Analysis (Eca) : TopicDocument17 pagesProject of Electric Circuit Analysis (Eca) : TopicMuhammad Hamza AminNo ratings yet

- Brkiot 2555Document92 pagesBrkiot 2555Alberto ArellanoNo ratings yet

- Hospital: Free PPT TemplatesDocument14 pagesHospital: Free PPT TemplatesKritika SoniNo ratings yet

- Label - Text Textbox - Name: Server Txtserver Port Txtport Username Txtmysqluser Password Txtmysqlpw Database TXTDBDocument85 pagesLabel - Text Textbox - Name: Server Txtserver Port Txtport Username Txtmysqluser Password Txtmysqlpw Database TXTDBIyengar PrasadNo ratings yet