Professional Documents

Culture Documents

Buses

Uploaded by

Sam RodríguezCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Buses

Uploaded by

Sam RodríguezCopyright:

Available Formats

.1.

BUSES NORMALIZADOS Un bus debe cumplir las siguientes especificaciones: Nivel mecnico En el nivel mecnico deben definirse aspectos tales como el tipo de soporte, el nmero de hilos del bus, el tipo de conector, etc. Por ejemplo, en los buses para la conexin de placas impresas, hay que definir, entre otras cosas, la altura de las placas, los conectores y las posiciones de stos, para garantizar la compatibilidad de las distintas placas. Nivel elctrico El nivel elctrico (u ptico, en el caso de emplear como soporte la fibra ptica), debe especificar el circuito equivalente de los dispositivos que se conectan a las lneas del bus, tanto de los emisores como de los receptores. Tambin debe especificar las tensiones y corrientes utilizadas para establecer el valor de las seales. En este nivel, debe quedar definida la forma en la que los distintos dispositivos deben conectarse elctricamente. Nivel lgico Este nivel define estticamente todas las lneas del bus, estableciendo las equivalencias entre los valores elctricos de las seales y sus valores lgicos. Por ejemplo, se definir que los hilos 0-7 su nivel alto (5V) equivale a un 1 lgico y los hilos 8-15 su nivel activo es a nivel bajo (0V). Nivel de temporizacin bsica En este nivel se establecen los cronogramas para la realizacin de la operacin ms elemental del bus, esto es, de un ciclo. Nivel de transferencia elemental En este nivel se establece el procedimiento empleado para realizar una transferencia de un dato por el bus. En el caso de un bus de ciclo completo, este nivel coincide con el anterior puesto que la temporizacin bsica establece todas las condiciones necesarias para transferir un dato. Sin embargo, en el caso de un bus de ciclo partido, se especifican las ranuras que forman cada tipo de ciclo o transferencia. Nivel de transferencia de bloque En algunos buses, la operacin bsica esta formada por una serie de transferencias elementales, que tiene por objetivo el transferir un bloque de informacin con entidad propia. En este nivel, deber definirse el protocolo de comunicacin empleado para realizar esta transferencia de bloque.

Se definirn aspectos tales como cabeceras, codificacin de los datos para deteccin de errores, procedimientos de recuperacin para el caso de error, identificacin del receptor, etc. [1] [3] 2.2. JERARQUA DE BUSES Por qu es necesaria la jerarqua de buses? Cuando queremos conectar un gran nmero de dispositivos nos encontramos con una serie de problemas fundamentales:

La diferencia de velocidad de los dispositivos afecta negativamente al rendimiento global, ya que mientras los dispositivos lentos realizan una nica transferencia, otro dispositivo ms rpido podra haber realizado muchas ms. Los buses pueden actuar de cuello de botella si la demanda de la transferencia es mayor que la capacidad del bus, los dispositivos debern esperar mucho tiempo para poder transmitir. Existe un mayor retardo de propagacin, dado que el bus ha de tener mayor longitud para poder soporta implementar un mayor nmero de dispositivos

Ventajas de las jerarquas de buses:

El bus local entre el procesador y la cach asla el trfico de E/S del procesador.

Se puede transferir informacin entre la memoria y la E/S sin interrumpir la actividad del procesador.

El bus de expansin reduce el trfico en el bus del sistema.

La transferencia entre cach y memoria principal se pueden realizar de forma ms eficiente.

o

Se pueden realizar una transferencia de memoria cach a memoria principal al mismo tiempo que el interfaz recibe datos desde un dispositivo de E/S El procesador+cach o el coprocesador tienen la misma prioridad en el acceso al bus que todos los dispositivos conectados al bus de expansin de forma conjunta.

Se elimina el problema de la incompatibilidad.

o

El bus local y del sistema suelen ser propietarios (no estndar) y estn optimizados para cada arquitectura particular.

Los buses de expansin son buses estndares o abiertos (ISA, EISA, PCI, VME, etc.).

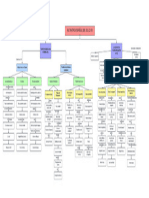

Esto permite tener caractersticas y especificaciones perfectamente definidas, con conectores estndar, podemos utilizar los mismos controladores y perifricos en otro computador que disponga del mismo bus estndar. [4] Figura: 1 Jerarqua de los buses. Buses de tipo 0 Los buses de tipo 0 son los buses internos de las pastillas. La utilizacin de buses internos de gran ancho de palabra unido a la incorporacin de memoria cach interna facilita que se puedan conseguir microprocesadores de grandes prestaciones. Buses de tipo 1 El bus de tipo 1 es el bus de interconexin de componentes de una placa o circuito impreso. Buses de tipo 2 Estos buses sirven para interconectar las distintas placas de un modulo, formando lo que se llama el panel posterior. La prctica totalidad de los computadores actuales se componen de un solo mdulo, por lo que no existe bus de nivel 3 y este bus se convierte en el bus del sistema. Buses de tipo 3 El bus de tipo 3 o bus del sistema permite interconectar diversos mdulos del computador. Hoy en da hay muy pocos sistemas que contengan varios mdulos. Por lo que generalmente coinciden los buses de nivel 2 y 3. La gran diferencia entre los tipos 2 y 3 es la distancia que debe tener el bus, que puede llegar a los 10m en el tipo 3. Ello obliga a tratar este bus como una lnea de transmisin. Adems, es muy frecuente que el bus de tipo 3 exija unos repetidores o buffers, para pasar de un panel posterior a otro. Buses de tipo 4 Los buses de tipo 4 lo forman los buses paralelos para conexin de perifricos. En realidad se pueden considerar cuatro situaciones, que a veces se pueden dar simultneamente en el mismo computador: En la primera, los controladores de los perifricos se conectan directamente al bus del sistema (bus tipo 2 3).

En la segunda se dispone de un bus especial para la E/S, como es un canal 370 de IBM, como es el Unibus en el caso de la arquitectura VAX, o como son los buses PCI e EISA en un computador personal. La tercera consiste en disear un bus reducido, derivado del bus del sistema, que permita la conexin en paralelo de una serie de perifricos especficos. La cuarta consiste en emplear un bus paralelo de conexin de perifricos, de acuerdo con una norma preestablecida. La diferencia con el caso anterior es que ahora no se trata de una versin reducida del bus del sistema, sino de una configuracin que puede ser muy distinta. El ejemplo clsico es el puerto paralelo o Centronics, previsto para la conexin de impresoras, el bus IEEE-488, previsto para la interconexin de instrumentos de laboratorio a computadores o los buses QIC, SCSI e IPI, para conexin de discos. Buses de tipo 5 Los buses serie suelen constituir el tipo ms elemental del espectro de las comunicaciones de un sistema informtico. Se emplean para cubrir las mayores distancias. El bus serie puede ser simple o doble. El simple puede permitir la transmisin en un solo sentido o en ambos sentidos de forma alternativa (semi-duplex). El doble permite la transmisin en los dos sentidos simultneamente (full-duplex). Un ejemplo de bus serie es el bus USB, que tratamos ms adelante. [1] [2] 2.3. ESTRUCTURA DEL BUS Un bus est constituido por muchas lneas, por ejemplo el bus del sistema est constituido por entre 50 y 100 lneas. A cada lnea se le asigna una funcin determinada. Las lneas del bus se pueden clasificar en tres grupos funcionales: lneas de datos, de direcciones, y de control. " Las lneas de datos del bus proporcionan el camino para transmitir datos entre los mdulos del sistema. El bus de datos consta de 8, 16, 32 lneas distintas, cuyo nmero se conoce como anchura del bus de datos. Este nmero de lneas determina cuantos bits se pueden transmitir al mismo tiempo. La anchura del bus es un factor clave a la hora de determinar las prestaciones del sistema. " Las lneas de direccin se utilizan para direccionar la fuente o el destino de los datos situados en el bus de datos. La anchura del bus de direcciones determina la cantidad mxima de memoria direccionable en el sistema.

" Las lneas de control se emplean para gestionar el acceso y el uso de las lneas de datos y direccin, sealizando peticiones y reconocimientos e indicando que tipo de informacin pasa por las lneas de datos. Figura: 2 Estructura de Bus tpica. Algunas lneas de control tpicas son:

Escritura en memoria (Memory Write): hace que el dato del bus se escriba en la posicin direccionada. Lectura de memoria (Memory Read): hace que el dato de la posicin direccionada se site en el bus. Escritura de E/S (I/O Write): hace que el dato del bus se transfiera a travs del puerto de E/S direccionado. Lectura de E/S (I/O Read): hace que dato del puerto de E/S direccionado se site en bus. Transferencia reconocida (Transfer ACK): indica que el dato se ha aceptado o se ha situado en bus. Peticin de bus (Bus Request): Indica que un modulo necesita disponer del control del bus. Cesin de bus (Bus Grant): indica que se cede el control del bus a un mdulo que lo haba solicitado. Peticin de interrupcin (Interrupt Request): indica si hay una interrupcin pendiente. Interrupcin reconocida (Interrupt ACK): seala que la interrupcin pendiente se ha aceptado. Reloj (Clock): se utiliza para sincronizar las operaciones. Inicio (Reset): pone los mdulos conectados en su estado inicial

2.4 CARACTERSTICAS DE LOS BUSES Paralelismo del bus Un bus puede ser paralelo, multiplexado o serie.

Normalmente, el bus paralelo tiene un ancho de palabra que coincide con el ancho de la informacin a transmitir. El bus multiplexado se origin como consecuencia de tener que ahorrar conexiones (patas) debido a la necesidad de una alta integracin de los componentes del ordenador. Un ejemplo de este uso es comunicar las direcciones de memoria entre el microprocesador y la memoria (en su forma fsica de chips). Consiste en utilizar los mismos hilos para enviar, en momentos distintos, informaciones distintas, permitiendo con el uso de seales adicionales, identificar la informacin o tipo de informacin que circula por el bus en cada momento. Generalmente el resto del sistema exige que el bus no est multiplexado. En estos casos en los extremos del bus se encontrarn multiplexores para realizar la multiplexacin / demultiplexacin. El bus serie esta formado nicamente por un par de hilos, por los que circula la informacin bit a bit. Durante el envo es necesario dividir la palabra en bits as como realizar un agrupamiento de estos bits para formar una palabra en la recepcin. Funcin El bus puede ser de carcter general o especfico. Los buses especficos, dedicados cada uno a una funcin permiten un diseo sencillo, y que la capacidad de transferencia total sea mayor. Los buses de carcter general reducen el nmero de hilos que llegan a la UCP, por lo que es especialmente til para microprocesadores. El esquema formado por estos buses es comparativamente ms sencillo, aunque cada bus individualmente sean ms complejos que los de carcter global. Ciclo de Funcionamiento Bus de ciclo completo En un bus de estas caractersticas todas las fases a realizar se efectan una detrs de otra, sin ningn espacio entre ellas. Normalmente se utiliza en sistemas sencillos, en especial con un nico dispositivo que acte como maestro. Bus de ciclo partido o de paquetes El tiempo de ciclo partido se divide en una serie de ranuras, cada una de las cuales permite enviar un mensaje. Estas ranuras pueden tener duracin fija y predefinida, y en caso de utilizarse una seal de reloj; es sncrona. Este bus es ms rpido que el anterior a costa de complicar los dispositivos que lo integran, por tanto se suele emplear en sistemas multiprocesador.

Algunas consideraciones adicionales sobre el esquema de este ltimo tipo:

En caso de existir mltiples peticionarios se debe almacenar la identificacin de ste. Debe disponer de mecanismos de control a la memoria, evitando accesos mltiples. Se disear de forma que se eviten colisiones, es decir que dos dispositivos puedan acceder a una ranura simultneamente.

[1] [2] Transferencias sncronas y asncronas

Transferencia en ciclo completo Figura: 3 Transferencia en ciclo completa. En este caso de forma resumida podemos decir que:

Lectura sncrona. El maestro pone en el bus la direccin deseada, y supone que el esclavo, a su vez, pone el dato en el bus en el tiempo T, momento en el que el maestro lo toma. Escritura sncrona. El maestro pone en el bus la direccin y el dato, y supone que el esclavo toma esta informacin antes de cierto tiempo T. Lectura asncrona. El maestro pone en el bus la direccin deseada, y se queda esperando hasta que el esclavo conteste, confirmando que ha puesto el dato en el bus, o bien hasta que la espera sobrepase determinado tiempo, en cuyo caso se genera una seal de error.

Escritura asncrona. El maestro pone en el bus la direccin y el dato, y se queda esperando que el esclavo confirme que ha tomado esta informacin. Si la espera sobrepasa un cierto intervalo, el maestro genera un error. [4]

Transferencia en ciclo partido Muy similar a la operacin de ciclo completo tan slo est dividida en fase de inicio de la transferencia y fase de fin de transferencia, ocupando cada una de ellas una ranura. La transferencia la inicia un maestro, empleando una de las ranuras del bus, y la finaliza el esclavo, empleando otra ranura, por lo que los esclavos deben tener la capacidad de solicitar y emplear ranuras del bus, para poder finalizar adecuadamente las transferencias. Como ya hemos visto antes si existen varios maestros potenciales, a la solicitud enviada por el bus deber incluir la identificacin del maestro, de forma que el esclavo pueda contestar adecuadamente.

Lectura sncrona. Esta lectura se compone de dos ranuras. En la primera, el maestro enva la orden de lectura, as como la direccin deseada. Un cierto tiempo despus, cuando dispone del dato pedido, el esclavo solicita otra ranura, para enviar el dato. Despus de x tiempo de espera sin contestacin se genera una seal de error. Escritura asncrona. En una nica ranura el maestro enva el dato y la direccin. Lectura asncrona. La lectura asncrona puede ser igual a la sncrona anterior, en algunos casos se utiliza una ranura adicional para comprobar que la direccin es correcta o se ha generado un error. Escritura Asncrona. Se utiliza una ranura para que el maestro enve la direccin y el dato, y una segunda ranura para que el esclavo confirme que ha realizado la operacin de escritura. Figura: 4 Transferencia en ciclo partido. [4]

2.5 ARBITRAJE Protocolos de Arbitraje Es la poltica de asignacin del bus en el caso de que varios dispositivos compartan su uso. Es similar a los protocolos de comunicaciones en redes de rea local. La funcin de estos protocolos es garantizar el acceso al bus sin conflictos cuando existen varios dispositivos que pueden actuar como master. Existen dos tipos bsicos: Arbitraje centralizado

Cuando hay un master principal, denominado rbitro, que controla el acceso al bus. Lo realiza un mdulo central de arbitraje.

You might also like

- Cap. 8 GestiónDocument32 pagesCap. 8 GestiónSam RodríguezNo ratings yet

- Ejemplo MVCDocument12 pagesEjemplo MVCOskar CadenaNo ratings yet

- Base de Datos 2 - Concurrencia, Problemas y Métodos de ControlDocument9 pagesBase de Datos 2 - Concurrencia, Problemas y Métodos de ControlSam RodríguezNo ratings yet

- EC10 Bus OkDocument20 pagesEC10 Bus OkmuistipunkNo ratings yet

- Capítulo 4 Uso de Análisis de Java CUPDocument26 pagesCapítulo 4 Uso de Análisis de Java CUPSam RodríguezNo ratings yet

- Chucvisión Del Producto y Alcance Del ProyectoDocument28 pagesChucvisión Del Producto y Alcance Del ProyectoSindi DzulNo ratings yet

- λ 0.75 Lq L TC μ 1.25 Cw 10 Cs 7: Investigación de Operaciones II Rodríguez Tun SandraDocument1 pageλ 0.75 Lq L TC μ 1.25 Cw 10 Cs 7: Investigación de Operaciones II Rodríguez Tun SandraSam RodríguezNo ratings yet

- Calendario Escolar 2012-2013 UACDocument1 pageCalendario Escolar 2012-2013 UACSam RodríguezNo ratings yet

- RequerimientosDocument28 pagesRequerimientosSam RodríguezNo ratings yet

- 312TecnicasAuditIngenieriaSoftware PCaneoDocument28 pages312TecnicasAuditIngenieriaSoftware PCaneoSam RodríguezNo ratings yet

- Base de DatosDocument3 pagesBase de DatosSam RodríguezNo ratings yet

- Actitudes PositivasDocument19 pagesActitudes Positivasvanessa zavaletaNo ratings yet

- Plan de Accion para El PlátanoDocument29 pagesPlan de Accion para El PlátanoCesar SiguenzaNo ratings yet

- Visual Basic 6 0 UltimoDocument65 pagesVisual Basic 6 0 UltimoWILSONNo ratings yet

- Proyecto Anual 2022 Estrada 5to y 6toDocument14 pagesProyecto Anual 2022 Estrada 5to y 6toAriel GismanoNo ratings yet

- TALLER "Marketing Mix o 4P S"Document10 pagesTALLER "Marketing Mix o 4P S"ramiro andres mena cardenasNo ratings yet

- PROYECTO DE sINDROME DE ESTOCOLMO - MALTRATO A LA MUJERDocument15 pagesPROYECTO DE sINDROME DE ESTOCOLMO - MALTRATO A LA MUJERKevin FrancoNo ratings yet

- Taller Sociologia JuridicaDocument5 pagesTaller Sociologia Juridicaluis fernando medina soteloNo ratings yet

- Práctica 2Document3 pagesPráctica 2Paola MartinezNo ratings yet

- Biometrias 2Document517 pagesBiometrias 2Mike Sanso100% (1)

- SARNA - Spanish TranslationDocument2 pagesSARNA - Spanish TranslationJuan Luis AcuñaNo ratings yet

- Brochure JK Simblast 04 OctubreDocument12 pagesBrochure JK Simblast 04 OctubreJoel Nuñez NuñezNo ratings yet

- S 5 I G VDocument84 pagesS 5 I G VOscar ChávezNo ratings yet

- 1 Unidad Civica 9Document24 pages1 Unidad Civica 9mariajoseibarraNo ratings yet

- Bitacora de Ppe Estudiante 9Document17 pagesBitacora de Ppe Estudiante 9Ivonne Lara FrancoNo ratings yet

- Estudios de planificación urbana ante desastres ZarumillaDocument412 pagesEstudios de planificación urbana ante desastres Zarumillaeguar100% (1)

- Caracteristicas Generales Del Derecho AnglosajonDocument3 pagesCaracteristicas Generales Del Derecho AnglosajonLuis Augusto Zenteno Enriquez100% (1)

- Ministerio de Desarrollo Social de La NaciónDocument3 pagesMinisterio de Desarrollo Social de La NaciónEdu Lalo MejiasNo ratings yet

- Auditoria III Tema 2Document25 pagesAuditoria III Tema 2Reinaldo PerniaNo ratings yet

- Informe Desembarque Pesquero en PucallpaDocument16 pagesInforme Desembarque Pesquero en PucallpaTunombretsamajain Jose LiriodevalleNo ratings yet

- Concussion y La Encefalopatia Traumatica CronicaDocument2 pagesConcussion y La Encefalopatia Traumatica CronicaHillary V Guillermo AngelesNo ratings yet

- Plan de Marketing CarambolaDocument40 pagesPlan de Marketing Carambolamiguel_moran29228963% (8)

- Presentación Taller N°2 Salud MentalDocument6 pagesPresentación Taller N°2 Salud MentalIsabel HernandezNo ratings yet

- Farmacia Hospitalaria Semana 4Document22 pagesFarmacia Hospitalaria Semana 4Ellie DarkNo ratings yet

- Entregable Final - Desarrollo EmpresarialDocument6 pagesEntregable Final - Desarrollo EmpresarialAlonso CeronNo ratings yet

- Hoja 1 Constitución Política de GuatemalaDocument5 pagesHoja 1 Constitución Política de GuatemalaJeannette Fuentes DiazNo ratings yet

- Como El Color Del Brezo - Josephine LysDocument233 pagesComo El Color Del Brezo - Josephine LysNana Rojas100% (2)

- Las Teorías Del Diseño Urbano en La Conceptualización Del Espacio Urbano y Sus Dos CategoríasDocument12 pagesLas Teorías Del Diseño Urbano en La Conceptualización Del Espacio Urbano y Sus Dos CategoríasSteevinson PatrickNo ratings yet

- Decreto de Urgencia Que Modifica Los Decretos de Urgencia #026-2020 y #078-2020 y El Decreto Legislativo #1505Document2 pagesDecreto de Urgencia Que Modifica Los Decretos de Urgencia #026-2020 y #078-2020 y El Decreto Legislativo #1505Melissa CosmópolisNo ratings yet

- Anatomía Texto Paralelo LisDocument53 pagesAnatomía Texto Paralelo LisMaureen Mendez100% (2)

- Mapa Conceptual Del Teatro Español Del Siglo XXDocument1 pageMapa Conceptual Del Teatro Español Del Siglo XXRachel Durand FuentesNo ratings yet