Professional Documents

Culture Documents

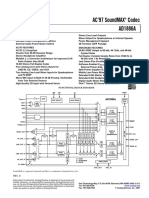

Technology: Multi-Channel Audio CODEC

Uploaded by

vetchboyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Technology: Multi-Channel Audio CODEC

Uploaded by

vetchboyCopyright:

Available Formats

AVS Technology AV2188

Multi-Channel Audio CODEC

FEATURES - -96 dB THD + N Ratio.

• Six Channel 24/20-bit DACs. - I2S and Left Justified Output Formats.

- 102 dB SNR • System clock: 384 fs for 32, 44.1 or 48 KH.

Sampling Rates, 192 fs for 96 KHz. Sam-

- 104 dB Dynamic Range. pling Rate.

- -92 dB THD + N Ratio.

- 32,44.1, 48, 96 and 192KHz. Sampling General

rates. • Automatic input format detection.

- 20-bit and 24-bit Digital Inputs. • 5-volt Power Supply.

- Containing Digital De-emphasis Filters. • 3.3 -volt Digital Interface Friendly.

- Digital Volume Control. • I2C Interface for Mode Setting.

- I2S, Left and Right Justified Digital Input

Formats. Applications

- Auto-Mute Control.

• Digital Surround Sound For Home Theater

- On -chip Reconstruction Filters.

• DVD

• Two Channel Stereo ADCs

• Car Audio.

- 32, 44.1 and 48 KHz. Sampling Rate.

- 100 dB SNR and Dynamic Range.

SDA I2C Serial

Control Port

AV2188

SCL D/A 40KHz VOR3

SD1 80 D/A VOL3

40KHz

5th Order Σ∆

Digital Volume

De-Emphasis

Over-sampling

Modulators

SD2 80

D/A 40KHz VOR2

96 Times

Filters

Audio I/F

Serial

SD3 77

D/A 40KHz VOL2

SDOUT 80

D/A 40KHz VOR1

SF 77 D/A 40KHz VOL1

High Pass

SC 78 Filter

A/D BIN

Decimation

Format

Filter

PLL A/D AIN

Detect'n

15

XCK RST

AVS Technology Inc.

4110 Clipper Ct., Fremont CA94538 1-19 January 4, 2001

Tel: (510) 353-0848

Fax: (510) 353-0856

AV2188

Item PERFORMANCE SPECIFICATIONS Spec.

Audio DAC

1 Audio Output Level 1 Vrms

2 Audio Bandwidth 20Hz - 20 KHz +/- 0.1 dB

3 SNR (A-weight, Muted) >102 dB

4 SNR (A-weight, Not Muted) >96 dB

6 THD + N (A-weight, FFS Output) < -92 dB

7 Dynamic Range 104 dB

8 Channel Separation < -96 dB

9 Nonlinear Distortion < 0.25 dB

10 Channel Gain Error < 0.1 dB

Audio ADC

1 Full Scale Audio Input Level 3.5 Vp-p

2 Maximum Input Level 5.0 Vp-p

2 Audio Bandwidth 15 KHz

3 SNR 98 dB

4 THD + N (A-weight, 0.5 FFS Input) 96 dB

4 Dynamic Range 98 dB

All Measurement were taken with only one channel active.

2-19 January 4, 2001

AV2188

DESCRIPTION

The AV2188 is a mixed signal CMOS monolithic audio CODEC. It consists six channels sigma delta DACs and two

channels sigma delta ADCs. The DACs support 20-bit and 24-bit input data, while the ADCs provides 24-bit MSB

justified data output.

XCK REQUIREMENT

The AV2188 support 384 and 256 times sampling clock for 32, 44.1 and 48 K audio; 192 and 128 times for the 96

K audio.; and 96 and 64 times for the 192K audio.

XCK Requirement

Sampling XCK Freq.

Rate 384*fs 256*fs

32 K 12.288 MHz 8.192 MHz

44.1 16.934 Mhz 11.29 Mhz.

48 K 18.432 MHz 12.288 Mhz.

96 K 18.432 MHz 12.288 Mhz.

192 K 18.432 Mhz 12.288 Mhz.

3-19 January 4, 2001

AV2188

PIN ASSIGNMENT

SD1 1 28 AR3

SD2 2 27 AL3

SD3 3 26 AR2

SDOUT 4 25 AL2

SC 5 24 AR1

A V 2 1 8 8

SF 6 23 AL1

DGND 7 22 AGND

DVDD 8 21 CM2

DGND 9 20 AVDD

XCK 10 19 CM1

SCL 11 18 AGND

SDA 12 17 RIN

TST 13 16 LIN

RST 14 15 N/C

PIN DESCRIPTION

Pin Name Pin # Type Description

DIGITAL

SD1 1 I Audio Serial Data Input 1, data can be 20bit/24bit, Right justified, or 24bit Left

justified, or 24bit I2S, all in 2’s complement format.

SD2 2 I Audio Serial Data Input 2, data can be 20bit/24bit, Right justified, or 24bit Left

justified, or 24bit I2S, all in 2’s complement format.

SD3 3 I Audio Serial Data Input 3, data can be 20bit/24bit, Right justified, or 24bit Left

justified, or 24bit I2S, all in 2’s complement format.

SDOUT 4 O Serial Audio Output pin, data can be in 24/20bit left justified or 24/20 bit I2S

format.

SC 5 I Audio Serial Data Clock pin.

SF 6 I Left/Right Channel Clock pin. For Left justified or Right justified mode, a high in

SF indicates Left Channel Data, a low in SF indicates Right Channel Data. For

I2S mode, a low in SF indicates Left Channel Data, a high in SF indicates Right

Channel Data.

DVSS 7 GND Digital ground

4-19 January 4, 2001

AV2188

PIN DESCRIPTION (Continued)

Pin Name Pin # Type Description

DVDD 8 +5V Digital power supply.

DVSS 9 GND Digital ground

XCK 10 I External Master Clock Input.

SCL 11 I I2C clock input.

SDA 12 I/O I2C DATA bus. Open drain output. Externally this pin should tie to a 680 ohm

pull up resistor.

TEST 11 O Test fs reference pin. For test vector verification. For normal operation this pin

must be tied to ‘0’.

RST 12 I Active low power down reset. When low, the chip is reset and all programmable

registers are reset to default values.

Analog

VOL3 28 O Analog left channel output 3

VOR3 27 O Analog right channel output 3.

VOL2 26 O Analog left channel output 2.

VOR2 25 O Analog right channel output 2.

VOL1 24 O Analog left channel output 1.

VOR1 23 O Analog right channel output 1.

AVSS 22 GND Analog circuits ground

VCM2 21 Common voltage output pin for the DAC.

AVDD 20 +5V Analog circuits power supply

VCM1 19 Common voltage output pin for the ADC.

AVSS 18 GND Analog circuits ground

AINR 17 I ADC right channel input. 1 volt rms input.

AINL 16 I ADC left channel input. 1 volt rms input.

N/C 15 No connection, should be tied to AVSS

5-19 January 4, 2001

AV2188

DIGITAL AUDIO SERIAL INTERFACE

The digital serial interface consists of 3 serial input pins, SD1, SD2, and SD3, one serial output pin, SDOUT, one

serial clock input pin, SC, and one left/right indicator input pin, SF. The data are 2’s complement MSB first

numbers. The AV2188 supports four resolution, which are selected either by setting the FMT[1] and FMT[0] pins or

by programming the control register CREG0[5:4] via the I2C serial control port. Table 1 describes these four

resolution.

Table (1): Audio Serial Data Input Format,

Format CREG0[5] CREG0[4] SD1, SD2, and SD3 SDOUT

0 0 0 24-bit

1 0 1 20-bit 24-bit

2 1 0 18-bit

3 1 1 16-bit

The SD3, SD2 and SD1 can be either 24-bit or 32-bit per frame as well as left justified, right justified or I2S. The

SDOUT only support left justified and I2S format. The AV1488 counts the number of BCK per frame to determine

whether the input is 24 or 32 bits format.

Table (1): Audio Serial Data Input Modes

Mode CREG0[7] 0REG0[6] SD1, SD2, and SD3 SDOUT

0 0 0 Right Justified Left Justified

1 0 1 I2S I2S

2 1 0 Left Justified Left Justified

3 1 1 Invalid

6-19 January 4, 2001

AV2188

Figure 1. Audio Serial Input Data Timing Diagram

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 2 1 0 2 1 0

Right justified, CREG0[7,6]=[0 0]

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 0 1 0

Left justified, CREG0[7,6]=[1 0]

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 1 0 1 0

IIS, CREG0[7,6]=[0 1]

Figure 2.

7-19 January 4, 2001

AV2188

Figure 3. Audio Serial Output Data Timing Diagram

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 23 22 21 2 1 0 23 22 21 2 1 0

Left justified, CREG0[7,6]=[X 0]

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3

23 22 21 2 1 0 23 22 21 2 1 0

IIS, CREG0[7,6]=[0 1]

8-19 January 4, 2001

AV2188

INFINITE ZERO DETECTION

The AV2188 has an Infinite Zero Detection circuit which detects zero in the Audio Serial Port that lasts for

approximately 0.5 sec. By default, the zero detection circuit is on.

Serial Command Port

The user can use the pin to select the chip operation or by programming the internal control registers through the 7

bit address I2C port. The Chip Address for the AV2188 is 31H. The protocol for write operation consists of sending

3 byte data to AV2188, following each byte are the acknowledges generated by AV2188. The first byte is the 7-bit

Chip Address followed by the read/write bit (read is high write is low). The second byte is the control register

address. The third byte is the control register data.

Upon power up, all programmable registers are set to default values. Figure 4 describes the serial command port

timing relationship.

Figure 4. Serial Command Port Timing

I2 C Bus Control Register write example:

Start CA6 CA0 R/W ACK A7 A0 ACK D7 D0 ACK Stop

SDA 1 1 1

SCL

Chip adrress: CA<6:0> = 31H

Register address: A<7:0> = 00H

DATA: D<7:0> = 30H

9-19 January 4, 2001

AV2188

SERIAL PORT CONTROL REGISTER ASSIGNMENT

There are 3 registers dedicated to the AV2188 for chip functional programming,. One register for testing. The

register addresses assignments are

Address Default

Register Register Function

(decimal) Value

0 CREG0[7:0] 80 Data input format, de-emphasis filter selection

1 CREG1[7:0] 80 DAC and ADC power down control

2 VOLREG[7:0] 80 Volume control

3 TREG1[7:0] 00 Test control

10-19 January 4, 2001

AV2188

CONTROL REGISTERS DESCRIPTION

Control Register 0(ADRS=hex00, default=hex80)

CREG0[7:0]

ADDR[4:0]

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Hex 00 LT IIS FMT[1:0] AMUTE DEM[1:0]

Default Value 1 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W

[LT, IIS] Digital Serial Bus Format Select

00: - Normal or Right Justified Format.

01: - I2S Format.

10: - Left Justified Format. (default)

11: - Not allowed.

FMT[1:0]: - These two bits define the serial audio input resolution

00: - 24-bit resolution. (default)

01: - 20-bit resolution.

10: - 18-bit resolution.

11: - 16-bit resolution.

AMUTE: - Active low auto-mute detection enable.

0: - Auto-mute enabled. (default)

1: - No auto-mute.

DEML: - De-emphasis Control

00: - No De-emphasis. (default)

01: - Select 44.1K de-emphasis filter.

10:- Select 48 K de-emphasis filter.

Control Register 1 (ADRS=hex01, default=hex80)

CREG1[7:0]

ADDR[4:0]

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Hex 01 ADCPWD fs384 px4s px2s DACPWD12 DACPWD34 DACPWd56

Default Value 1 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W

ADCPWD: ADC Control.

0 - ADC operational.

1 - Power down the ADC.

11-19 January 4, 2001

AV2188

DACPWD56: DAC5 and DAC6 Control.

0 - DAC5 and DAC 6 operational.

1 - Power down the DAC5 and DAC6.

DACPWD43: DAC3 and DAC4 Control.

0 - DAC3 and DAC4 operational.

1 - Power down the DAC3 and DAC4.

DACPWD21: DAC2 and DAC1 Control.

0 - DAC2 and DAC1 operational.

1 - Power down the DAC2 and DAC1.

Volume Registers, (ADRS=hex02, default=hex80)

Volume Registers

ADDR[4:0]

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Hex 02 VLREG[7:0]

Default Value 1 0 0 0 0 0 0 0

VOLREG:- Control the volume of the 6 DAC’s

80h- corresponds to 0 dB setting.

12-19 January 4, 2001

AV2188

Application Connection Example:

Digital 4.7 ohm Analog

+5 Volt

22 uF 8 20 22 uF

DVCC AVCC

22 uF

1 28

SD1 AR3

2

SD2 27 22 uF

3

SD3

AV2188 AL3

Digital Audio 4 26 22 uF

Interface SDOUT AR2

5 25 22 uF

SC AL2

6

SF 24 22 uF

AR1

384 or 256 Times 10

XCK 23 22 uF

SF C lock

AL1

21

+5 Volt CM2

47uF

680 ohm

11

2 19

I C Serial SCL

CM1

Interface 12 47uF

SDA

220 ohm 22 uF

13 17

TST RIN

200K

14

Reset 220 ohm 22 uF

RST 16

LIN

200K

DVSS AVSS

All Unmarked 18 22

7 9 15

Capacitors are

0.1 uF

13-19 January 4, 2001

AV2188

TIMING DIAGRAM

Figure 5. Audio Serial Interface Timing Requirement

tsc

tscH tscL

SC

tsd su

SD1-3

tsdout mx tsd hd

SDOUT

tsdout mn

tsf su

SF

tsf hd

Figure 6. Serial Command Port Write Timing Requirement

tBUF tSU;STA

SDA

tHD;STA tSU;DAT

tSU;STO

tHIGH

SCL P S P

Sr

tLOW

tR

tF tHD;DAT

14-19 January 4, 2001

AV2188

Figure 7. Power Down / Reset Timing

trst

PWD

ABSOLUTE MAXIMUM RATINGS

Symbol Characteristics Min Max Units

VDD Power Supply Voltage (Measured to GND) -0.5 +7.0 V

Vi Digital Input Applied Voltage2 GND-0.5 V

Ai Digital Input Forced Current3,4 -100 100 mA

Vo Digital Output Applied Voltage2 GND-0.5 VDD+0.5 V

Ao Digital Output Forced Current3,4 -100 100 mA

TDsc Digital Short Circuit Duration (single output high state to Vss) 1 Sec

TASC Analog Short Circuit Duration (single output to VSS1) infinite Sec

Ta Ambient Operating Temperature Range -25 +125 o C

Tstg Storage Temperature Range -65 +150 o C

Tj Junction Temperature (Plastic Package) -65 +150 o C

Tsol Lead Soldering Temperature (10 sec., 1/4” from pin) 300 o C

Tvsol Vapor Phase Soldering (1 minute) 220 o C

Tstor Storage Temperature -65 +150 o C

Notes:

1. Absolute maximum ratings are limiting values applied individually, while all other parameters are within specified

operating conditions.

2. Applied voltage must be current limited to specified range, and measured with respect to VSS.

3. Forcing voltage must be limited to specified range.

4. Current is specified as conventional current, flowing into the device.

15-19 January 4, 2001

AV2188

RECOMMENDED OPERATING CONDITIONS

Symbol Characteristics Min Typical Max Units

VDD Power supply voltage 4.5 5 5.5 V

VVCM Reference voltage 2.25 2.41 V

RL Analog output load 37.5 70 Ω

Ta Ambient operating temperature range 0 70 o C

ELECTRICAL CHRACTERISTICS

Parameter Characteristics Min Typ Max Units

Supply

IDD Total Power Supply Current, Analog + Digital 135 145 mA

Digital Characteristics

VIH Digital Input Voltage, Logic HIGH, 2.0 VDD V

TTL Compatible Inputs.

VIL Digital Input Voltage, Logic LOW, VSS 0.8 V

TTL Compatible Inputs

IIH Digital Input Current, Logic HIGH, (VIN=4.0V) 10 µA

IIL Digital Input Current, Logic LOW, (VIN=0.4V) -10 µA

CIN Digital Input Capacitance (f=1Mhz, VIN=2.4V) 7 pF

VOH Digital Output Voltage, Logic HIGH, 3.2 3.4 3.5 V

(IOH= -1mA)

VOL Digital Output Voltage, Logic LOW, VSS 0.4 V

(IOL=4.0 mA)

IOZH Hi-Z Leakage Current, HIGH, 10 µA

VDD=Max, VIN=VDD)

IOZL Hi-Z Leakage Current, LOW, -10 µA

VDD=Max, VIN=VSS)

CI Digital Input Capacitance (TA=25oC, f=1Mhz) 8 pF

CO Digital Output Capacitance (TA=25oC, 10 pF

f=1Mhz)

16-19 January 4, 2001

AV2188

Parameter Characteristics Min Typ Max Units

Audio Serial Interface Timing

tsc SC Cycle Time 80 ns

tscH SC Pulse Width, HIGH 30 ns

tscL SC Pulse Width, LOW 30 ns

tsdsu Audio Data Setup Time With Respect To Ris- 10 ns

ing Edge of SC

tsdhd Audio Data Hold Time With Respect to Rising 15 ns

Edge of SC

tsfsu Audio SFSetup Time With Respect To Rising 10 ns

Edge of SC

tsfhd Audio SF Hold Time With Respect To Rising 15 ns

Edge of SC

tsdoutmx SC falling edge to SDOUT Valid 25 ns

tsdoutmn SC falling edge to SDOUT Valid 5 ns

Reset Signal

trst Active low reset time 1 µs

Serial Command Port

fsc SCL Clock Frequency 100 kHz

tsu;sta Start condition set up time 4.7 us

thd;sta Start condition hold time 4.0 us

tsu;sto Stop condition set up time 4.0 us

tLOW SCL Low time 4.7 us

tHIGH SCL High time 4.0 us

tr SCL & SDA rise time 1.0 us

tf SCL & SDA fall time 0.3 us

tsu;DAT Data set-up time 250 ns

thd;DAT Data hold time 0 ns

tvd;DAT SCL LOW to data out valid 3.4 us

tBUF Bus Free time 4.7 us

17-19 January 4, 2001

AV2188

Parameter Characteristics Min Typ Max Units

Audio DAC Characteristics

SNR Signal To Noise Ratio 99 102 dB

THD+N Total Harmonic Distortion + Noise 94 dB

Dynamic Range 102 104 dB

Channel Separation 84 97 dB

Full Scale Output Voltage .96 1 1.02 Vrms

Center Voltage 2.18 2.20 2.25 V

Inter-channel Gain Mismatch 0.1 dB

Analog Output Load Resistance 5 KΩ

Analog Output Load Capacitance 100 pF

Audio ADC Characteristic

SNR Signal To Noise Ratio 98 dB

THD+N Total Harmonic Distortion + Noise 94 dB

Dynamic Range 102 dB

Channel Separation 96 dB

Full Scale Input Voltage 1.3 Vrms

Center Voltage 1.6 2.20 2.5 V

Inter-channel Gain Mismatch 0.1 dB

Analog Input Load Capacitance 30 pF

18-19 January 4, 2001

AV2188

PACKAGING INFORMATION

Dimensions

Mils Mils

min norm max min norm max

A 93 100 104 E1 291 295 299

A1 4 8 12 E2 394 406 419

b 14 16 19 e 50

C 9 10 12 L 20 30 40

D 691 702 713

28-Pin (SOP)

A1

E2 A

E1

19-19 January 4, 2001

You might also like

- Technology: Multi-Channel Audio CODECDocument20 pagesTechnology: Multi-Channel Audio CODECvetchboyNo ratings yet

- 2 Adc, 8 Dac, 96 KHZ, 24-Bit: - CodecDocument25 pages2 Adc, 8 Dac, 96 KHZ, 24-Bit: - Codecmusical_cat2No ratings yet

- Pawpaw: Analog ReinventedDocument64 pagesPawpaw: Analog ReinventedНиколайNo ratings yet

- Cs4362a F2Document50 pagesCs4362a F2raiksonNo ratings yet

- ES9038Q2M Datasheet v1.4Document65 pagesES9038Q2M Datasheet v1.4Thắng NguyễnNo ratings yet

- PCM 5102Document38 pagesPCM 5102Володимир ТеліженкоNo ratings yet

- Pcm3168a q1 PDFDocument66 pagesPcm3168a q1 PDFSATYAM NAIDUNo ratings yet

- Description Features: SBAS067Document10 pagesDescription Features: SBAS067vetchboyNo ratings yet

- ES9016S Datasheet v1.91Document33 pagesES9016S Datasheet v1.91Nursapta nugrohoNo ratings yet

- Six Channel, 20-Bit Codec: Features DescriptionDocument36 pagesSix Channel, 20-Bit Codec: Features Descriptionalive ElectronicsNo ratings yet

- Ad1939 PDFDocument32 pagesAd1939 PDFMax MaierNo ratings yet

- Sigmadsp 28/56-Bit Audio Processor With 2Adc/4Dac Adau1701: Preliminary Technical DataDocument43 pagesSigmadsp 28/56-Bit Audio Processor With 2Adc/4Dac Adau1701: Preliminary Technical DataNguyễn Quang TrânNo ratings yet

- Analog Reinvented: High Performance USB DAC With Headphone Amplifier, MQA, ADC, PLL, Jack Detect, Mic, and A/D MixingDocument3 pagesAnalog Reinvented: High Performance USB DAC With Headphone Amplifier, MQA, ADC, PLL, Jack Detect, Mic, and A/D MixingCoreyNo ratings yet

- 4 Adc/8 Dac With PLL, 192 KHZ, 24-Bit Codec: Data SheetDocument33 pages4 Adc/8 Dac With PLL, 192 KHZ, 24-Bit Codec: Data SheetLAI YEEK HRVENo ratings yet

- CS4398 DS568F4Document45 pagesCS4398 DS568F4vantri27082004No ratings yet

- PCM 1802Document32 pagesPCM 1802Raiatea MoeataNo ratings yet

- 16-Channel High Performance Differential Output, 192 KHZ, 24-Bit DacDocument52 pages16-Channel High Performance Differential Output, 192 KHZ, 24-Bit DaczorkerNo ratings yet

- ASIO4ALL v2 Instruction ManualDocument4 pagesASIO4ALL v2 Instruction ManualromanbunNo ratings yet

- PCM 1796Document61 pagesPCM 1796joe joeNo ratings yet

- 3G-SDI Analog and Digital Audio Embedder / De-Embedder: FlashlinkDocument4 pages3G-SDI Analog and Digital Audio Embedder / De-Embedder: FlashlinkPhuong HaNo ratings yet

- 98 Ak 4480 EfDocument44 pages98 Ak 4480 EfYurii LembergNo ratings yet

- Features: Crystalclear™ Portable Isa Audio SystemDocument98 pagesFeatures: Crystalclear™ Portable Isa Audio Systemradaki-1No ratings yet

- PCM 5121Document107 pagesPCM 5121Fabio Da Silva Assunçao AssunçaoNo ratings yet

- High Feature 96Khz 24bit Dir: Asahi Kasei (Ak4112A)Document32 pagesHigh Feature 96Khz 24bit Dir: Asahi Kasei (Ak4112A)DavidNo ratings yet

- Ad1886A Ac'97 Soundmax Codec: - Converter Architecture For Improved S/NDocument29 pagesAd1886A Ac'97 Soundmax Codec: - Converter Architecture For Improved S/NCIACIACIACIACIACIANo ratings yet

- BW Broadcast DSPX-FM Datasheet PDFDocument1 pageBW Broadcast DSPX-FM Datasheet PDFwendyNo ratings yet

- TLV 320 Aic 3100Document134 pagesTLV 320 Aic 3100megatornadoNo ratings yet

- Pcm175X 24-Bit, 192-Khz Sampling, Enhanced Multilevel, Delta-Sigma, Audio, Digital-To-Analog ConverterDocument41 pagesPcm175X 24-Bit, 192-Khz Sampling, Enhanced Multilevel, Delta-Sigma, Audio, Digital-To-Analog ConverterSATYAM NAIDUNo ratings yet

- DA-20mkII TECHDOCDocument2 pagesDA-20mkII TECHDOCAbdalhakeem Al turkyNo ratings yet

- 114 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionDocument25 pages114 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionLéo TecladistaNo ratings yet

- 4 Adc/8 Dac With PLL, 192 KHZ, 24-Bit Codec Ad1939: Features General DescriptionDocument32 pages4 Adc/8 Dac With PLL, 192 KHZ, 24-Bit Codec Ad1939: Features General Descriptionsuan kwang TanNo ratings yet

- High-Performance 32-bit Mobile Audio DACDocument2 pagesHigh-Performance 32-bit Mobile Audio DACivo radoichevNo ratings yet

- Crystalclear Single Chip Audio System: General DescriptionDocument110 pagesCrystalclear Single Chip Audio System: General DescriptionGregNo ratings yet

- Crystal Clear AdvancedDocument114 pagesCrystal Clear AdvancedraiksonNo ratings yet

- STA308A: Multichannel Digital Audio Processor With DDX™Document46 pagesSTA308A: Multichannel Digital Audio Processor With DDX™Milka RamirezNo ratings yet

- Data Sheet: TDA9615HDocument44 pagesData Sheet: TDA9615HCLAUDIONORMENDESNo ratings yet

- 101 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionDocument24 pages101 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionGilbertoAdonayGutierrezNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : STA308ADocument63 pagesObsolete Product(s) - Obsolete Product(s) : STA308AJorgeNo ratings yet

- CS42448 Audio DAC ADCDocument66 pagesCS42448 Audio DAC ADCQuinta EspNo ratings yet

- Ak4113 (Spdif In)Document49 pagesAk4113 (Spdif In)slobodan.jovanovic.jaNo ratings yet

- pcm1794 PDFDocument30 pagespcm1794 PDFSunghwan ShinNo ratings yet

- 8-Channel Dac With PLL and Differential Outputs, 192 KHZ, 24 BitsDocument28 pages8-Channel Dac With PLL and Differential Outputs, 192 KHZ, 24 BitsIvan AlyaevNo ratings yet

- ES9038PRO Datasheet v3.7Document59 pagesES9038PRO Datasheet v3.7edgarNo ratings yet

- HTTPSWWW - Micro Semiconductor - Hudatasheet97 AK4628AVQ PDFDocument42 pagesHTTPSWWW - Micro Semiconductor - Hudatasheet97 AK4628AVQ PDFPoon Electronic Training CentreNo ratings yet

- PCM1710U: Features DescriptionDocument17 pagesPCM1710U: Features DescriptionFetrian IvanNo ratings yet

- Obsolete: Ad1853 Stereo, 24-Bit, 192 KHZ, MultibitDocument16 pagesObsolete: Ad1853 Stereo, 24-Bit, 192 KHZ, MultibitLan NgocNo ratings yet

- PCM 1716Document14 pagesPCM 1716Phạm Văn BằngNo ratings yet

- PCM1716E and PCM1716E 2KDocument15 pagesPCM1716E and PCM1716E 2KSergiu CretuNo ratings yet

- Cs5330a 31aDocument16 pagesCs5330a 31aiskarupNo ratings yet

- Amc Dac8Document3 pagesAmc Dac8googleheadNo ratings yet

- AK4342ENDocument43 pagesAK4342ENDamnLostNo ratings yet

- TAS5727 25-W Digital Audio Power Amplifier With EQ and DRC: 1 FeaturesDocument70 pagesTAS5727 25-W Digital Audio Power Amplifier With EQ and DRC: 1 Featuressergey7205No ratings yet

- TAS5727Document73 pagesTAS5727Дмитрий КопышевNo ratings yet

- Tda 8425Document24 pagesTda 8425vali dNo ratings yet

- Tpa6404 q1Document12 pagesTpa6404 q1siogNo ratings yet

- WM 8770Document52 pagesWM 8770ha haihaNo ratings yet

- ES8396Document13 pagesES8396Luis PerezNo ratings yet

- Key Features: Electronics and ConnectorsDocument2 pagesKey Features: Electronics and ConnectorsIrvanda ENVIOUSNo ratings yet

- Practical Applications Circuits HandbookFrom EverandPractical Applications Circuits HandbookRating: 5 out of 5 stars5/5 (1)

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Document16 pagesCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyNo ratings yet

- Audio Tda8567q Spec enDocument20 pagesAudio Tda8567q Spec envetchboyNo ratings yet

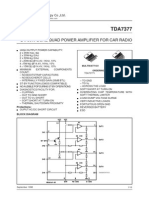

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDocument10 pages2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNo ratings yet

- 4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionDocument12 pages4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- Audio Tda8510j Spec enDocument16 pagesAudio Tda8510j Spec envetchboyNo ratings yet

- Audio Tda8569q Spec enDocument20 pagesAudio Tda8569q Spec envetchboyNo ratings yet

- Audio Tda8567q Spec enDocument20 pagesAudio Tda8567q Spec envetchboyNo ratings yet

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDocument10 pages4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- Tda 7269aDocument7 pagesTda 7269aAlexa DanNo ratings yet

- Tda 7313Document15 pagesTda 7313jordachadiNo ratings yet

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocument9 pagesTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNo ratings yet

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocument13 pages120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNo ratings yet

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDocument14 pagesDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyNo ratings yet

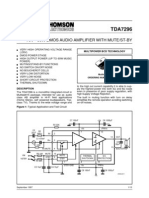

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDocument14 pagesDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyNo ratings yet

- Tda 7296Document14 pagesTda 7296Mayra GonzálezNo ratings yet

- Amplificador 20W RMS TDA2003 Con Placa PCBDocument15 pagesAmplificador 20W RMS TDA2003 Con Placa PCBEnya Andrea Ribba Hernandez100% (5)

- Tda7294 PDFDocument16 pagesTda7294 PDFRoger NunesNo ratings yet

- Tda 7265 2 x25 WDocument12 pagesTda 7265 2 x25 WJavier CanaviriNo ratings yet

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocument18 pagesTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyNo ratings yet

- 30W Bridge Car Radio Amplifier: DescriptionDocument10 pages30W Bridge Car Radio Amplifier: DescriptionvetchboyNo ratings yet

- TDA 2822M CircuitoDocument11 pagesTDA 2822M CircuitoDATA24No ratings yet

- Low Power Quad Operational Amplifiers: LM124 LM224 - LM324Document13 pagesLow Power Quad Operational Amplifiers: LM124 LM224 - LM324vetchboyNo ratings yet

- TDA1554Q 44W Audio AmplifierDocument11 pagesTDA1554Q 44W Audio Amplifiersava7698No ratings yet

- Tda 2004Document11 pagesTda 2004Diana Belen Rodriguez HernandezNo ratings yet

- 10W Car Radio Audio Amplifier: DescriptionDocument11 pages10W Car Radio Audio Amplifier: DescriptionvetchboyNo ratings yet

- Audio Tda2002 Spec enDocument2 pagesAudio Tda2002 Spec envetchboyNo ratings yet

- Audio Tas5100a Spec enDocument15 pagesAudio Tas5100a Spec envetchboyNo ratings yet

- Description: Angus Electronics Company LimitedDocument9 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- STK442-110 70W Audio Power Amplifier SpecificationsDocument4 pagesSTK442-110 70W Audio Power Amplifier SpecificationsIvan AsimovNo ratings yet

- Description: Angus Electronics Company LimitedDocument13 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- Ad5280 5282Document10 pagesAd5280 5282diorginer silvaNo ratings yet

- LTM4700 PDFDocument126 pagesLTM4700 PDFemilfrancuNo ratings yet

- STR71xF: ARM7TDMI™ 32-Bit MCU With Flash, USB, CAN 5 Timers, ADC, 10 Communications InterfacesDocument78 pagesSTR71xF: ARM7TDMI™ 32-Bit MCU With Flash, USB, CAN 5 Timers, ADC, 10 Communications Interfacesdaniel_cirlan_2No ratings yet

- MAX14830 Evaluation KitDocument15 pagesMAX14830 Evaluation KitStef GaudreauNo ratings yet

- Ms 6 ControllerDocument16 pagesMs 6 ControllerQuiteNo ratings yet

- Pmodad2 RMDocument2 pagesPmodad2 RMsergioNo ratings yet

- Programming Cable Users GuideDocument13 pagesProgramming Cable Users GuideSahal AhammedNo ratings yet

- Simulation For Iot Based Smart Traffic Control System For Emergency VehiclesDocument44 pagesSimulation For Iot Based Smart Traffic Control System For Emergency VehiclesJeba JinilNo ratings yet

- MB85RC64TA: 64 K (8 K 8) Bit I CDocument28 pagesMB85RC64TA: 64 K (8 K 8) Bit I CRohit MoreNo ratings yet

- Electronic Protection To Exam Paper Leakage IJERTV2IS50588Document7 pagesElectronic Protection To Exam Paper Leakage IJERTV2IS50588AMal MpNo ratings yet

- Datasheet DT11 SensorDocument12 pagesDatasheet DT11 SensorYuwono Marta DinataNo ratings yet

- Bosch SensortechDocument2 pagesBosch SensortechGkou DojkuNo ratings yet

- SC 3035Document33 pagesSC 3035Mr DungNo ratings yet

- CMPS03Document7 pagesCMPS03Đặng Xuân HồngNo ratings yet

- I 2 CDocument16 pagesI 2 CelumalaianithaNo ratings yet

- CV3393CH O 11 Specification V1.0Document22 pagesCV3393CH O 11 Specification V1.0Красимир КостадиновNo ratings yet

- Data Sheet of RL508 FM TunerDocument20 pagesData Sheet of RL508 FM Tunerapi-432313169No ratings yet

- Raspberry Pi As A Sensor Web Node For Home AutomationDocument19 pagesRaspberry Pi As A Sensor Web Node For Home AutomationDavid GhisaysNo ratings yet

- Computer Multitasking Real-Time ComputingDocument3 pagesComputer Multitasking Real-Time ComputingAlazar DInberuNo ratings yet

- IES Sample MCQ-01Document12 pagesIES Sample MCQ-0132 shreya singhNo ratings yet

- Kenwood KDC-MP228 - MP2028 - MP3029 - MP4029Document36 pagesKenwood KDC-MP228 - MP2028 - MP3029 - MP4029gamercriolloNo ratings yet

- Basic Operations With EEPROM Using Arduino and ConnDuino - ConnDuino ProjectsDocument19 pagesBasic Operations With EEPROM Using Arduino and ConnDuino - ConnDuino Projectsbrahim100% (1)

- Question Bank-1913104-Design of Embedded SystemsDocument12 pagesQuestion Bank-1913104-Design of Embedded SystemsHasib Al-ariki100% (1)

- Learning Internet of Things Sample ChapterDocument31 pagesLearning Internet of Things Sample ChapterPackt Publishing100% (1)

- B01N8V3UEZDocument96 pagesB01N8V3UEZEverton Klinger Sousa Silva100% (4)

- FDC2214 DatasheetDocument61 pagesFDC2214 Datasheetshantanu142No ratings yet

- Infratec 1241 (009-103)Document95 pagesInfratec 1241 (009-103)Revi RevildaNo ratings yet

- Bit Guide PosterDocument24 pagesBit Guide PosterDavid FernándezNo ratings yet

- TCM3.2L La 22PFL1234 D10 32PFL5604 78 32PFL5604 77 42PFL5604 77Document67 pagesTCM3.2L La 22PFL1234 D10 32PFL5604 78 32PFL5604 77 42PFL5604 77castronelsonNo ratings yet

- Nexperia Document Brochure ESD-Protection-Applications 022017Document27 pagesNexperia Document Brochure ESD-Protection-Applications 022017NhatNo ratings yet