Professional Documents

Culture Documents

White Paper ImprovingBTSclocking 101531

Uploaded by

ullascsOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

White Paper ImprovingBTSclocking 101531

Uploaded by

ullascsCopyright:

Available Formats

Improving Clock Performance in Base Stations White Paper

Improving Clock Performance in Base Stations

Do w

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

White Paper

by Mark Hiebert and Ben Lake Issue No. 1: June 2011 PMC-Sierra, Inc.

Improving Clock Performance in Base Stations White Paper

Legal Information

Copyright

Copyright 2011 PMC-Sierra, Inc. All rights reserved. The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement. In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

Trademarks

For a complete list of PMC-Sierras trademarks and registered trademarks, visit: http://www.pmc-sierra.com/legal/ Other product and company names mentioned herein may be the trademarks of their respective owners.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

Patents

The technology discussed in this document may be protected by one or more patent grants.

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Improving Clock Performance in Base Stations White Paper

Abstract

As base station architectures shift towards multi-standard, multi-carrier Remote Radio Heads and Active Antenna Modules, system designers are being challenged to reduce cost, power, and area while increasing the number of clocks in the system and still meeting all standards-based requirements. To meet stringent clock specifications, currently deployed systems often include additional filtering or costly discrete clocking components, which is often a sub-optimal tradeoff between system performance and circuit cost, area, and power consumption. A key issue related to accurately specifying clock performance levels is the edge sensitive nature of sampled systems, where a sampled system is defined as any device where the output signal phase alignment is related to the phase of the clock which samples the input signal. ADCs, DACs, LO synthesizer clock inputs and hard-switching mixers are all examples of devices which are sensitive to the noise at the clocks threshold crossing; therefore it is essential to accurately measure the phase noise at the threshold crossing of the clock signal. A result of the sampling process is that aliasing occurs on the clock signal and all of the noise associated with that clock at the threshold crossing. Frequency planning is an important technique to avoid selecting frequencies at which aliased spurs fall into the wanted frequency band. Use of proper measurement techniques such as observing the spectral content of a clock following a high quality limiting amplifier to isolate phase noise at the threshold crossing enables system designers to more accurately account for spurious noise and aliasing effects in sampled systems. In addition, careful phase planning of system clocks can significantly reduce spurious coupling between clocks. This white paper reviews the basic concepts of phase noise, contrasting continuous with discretely sampled phase noise, discusses frequency aliasing, and explores phase planning techniques that aid designers to address high-density clocking requirements in next-generation base station systems. A clocking architecture that utilizes these techniques is finally presented as an example of how the clocking requirements for a 2T2R base station are addressed by a single high-density clocking solution.

About PMC

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

PMC-Sierra, the premier Internet infrastructure semiconductor solution provider, offers its customers technical and sales support worldwide through a network of offices in North America, Europe, Israel and Asia. PMC-Sierra provides semiconductor solutions for Enterprise and Channel Storage, Wide Area Network Infrastructure, Fiber To The Home, and Laser Printer/Enterprise market segments. The Company is publicly traded on the NASDAQ Stock Market under the PMCS symbol. For more information, visit www.pmc-sierra.com.

About the Authors

Mark Hiebert is a Leader in the Mixed Signal Design Group at PMC-Sierra. Ben Lake is a Senior Applications Engineer in the Broadband Wireless Division at PMC-Sierra.

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Improving Clock Performance in Base Stations White Paper

Revision History

Issue No.

1

Issue Date

June 2011

Details of Change

Initial Release.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Improving Clock Performance in Base Stations White Paper

Table of Contents

Legal Information ........................................................................................................................... 2 Copyright ................................................................................................................................. 2 Disclaimer ............................................................................................................................... 2 Trademarks ............................................................................................................................. 2 Patents .................................................................................................................................... 2 Abstract ................................................................................................................................... 3 About PMC .............................................................................................................................. 3

Revision History............................................................................................................................. 4 List of Figures ................................................................................................................................ 6 1 2 3 4 5 6 7 8 9 Introduction ............................................................................................................................. 7 Continuous-Time Phase Noise Defined .................................................................................. 7 Discrete-Time Phase Noise Defined ....................................................................................... 9 Implications of Discrete-Time Phase Noise .......................................................................... 11 Jitter versus Discrete-Time Phase Noise .............................................................................. 13 Clock Signal Evaluation Considerations ............................................................................... 14 Emulating a Clock Receiver .................................................................................................. 17 Clock Phase Alignment ......................................................................................................... 19 Increasing Clock Density to Address Evolving System Requirements ................................. 22

10 Conclusion ............................................................................................................................ 23

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

About the Authors ................................................................................................................... 3

Improving Clock Performance in Base Stations White Paper

List of Figures

Figure 1 Continuous-time Phase Noise......................................................................................... 8 Figure 2 Discrete-time Phase Noise ............................................................................................ 10 Figure 3 Discrete-time Phase Noise Represented as a Continuous-time Process .................................................................................................................... 11 Figure 4 Measured Result of a 153.6MHz Clock with Aliased Spurious Coupling from a nearby 491.52MHz Clock ............................................................................. 12 Figure 5 Clock Signals Containing Modulated Noise ................................................................. 14

Figure 7 Limiting Amplifier Emulating a Clock Input .................................................................... 18 Figure 8 Example Measurement Setup using a Limiting Amplifier ............................................ 18 Figure 9 Clock Phase Alignment Simulation ............................................................................... 20 Figure 10 Spurious Coupling Between Clock Outputs versus Phase Alignment ........................ 21 Figure 11 RRH 4T4R Clocking Example using PM7520 SyntheCLK ......................................... 22

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Figure 6 System Clocks with Amplitude Modulated or Phase Modulated Noise ....................... 16

Improving Clock Performance in Base Stations White Paper

Introduction

Clock phase noise is a topic that has been discussed extensively. A pure sine wave is commonly used in examples to represent the clock with an associated amount of phase noise. However, modern radio systems use advanced digital and analog circuits to sample, create, and synchronize various analog signals. The clock inputs to these devices are often only sensitive to the threshold crossing of the clock signals. This white paper discusses the clock sensitivity of these devices to show that the clock receivers of most devices effectively sample the phase noise at the rising threshold crossings. Considering a clock signal where the clock phase information is only sampled once per cycle challenges some of the traditional assumptions about clock measurement techniques using RF test equipment. The discrete, sampled nature of the clocks phase information detected by these devices has several implications in the system, including aliasing of spurious signals and variation in coupling between signals depending on clock phase alignment. Minimizing these effects on critical clock signals can improve clock performance.

Continuous-Time Phase Noise Defined

Phase noise is the angular error present in periodic signals. For example the sinusoidal signal s (t ) includes a continuous-time phase noise term j noise (t ) .

s (t ) = sin[2pf CLK t + j noise (t )]

The periodic signal is often illustrated as a rotating vector with a rotation frequency of fCLK, where its instantaneous angle is given by 2pf CLK t + j noise (t ) , as shown in Figure 1 below.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Improving Clock Performance in Base Stations White Paper

Figure 1 Continuous-Time Phase Noise

SE ( t

In RF applications, phase noise is often considered a continuous-time process. For example, if an upconverting mixer is implemented as an ideal analog multiplier, and the LO signal is sinusoidal and is defined as having a continuous-time phase noise process. Considering the mathematical representation of an analog upconverting mixer,

s RFOUT (t ) = V IF (t ) V LO sin 2pf LO t + j LO _ noise (t )

it is apparent that the phase noise of the LO signal affects the RF output at any time t. The output of this mixer is dependent on the continuous-time phase noise process. Referring to Figure 1, at every point in the LO signal vectors rotation, a disturbance in the ideal phase of the LO signal directly impacts the characteristics of the output signal, sRFOUT(t). However, if a device is sensitive only to the threshold crossing of a clock signal, this concept of continuous-time phase noise is insufficient. For example, if an upconverting mixer is implemented with an LO amplifier that amplifies and clips its incoming LO signal, the output of the mixer would not be dependent on a continuous-time phase noise process affecting its LO input signal. Ideally, this type of mixer would convert a LO input signal into a clipped signal taking values of +/-1, as illustrated by the mathematical representation of a LO-clipping upconverting mixer:

Do w

s RFOUT (t ) = V IF (t ) sign(V LO sin 2pf LO t + j LO _ noise (t ) )

Where sign( x ) = -1 if x 0 and sign( x ) = 1 if x > 0

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

[ ]

[ ]

2*fCLKt

OI

Improving Clock Performance in Base Stations White Paper

For this type of device, the value of j LO _ noise (t ) only affects the RF output signal at the instants where the LO phase argument 2pf LO t + j LO _ noise (t ) takes values of np . Referring again to Figure 1, only at the points in the LO signal vectors rotation where the vector crosses the horizontal axis does a disturbance in the ideal phase of the LO signal impact the characteristics of the output signal. The fact that the LO-clipping mixer is insensitive to the phase of its LO signal except at distinct points in the LO period has important implications for how we need to think about phase noise to get an accurate picture of its effect on the devices output.

Many real world devices are sensitive to the phase of their clock signal only at threshold crossing points, including: Data converters, such as Digital-to-Analog Converters (DACs) and Analog-to-Digital Converters (ADCs), LO synthesizers which employ a digital phase/frequency detector in the PLL, and Mixers where the LO signal is clipped or hard-switching.

Therefore, almost all major functional blocks within the RF and baseband sections of a base station system are sensitive to phase noise only at discrete moments in each clock cycle, at the threshold crossing of the clock. Consider devices clocked by a sinusoidal signal s (t ) with continuous-time phase noise

s (t ) = sin[2p * f CLK t + j noise (t )]

Since TCLK =

2p * t s (t ) = sin + j noise (t ) TCLK

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

If the device was only sensitive to phase of the clock at the instant it rises through the zero threshold, its clock receiver would detect a clock event every time the phase argument crosses n*2.

2p * t + j noise (t ) = n * 2p TCLK

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

1 f CLK

, the signal can also be written as

Discrete-Time Phase Noise Defined

Improving Clock Performance in Base Stations White Paper

To meaningfully define the phase noise for these devices which are only sensitive to the clock phase during specific instants in the clocks period (e.g. the zero threshold crossing), we must acknowledge that the phase noise is also only detected (or sampled) at these discrete instants. The phase noise detected by this device can be accurately represented as a discrete sequence of samples of the original continuous-time phase noise process. The phase noise of the nth clock period is given by:

j noise [n] @ j noise (nTCLK )

where this relationship is approximate. The phase noise is not sampled at exactly nTCLK because the phase noise process itself disturbs the sampling instant, but this approximation does not affect the following discussion. Continuous-time phase noise and the resultant discrete sequence of phase noise samples are illustrated in the following figure, where the discrete-time phase noise is assumed to be measured at the rising zero threshold crossing.

Figure 2 Discrete-Time Phase Noise

Clock Amplitude, s(t)

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Clock Signal

time

Clock Phase Noise, noise(t) Continuous Time Phase Noise Discrete Time Phase Noise Samples

time noise[4]

noise[0]

noise[1]

noise[2]

noise[3]

noise[5]

Note that the phase noise for the nth clock period is equal to the phase error that impacted the nth rising threshold crossing of the clock, j noise [n] The sequence j noise [n] is the discrete-time . phase noise representation of the original clock signals continuous-time phase noise, as observed at the instants of the clock signals rising edge threshold crossing. It has a sample rate of fCLK if the phase of the clock signal is sensed once per clock cycle.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

We can look at this discrete-time sequence of phase noise measurements as a representation of the phase noise seen by this sampled system. This is shown graphically in Figure 3 below.

10

Improving Clock Performance in Base Stations White Paper

Figure 3 Discrete-Time Phase Noise Represented as a Continuous-Time Process

Clock Amplitude, s(t) time

Clock Signal

Clock Phase Noise, noise(t) Phase Error Discrete Time Phase Noise Samples time noise[0] noise[1] noise[3] noise[4]

The resultant phase noise of each discrete-time sample can be envisioned as constant over each sample period. The information in the samples is limited by the Nyquist bandwidth of the sampling clock.

Implications of Discrete-Time Phase Noise

In sampled systems, system designers are conscious of the implications of moving from the domain of continuous-time signals to sampled signals. For example in an ADC, aliasing occurs when continuous-time signals are sampled: any signal content at frequencies above half the sample frequency, fSAMPLE, will alias into the discrete-time spectrum of the sampled output sequence. The discrete-time Power Spectral Density (PSD) of the sampled values is captured within a frequency band from DC to fSAMPLE/2. Aliasing and Nyquist bandwidth concepts also apply when considering the characteristics of discretely sampled phase noise. Aliasing effects, when considering phase noise as a discrete-time sampled sequence, can be illustrated by considering a 100MHz sinusoidal clock driving a system sensitive only to the rising threshold crossing, but including a continuous-time phase noise process with a frequency of 501MHz:

s (t ) = sin[2pf CLK t + APhN sin( 2p * 501MHz * t )]

The phase noise present in each of the clocks rising threshold crossings is:

j noise [n] @ j noise (nTCLK ) = APhN sin( 2p * 501MHz * n / 100MHz ) = APhN sin( 2p * n * 500MHz / 100MHz + 2p * n * 1MHz / 100MHz ) = APhN sin( 2p * n * 5 + 2p * n * 1MHz / 100MHz ) = APhN sin( 2p * n * 1MHz / 100MHz )

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

noise[2]

noise[5]

11

Improving Clock Performance in Base Stations White Paper

From the above equations, it is apparent that the phase disturbances as observed on the clocks threshold crossings have a periodicity of 1MHz. The 501MHz frequency content in the continuous-time phase noise process aliases to 1MHz when the phase of the clock is only observed at a specific instant of the clock period. A practical example that highlights this aliasing effect is to consider a 153.6MHz clock signal with a nearby 491.52 MHz clock signal coupling on to this clock. If the 153.6MHz clock signals phase is only observed once per clock period, it is nonsensical to define spurious content at 491.52MHz offset in the sequence of discrete-time phase noise samples. 491.52MHz is above the 153.6MHz/2 bandwidth limit for the discrete-time phase noise in this example system. If the 491.52MHz clock signal couples and affects the phase of the 153.6MHz clock signal at the threshold crossings, it would result in a 30.72MHz offset (491.52MHz 4*153.6MHz/2 = 30.72MHz) periodic phase disturbance in the discrete-time phase noise spectrum detected on the 153.6MHz clock signal (after being sampled by the clock input). By using a hard clipping / limiting amplifier to emulate an edge-sensitive clock input and driving it with both a 153.6MHz wanted clock signal and a 491.52MHz unwanted coupled signal, an example of this effect was measured in a lab setup and captured below in Figure 4.

Figure 4 Measured Result of a 153.6MHz Clock with Aliased Spurious Coupling from a nearby 491.52MHz Clock

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

12

Improving Clock Performance in Base Stations White Paper

The above example shows how critical it can be to be aware of aliasing effects when selecting the clock frequencies within a system. Consider another example system where a 153.6MHz ADC clock and a 614.4MHz DAC clock are used. The ADC clock input detects clock edges, meaning that it effectively detects a sequence of discrete-time phase noise samples with a rate of 153.6Msps. All power in this sequence can be displayed in the frequency range DC to 153.6MHz/2 and spurious content at the ADC clocks threshold crossing location will alias down into this frequency range. Therefore any spurious coupling from the DAC clock (614.4MHz mod 76.8MHz = 0) will alias down to DC and have no impact on the phase noise characteristics of the clock information detected by the ADC.

Jitter versus Discrete-Time Phase Noise

When making the transition from continuous-time phase noise to the disturbances in threshold crossing events on a clock signal, the disturbances in the threshold crossing are generally referred to as jitter and are represented in units of time (i.e. seconds). However, in RF applications, representing the clock disturbances as phase noise, measurable in dBc or radians, can be a more appropriate choice of units and terminology; this is true even where the concept of continuous-time phase noise is no longer an accurate representation. Describing phase noise in units of time can be limiting in the context of performance impacts in an RF signal chain. For example, if a LO-clipping RF mixer is clocked by a 1GHz sine wave with threshold crossings that are modulated by 50fs with a frequency of 1MHz,

s RFOUT (t ) = V IF (t ) sign(V LO sin[2p * 1GHz * t + 0.1 * sin(2p * 1MHz * t )])

In this application, it is meaningful to note that the discrete-time phase noise sequence has a 1MHz periodic content with an RMS phase noise power of

2 * p * (1GHz ) * (50 fs ) = 314uRad

which can also be expressed as

20 * log10 (314uRad ) = -70dBc .

Note that the above result is the double sideband phase noise power. The single sideband power, which is more commonly used in lab measurements, is half of that value

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

PowerPhaseNoise _ SSB = -70dBc - 3dB = -73dBc .

It is also important to observe that phase noise power varies with clock frequency, for the same amount of timing jitter. In the above example, if the 1GHz sine wave was replaced with a 100MHz sine wave, the same disturbance would have a phase noise of 31.4uRad and the resultant single sideband phase noise power would be -93dBc. Therefore, it is essential to consider the operating frequency of each clock in the system when defining spurious performance specifications for those clock outputs.

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

13

Improving Clock Performance in Base Stations White Paper

The LO phase modulation power, in radians or dBc, gives specific insight into the spectral purity of the RF output signal. In this application, it is much less meaningful to note that the periodic timing jitter on the clipped LO signal has an RMS level of 50fs. No straightforward insights into the spectral purity of the RF output signal can be derived from this description of the jitter on the clock edge crossings, expressed in units of time. The practicality of using units of radians or dBc to represent phase noise characteristics applies for RF mixers, but also for other clock inputs in an RF signal path, such as ADC/DAC clock inputs or digital phase/frequency detectors in RF PLLs. For this reason, the following discussion will continue to focus on the concept of threshold crossing disturbances as discretetime phase noise, inferring that clock disturbances are represented in units of phase.

Suppose that two identical systems were each clocked by a sinusoidal clock signal, one clock containing amplitude noise Anoise(t) and the other clock containing phase noise j noise (t ) impairments:

2p * t s INPUT 1 (t ) = (1 + Anoise (t )) * sin TCLK

It is important to note that when the continuous-time power spectral densities of these two clock signals are observed, one clock with only phase modulation and one clock with only amplitude modulation, identical spectral power distributions are detected if the modulation power levels are equal. Figure 5 presents an example of similar amounts of amplitude modulated noise and phase modulated noise on the same clock displaying similar power spectral densities.

Figure 5 Clock Signals Containing Modulated Noise

Amplitude Modulated Clock Signal

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Clock Signal Evaluation Considerations

2p * t + j noise (t ) s INPUT 2 (t ) = sin TCLK

Phase Modulated Clock Signal

14

Improving Clock Performance in Base Stations White Paper

In some situations both the amplitude noise and phase noise of a clock signal are relevant. The ideal analog upconverting mixer presented in Section 2 is one of those cases. Conversely, many sampled systems are sensitive to only the clock phase at the threshold crossing of the clock signal. In these sampled systems, the clock signal after the clock receiver can be thought of as a square wave, where the clock receivers output y (t ) depends on the input x(t ) in the manner described below

y (t ) = sign( x(t ) )

Where sign( x ) = -1 if x 0 and sign( x ) = 1 if x > 0

This behavior has been modeled in Matlab, simulating the time domain waveforms, the signals power spectral density, and the resultant phase noise (jitter) of the clock threshold crossings. The simulation results for both a clock waveform containing only amplitude modulation and a clock waveform containing only phase modulation are shown in Figure 6.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

For each clock input signal passing through a receiver such as this, the input clock signal with only amplitude noise would produce no deviations in the clock receivers output signal because the amplitude noise doesnt affect the position of the signals threshold crossing. However, the input clock signal with only phase noise would produce deviations in the clock receivers output signal because the phase noise j noise (t ) shifts the location of the signals zero threshold crossing.

15

Improving Clock Performance in Base Stations White Paper

Figure 6 System Clocks with Amplitude Modulated or Phase Modulated Noise

Amplitude Modulated Clock Signal

Phase Modulated Clock Signal

In order to illustrate the fundamental difference between these sources of noise, the amount of modulation used in the above simulation is much larger than the noise in real systems. Measuring the spectral content of the actual clock signals on a continuous-time instrument will show identical results, but the measurement provides no insight into the power spectrum of the phase information on the clock at the threshold crossings. Analyzing the power spectral density of the discrete-time samples of clock phase at the threshold crossings (jitter) confirms that an ideal clock buffer will only pass through noise that affects the phase of the clock threshold crossings.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

16

Improving Clock Performance in Base Stations White Paper

Now that we have established that we are primarily concerned with the clock phase noise only at the threshold crossing in sampled systems, it is essential to use techniques in the laboratory that can effectively measure that phase noise in isolation and then develop solutions to minimize those specific sources of noise. Emulating a system that is sensitive to only the clock phase at the threshold crossing using a high gain limiting amplifier is an effective way to enable continuous-time test equipment to effectively see the same types of phase noise that are encountered in these sampled systems.

Emulating a Clock Receiver

A high-gain, high-performance buffer device, or limiting amplifier, can be used to condition the clock signal before measurement. Passing the clock signal through a limiting amplifier effectively clips the clock signal such that amplitude modulation is removed but phase modulation near the threshold crossing is preserved. The limiting amplifier closely mimics the functionality of the clock input of a sampled system, shown below in Figure 7, enabling precise measurement of phase noise and spurious coupling due to phase modulation on a continuoustime measurement instrument, such as a Spectrum Analyzer. The spectral content at the output of this limiting amplifier is representative of the spectral content in the discrete-time samples of phase noise that would be detected by a device that is sensitive to only the clock threshold crossing.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Measurement instruments such as Spectrum Analyzers are continuous-time instruments and therefore directly measuring a clock signal will not be indicative of the performance when that clocks phase information is sampled by a system which is only sensitive to the clock threshold crossing. In order to determine the impact of clock impairments for systems that reject amplitude-modulated noise on clock signals and are sensitive to phase-modulated noise at the clock threshold crossing, it is necessary to use a clock measurement methodology that behaves in a similar manner.

17

Improving Clock Performance in Base Stations White Paper

Figure 7 Limiting Amplifier Emulating a Clock Input

It is essential to choose a high-performance limiting amplifier with a high bandwidth and low noise characteristics so that the clock signal being measured is not significantly degraded. PMCSierra has designed a limiting amplifier test board using the clock input buffer of a PM7520 SyntheCLK device. An example of a limiting amplifier being used to measure the spurious content of the clock source at the clock threshold crossings is shown in Figure 8.

Figure 8 Example Measurement Setup using a Limiting Amplifier

PM7520 SyntheCLK or other high-performance clock source

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Differential Limiting Amplifier

n

Spectrum Analyzer

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

18

Improving Clock Performance in Base Stations White Paper

The limiting amplifier enables measurement of spurious coupling and aliasing effects equivalent to the sampling process that occurs at the clock input of sampled systems. 1 If the clock source was connected directly to the Spectrum Analyzer, then the measurement would report the average spectral content of the clock signal, including spectral content that occurs away from the threshold crossing; there would be no way to discriminate between the effects that disturb the threshold crossing (phase modulated noise), and those that do not (amplitude noise). Note that the limiting amplifier also provides the required differential to single-ended conversion, which ensures that common-mode noise is removed, enabling an accurate measurement with single-ended test equipment while still providing the expected differential termination for the clock output being measured. This is an appropriate measurement technique because typically a differential clock receiver would be used in the actual application.

System clocks generally have very fast edge rates and appear very similar to square waves. Thus, signal disturbances near the threshold crossing will occur as phase modulated noise, while disturbances away from the threshold crossing will occur as amplitude modulated noise. As discussed in Section 6, noise that does not affect the clock signal near the threshold crossing will not be detected at the clock receiver. Therefore, if we consider the example of a clocking device with multiple clock outputs, high-speed switching transients caused by other clock outputs can couple onto a clock output that has very strict phase noise requirements. It is possible to minimize the phase disturbance to the threshold crossing of the desired output clock by adjusting the phases of the other output clocks. Figure 9 shows a simulation demonstrating a lower frequency clock coupling onto a higher frequency clock with the phase of the lower frequency clock being shifted in phase. Note that the right side of the figure shows the discrete-time Power Spectral Density (PSD) of this clock signal, where phase is measured only at the threshold crossing.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

Note that an ideal limiting amplifier would include a divide by 2 circuit internally, such that only the rising edge is measured.

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

Clock Coupling Depends on Phase Alignment

19

Improving Clock Performance in Base Stations White Paper

Figure 9 Clock Phase Alignment Simulation

This effect in the simulation is quite dramatic, but in real systems the effect of phase alignment is much more complex. Multiple interfering clock sources, Printed Circuit Board (PCB) trace propagation delays, trace impedance mismatches at various frequencies, etc. all cumulate into a measured effect that correlates closely to theory, but is not as predictable. Consider a practical example using the PMC-Sierra PM7520 SyntheCLK device configured for a 76.8 MHz clock output and 153.6 MHz clock output. The 153.6 MHz clock output is measured for spurious coupling from the 76.8 MHz clock output, and the 153.6 MHz output is adjusted through 16 possible output phase alignments to find the best isolation between clock outputs, is shown below in Figure 10.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

20

Improving Clock Performance in Base Stations White Paper

Figure 10 Spurious Coupling Between Clock Outputs versus Phase Alignment

/2

3/2

The PMC-Sierra PM7520 SyntheCLK device features 30 clock outputs where each output has a deterministic phase relationship to the other outputs and independent, glitchless phase control. This enables system designers to conveniently optimize phase alignment without the need for complex routing or additional circuitry to account for multiple clock buffers. Optimizing the phase alignment of all clock outputs within a given frequency plan can significantly improve the isolation between various clock outputs, resulting in better spurious performance on critical system output clocks such as transmit path DACs and receive path ADCs. 2

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

Please contact PMC-Sierra Applications Support (apps@pmc-sierra.com) for phase-optimized performance results for specific frequency plans.

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

21

Improving Clock Performance in Base Stations White Paper

Increasing Clock Density to Address Evolving System Requirements

The shift in Base Station architecture towards multi-standard, multi-carrier Remote Radio Heads and Active Antenna Modules is dramatically increasing the number of high-performance clocks required per system. PMC-Sierras PM7520 SyntheCLK addresses this need by providing a single, highly-integrated solution with a 30-output dual-PLL clock synthesizer. SyntheCLK features include: Jitter attenuation of the recovered clock;

30 low phase noise clock outputs, each with independent frequency control, output phase control, and glitch-free synchronization.

An example of the PM7520 SyntheCLK being used in a 4 Transmit 4 Receive (4T4R) Remote Radio Head application is shown in Figure 11.

Figure 11 RRH 4T4R Clocking Example using PM7520 SyntheCLK

Tx DAC

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

4 4

A programmable system clock synthesizer unit capable of providing output clocks up to 1.583 GHz;

DAC

Tx LO Tx Observation ADC

ADC

Observation LO

SerDes

SerDes Recovered Clock

Rx ADC

ADC

Rx LO Envelope Tracking DAC

4 4 4

DAC

VCXO

FPGA / ASIC

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

22

Improving Clock Performance in Base Stations White Paper

10

Conclusion

Clock signals can include amplitude-modulated noise or phase-modulated noise. The continuous-time representation of the power spectral densities of signals with either of these impairments can be indistinguishable. When a clock signal is sampled by an input that is only sensitive to the threshold crossing, the phase noise is also sampled at those threshold crossing instants; noise on the clock signal at all frequencies above fSAMPLE/2 can alias down into this region. Careful frequency planning can help to ensure that no unwanted signals will alias onto a critical clock signal. Measurement techniques that analyze the clock perturbations at the threshold crossing give a more accurate representation of the phase noise in the resultant sampled signal. Simulations and lab observations match the theory that a limiting amplifier closely mimics the functionality of a clock input. By removing the amplitude modulated noise from a clock signal and by being sensitive only to the threshold crossing position of the input signal, the limiting amplifier enables measurement of only the phase noise at the threshold crossing. The limiting amplifier allows system designers to measure and analyze the aliasing effects that are seen in sampled systems. The sensitivity of sampled systems to phase modulation, but not to amplitude modulation, suggests that phase optimization of key clocks can significantly reduce spurious coupling between output clocks, thereby improving the performance of the clock signals. This enables system designers to deliver high-performance, high-density base station architectures which are clocked from a single device. PMC-Sierras PM7520 SyntheCLK provides the required functionality and high-level of integration to enable next generation base station designs that reduce circuit cost, area, and power consumption while meeting stringent performance requirements.

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

23

Improving Clock Performance in Base Stations White Paper

Contacting PMC-Sierra

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7 Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200 Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: http://www.pmc-sierra.com

Proprietary and Confidential to PMC-Sierra, Inc., and for its customers' internal use. Document No.: PMC-2103003, Issue 1

Do w

nl o on ade Th d [ ur co sd nt ay rol , 0 led 9M ] ay by U , 2 lla 01 s K 3 04 um :4 ar 0: 24 of R PM ak o

24

You might also like

- NYT - Why Sanders Will Probably Win The Nomination PDFDocument3 pagesNYT - Why Sanders Will Probably Win The Nomination PDFullascsNo ratings yet

- Every Saturdays, 2 - 4Pm - Focus On The Family SingaporeDocument1 pageEvery Saturdays, 2 - 4Pm - Focus On The Family SingaporeullascsNo ratings yet

- Ntttechnical PDFDocument62 pagesNtttechnical PDFullascsNo ratings yet

- House Brand ProductsDocument13 pagesHouse Brand ProductsullascsNo ratings yet

- LoRaWAN Specification 1R0Document82 pagesLoRaWAN Specification 1R0AnindyaSahaNo ratings yet

- Oscillator FundamentalsDocument27 pagesOscillator FundamentalsullascsNo ratings yet

- SMA Quarterly Updates Highlights Events, COVID ResponseDocument6 pagesSMA Quarterly Updates Highlights Events, COVID ResponseullascsNo ratings yet

- JnaniDocument16 pagesJnaniullascsNo ratings yet

- Gateway Block DiagramDocument1 pageGateway Block DiagramullascsNo ratings yet

- Pranayama Rahasya English FlyerDocument2 pagesPranayama Rahasya English FlyerullascsNo ratings yet

- TABE InvitationDocument1 pageTABE InvitationullascsNo ratings yet

- Prasnopanishad - MalayalamDocument0 pagesPrasnopanishad - Malayalamzkaria_johnNo ratings yet

- Water Quality Monitoring SlidesDocument6 pagesWater Quality Monitoring SlidesullascsNo ratings yet

- Synch Ethernet v1Document2 pagesSynch Ethernet v1ullascsNo ratings yet

- 5G Factsheet V2Document3 pages5G Factsheet V2ullascsNo ratings yet

- Anue 3500 Qrs - 0Document2 pagesAnue 3500 Qrs - 0ullascsNo ratings yet

- Base Station Solutions: Icon Icon IconDocument2 pagesBase Station Solutions: Icon Icon IconullascsNo ratings yet

- GNSS Positioning Solutions: Technology Expertise and Standards CompliantDocument2 pagesGNSS Positioning Solutions: Technology Expertise and Standards CompliantullascsNo ratings yet

- Blu LogDocument1 pageBlu LogullascsNo ratings yet

- Blugrpah BrochureDocument2 pagesBlugrpah BrochureullascsNo ratings yet

- BluSense Energy & Environment Monitoring SolutionDocument1 pageBluSense Energy & Environment Monitoring SolutionullascsNo ratings yet

- GNSS Based Synchronisation PDFDocument2 pagesGNSS Based Synchronisation PDFullascsNo ratings yet

- Passport Application Form PDFDocument4 pagesPassport Application Form PDFullascsNo ratings yet

- Anue 3500 Qrs - 0Document2 pagesAnue 3500 Qrs - 0ullascsNo ratings yet

- 5G Vision White Paper Outlines Immersive Services and IoTDocument16 pages5G Vision White Paper Outlines Immersive Services and IoTteomondoNo ratings yet

- AN420Document16 pagesAN420ullascsNo ratings yet

- AV Policy Guidance PDFDocument116 pagesAV Policy Guidance PDFTechCrunch100% (1)

- Base Station Solutions: Icon Icon IconDocument2 pagesBase Station Solutions: Icon Icon IconullascsNo ratings yet

- Draft Finn Detnet Architecture 01Document23 pagesDraft Finn Detnet Architecture 01ullascsNo ratings yet

- Packet Network Sync v1Document2 pagesPacket Network Sync v1ullascsNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- FWC143 Mini Hi-Fi System: Downloaded From Manuals Search EngineDocument23 pagesFWC143 Mini Hi-Fi System: Downloaded From Manuals Search EngineAndré LeftNo ratings yet

- Chebyshev Analog FilterDocument24 pagesChebyshev Analog FilternguyenphuonghuyNo ratings yet

- Ic7410 Ts590 Ft950 AnalysisDocument20 pagesIc7410 Ts590 Ft950 AnalysisLoco Soy Loco SoyNo ratings yet

- Mcq-For-Dip With SolutionDocument55 pagesMcq-For-Dip With SolutionAkkilNo ratings yet

- GuitarDocument34 pagesGuitarbendeniNo ratings yet

- Digital Signal Processing (EE-394) : Practical Work BookDocument13 pagesDigital Signal Processing (EE-394) : Practical Work BookHermain Fayyaz KarimNo ratings yet

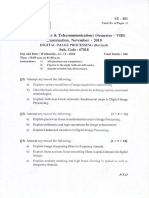

- Se 481 - Digital Image Processing - Sem Viii - Dec 2018 PDFDocument2 pagesSe 481 - Digital Image Processing - Sem Viii - Dec 2018 PDFMonika DhembareNo ratings yet

- EC 402 SignalSystems NotesDocument45 pagesEC 402 SignalSystems NotesAnkit KapoorNo ratings yet

- Noise Reduction For Periodic Signals Using High-Resolution Frequency AnalysisDocument19 pagesNoise Reduction For Periodic Signals Using High-Resolution Frequency Analysismahdi cheginiNo ratings yet

- Digital Image Processing Elective 1Document3 pagesDigital Image Processing Elective 1Tripathi VinaNo ratings yet

- 2-Iteration Bound PDFDocument3 pages2-Iteration Bound PDFmasoudNo ratings yet

- SLS Laboratory APU2F1908 PDFDocument5 pagesSLS Laboratory APU2F1908 PDFLimpei chinNo ratings yet

- High Performance JPEG Steganography Using Complementary Embedding Strategy PDFDocument11 pagesHigh Performance JPEG Steganography Using Complementary Embedding Strategy PDFManiNo ratings yet

- 5ETC03 DSP SyllabusDocument1 page5ETC03 DSP SyllabusfesajaNo ratings yet

- Class-D LC Filter Design: Application ReportDocument27 pagesClass-D LC Filter Design: Application ReportSunghoonie Kang100% (1)

- Sound Mixer TutorialsDocument11 pagesSound Mixer Tutorialssmithesh govindan c e100% (2)

- Icramet RDGAN Rep3Document6 pagesIcramet RDGAN Rep3Tri WinotoNo ratings yet

- DSP Objective QuestionsDocument3 pagesDSP Objective Questionsannam karthikNo ratings yet

- LG Power Supply Reference GuideDocument29 pagesLG Power Supply Reference GuideOrlando Jose PascuaNo ratings yet

- EPWTDocument5 pagesEPWTyazeed7079875No ratings yet

- Lec15 Histogram EqualizationDocument19 pagesLec15 Histogram EqualizationIqrakhanNo ratings yet

- Project 7 Compressor Limiter p91-95Document5 pagesProject 7 Compressor Limiter p91-95Engkiong GoNo ratings yet

- Meridian MLPDocument11 pagesMeridian MLPmflemi4No ratings yet

- Exam 2 Cheat SheetDocument3 pagesExam 2 Cheat SheetMac JonesNo ratings yet

- EEE415 Digital Image Processing: Frequency Domain FilteringDocument50 pagesEEE415 Digital Image Processing: Frequency Domain FilteringFAISAL NAWABNo ratings yet

- Analysis On Output LC Filter of PWM InverterDocument6 pagesAnalysis On Output LC Filter of PWM InverterKiran Kumar100% (1)

- UNIT IV Part B (Questions With Answer)Document5 pagesUNIT IV Part B (Questions With Answer)Abinaya TNo ratings yet

- ELE 301: Signals and Systems: Prof. Paul CuffDocument45 pagesELE 301: Signals and Systems: Prof. Paul CuffdioumbNo ratings yet

- Lect08 PDFDocument53 pagesLect08 PDFSandeepNo ratings yet

- Designing Digital Filter Banks Using WaveletsDocument11 pagesDesigning Digital Filter Banks Using WaveletsAnand MattadNo ratings yet