Professional Documents

Culture Documents

Cap 12

Uploaded by

Carlos PerezCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cap 12

Uploaded by

Carlos PerezCopyright:

Available Formats

CAP 12 XlLlNX SPARTAN-3 SPECIFIC MEMORY

Introduccin: Un sistema digital requiere frecuentemente la memoria para el almacenamiento. Para facilitar esta necesidad, la mayora de los dispositivos FPGA contienen mdulos de memoria integrados dedicados. Mientras que estos mdulos no pueden sustituir a los dispositivos de memoria externos masivas, que son tiles para aplicaciones que requieren una memoria pequea o de tamao intermedio. Aunque la estructura interna bsica de mdulos de memoria es similar, hay muchas diferencias sutiles en sus interfaces 110. Por lo general, es difcil para el software de sntesis para extraer las caractersticas deseadas del cdigo e inferir un mdulo de memoria juego de la biblioteca dispositivo subyacente. En Xilinx ISE, podemos utilizar instanciacin HDL, el programa Core Generator, o la plantilla de inferencia HDL comportamiento para incorporar un mdulo de memoria integrado en un diseo. La tercera es semi-independiente del dispositivo y utilizar este mtodo en este libro. En este captulo, examinaremos brevemente los mdulos de memoria Spartan-3 y los dos primeros mtodos y proporcionar descripciones detalladas de varias plantillas clave HDL del comportamiento.

12.2 memoria incorporada de DISPOSITIVO SPARTAN 3 12.2.1 Informacin general Hay dos tipos de memoria integrada en un dispositivo de Spartan - 3 : RAM distribuida y bloque de memoria RAM . Una memoria RAM distribuida se construye a partir de tabla de consulta de la celda lgica ( LUT ) . La LUT se puede configurar como una memoria RAM de 16 - por - 1 sncrona , y mltiples tablas de bsqueda puede ser en cascada para formar un mdulo de memoria ms amplia y ms profunda . El Spartan- 3 XC3S200 dispositivo de la placa S3 puede proporcionar hasta 30 K bits de memoria distribuida , que es pequeo en comparacin con un bloque de RAM o la memoria externa. Adems, puesto que la memoria RAM distribuida utiliza las clulas de la lgica , que compite por los recursos con la lgica normal . Por lo tanto , es factible slo para aplicaciones que requieren relativamente pequea de almacenamiento . Un bloque de memoria RAM es un mdulo de memoria especial incorporado en un dispositivo FPGA y se separa de las clulas de la lgica regulares . Se puede considerar como una SRAM rpido envuelto por una , interfaz configurable sncrono . Cada bloque consta de RAM de 16K ( 214 ) bits de datos , adems de los bits de paridad 2K opcionales. Se puede organizar en diferentes anchuras , de 16K por 1 ( es decir , 214 por 2 ' ) a 512 por 32 ( es decir , 2 ' por 25 ) . El XC3S200 dispositivo Spartan- 3 tiene 12 bloques de reciente adhesin, por un total de bits

de datos de 172K . Estos RAM bloque puede ser utilizado para aplicaciones de tamao intermedio , tales como una FIFO , una gran tabla de consulta , o una memoria local de tamao intermedio . En comparacin, los chips de SRAM externas de la junta S3 tienen una capacidad de bits de 8M . RAM Tanto la RAM y el bloque distribuido ya estn " envueltos " con una sincrnica es necesaria la interfaz, y por lo tanto no hay circuito controlador de memoria adicional. Ellos son muy flexibles y pueden ser configurados para llevar a cabo el acceso de un solo y de doble puerto y para admitir varios tipos de almacenamiento en bfer y la hora de esquemas . Discusin detallada est ms all del alcance de este libro . Slo examinamos varias configuraciones comunes, como una memoria RAM sncrona de un solo puerto , una RAM de doble puerto sncrono , y una ROM en la Seccin 12.4 . 12.2.2 Comparacin El dispositivo Spartan-3 y la tabla S3 ofrecen varias opciones para los elementos de almacenamiento. Es una buena idea para tener en cuenta las capacidades relativas de estas opciones: FFs de XC3S200 (de registros): unos bits de 4.5K, incrustados en celdas lgicas y 110 buffers de memoria RAM distribuida de XC3S200 30 mil pedazos, construido a partir de las clulas de la lgica Bloque de la memoria RAM de XC3S2OO: 172K bits configurado como doce mdulos 16K bits Externa SRAM: Bits 8M, configurados como dos 256K por 16 chips SRAM Esto nos ayuda a decidir qu opcin es la ms adecuada para una aplicacin en cuestin.

12.3 MTODO PARA INCORPORAR LOS MDULOS DE MEMORIA Aunque los mdulos de memoria tienen una estructura interna similar, hay muchas diferencias sutiles en sus interfaces, tales como el nmero de puertos de lectura y escritura, en la hora del esquema, los datos y la direccin de buffering, habilitar y restablecer las seales y los valores iniciales. A pesar de que es posible describir los comportamientos deseados en el cdigo del mdulo de HDL, el software de sntesis puede o no reconoce la intencin del diseador. Por lo tanto, el cdigo de HDL no siempre puede inferir el mdulo de memoria adecuada y, normalmente, no es porttil. En Xilinx ISE, hay tres mtodos para incorporar un mdulo de memoria integrada en un diseo: instanciacin HDL El programa Core Generator La plantilla de inferencia HDL comportamiento

Los dos primeros son especficos para los dispositivos de Xilinx y el tercero es un semiindependiente del dispositivo Descripcin de comportamiento. Debido a la claridad de la descripcin de comportamiento, se utiliza el tercer mtodo en este libro. Nosotros proveemos una breve descripcin de los tres mtodos descritos en esta seccin.

12.3.1 Mdulo de memoria a travs de la creacin de instancias de componentes HDL

Hemos utilizado la creacin de instancias de componentes HDL en muchos ejemplos de diseos anteriores para incluir prediseado mdulos o para crear una jerarqua. Crear instancias de un mdulo de memoria Xilinx es similar, excepto que no hay una descripcin HDL para el cuerpo arquitectura. Debemos comprobar el manual para saber el nombre del mdulo exacto y los parmetros asociados y el puerto 110 definiciones. Este es un proceso tedioso y es particularmente propenso a errores para mdulos de memoria debido al gran nmero de configuraciones y opciones. El cdigo de instancias para muchos componentes de Xilinx se puede obtener directamente a partir de ISE por seleccionando Editar + plantillas de idiomas. Los siguientes son segmentos de un 16K-por-1 de doble puerto RAM:

Aunque el cdigo est disponible, debemos estudiar cuidadosamente el manual para encontrar el componente correcto y los parmetros de configuracin apropiados. 12.3.2 Mdulo de memoria a travs de Core Generator Para simplificar el proceso de creacin de instancias, Xilinx proporciona un programa de utilidad, conocida como ncleo generador (CoreGen), para generar componentes de Xilinxespecficos. Esta utilidad se puede invocar desde el entorno ISE seleccionando Proyecto + Fuente Nueva. Despus de la Fuente Nueva Aparece el dilogo de Asistente, seleccionamos IP (CoreGen y arquitectura Asistente) para invocar el programa CoreGen. El programa gua a los usuarios a travs de una serie de preguntas y genera archivos varios. El archivo con la extensin XCO. Es un archivo de texto que contiene la informacin necesaria para construir el componente de memoria deseada. El archivo con la extensin v. Contiene el cdigo de "contenedor" para los fines de simulacin. Este archivo no se puede usar para crear una instancia del componente deseado y se pasa por alto durante el proceso de sntesis. Aunque el uso del programa CoreGen es ms conveniente que la instanciacin HDL directa, que no est dentro del marco de HDL y puede conducir a un problema de compatibilidad cuando un diseo no se realiza en el entorno Xilinx ISE.

You might also like

- DO Optical TechnologyDocument20 pagesDO Optical TechnologyCarlos PerezNo ratings yet

- Instructor CKB Fabián CuencaDocument13 pagesInstructor CKB Fabián CuencaCarlos PerezNo ratings yet

- Tecnologias CelularesDocument2 pagesTecnologias CelularesCarlos PerezNo ratings yet

- Taekwondo Fundamentos PDFDocument24 pagesTaekwondo Fundamentos PDFAlbert Lestat GarciaNo ratings yet

- Uplink Reference Signals: RS Signal Sequence GenerationDocument7 pagesUplink Reference Signals: RS Signal Sequence GenerationCarlos PerezNo ratings yet

- Comando Ss QLDocument1 pageComando Ss QLCarlos PerezNo ratings yet

- Ensayo - Normalizacion de Bases de Datos PDFDocument6 pagesEnsayo - Normalizacion de Bases de Datos PDFCharlie BrownNo ratings yet

- SQL PlusDocument34 pagesSQL PlusLuis Alejandro Curay ValdiviezoNo ratings yet

- Divisor de Tensión (Actividad) - 2Document6 pagesDivisor de Tensión (Actividad) - 2Edwin Paucara CondoriNo ratings yet

- Tabla de Derivadas e Integrales PDFDocument1 pageTabla de Derivadas e Integrales PDFKathy CoMonNo ratings yet

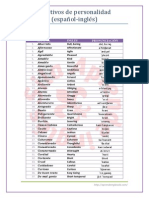

- Adjetivos PersonalidadDocument5 pagesAdjetivos PersonalidadDaniel Suarez ManriqueNo ratings yet

- 60 AdjetivosDocument1 page60 AdjetivosOscar OsKrNo ratings yet

- Cap 7Document7 pagesCap 7Carlos PerezNo ratings yet

- Cap 11-14Document5 pagesCap 11-14Carlos PerezNo ratings yet

- 15 16 17Document4 pages15 16 17Carlos PerezNo ratings yet

- Cap 12Document4 pagesCap 12Carlos PerezNo ratings yet

- Cap 11-14Document6 pagesCap 11-14Carlos PerezNo ratings yet

- Cap 7Document7 pagesCap 7Carlos PerezNo ratings yet

- DC Motor Ø 24 1.16.011Document11 pagesDC Motor Ø 24 1.16.011Carlos PerezNo ratings yet

- Utran LongDocument7 pagesUtran LongCarlos PerezNo ratings yet

- Análisis de La Respuesta de Sistemas en Tiempo ContinuoDocument15 pagesAnálisis de La Respuesta de Sistemas en Tiempo Continuopaca123No ratings yet

- PLMN and Cell SelectionDocument3 pagesPLMN and Cell SelectionCarlos Perez100% (1)

- Practica 4Document4 pagesPractica 4Carlos PerezNo ratings yet

- Cap 12Document4 pagesCap 12Carlos PerezNo ratings yet

- Practica 3Document3 pagesPractica 3fernando_jaramill_66No ratings yet

- PDF AtmosferaDocument12 pagesPDF AtmosferaCarlos PerezNo ratings yet

- Medidas ElectricasDocument30 pagesMedidas ElectricasAlfonso Mendoza94% (17)

- Coeficientes de Asimetria de Fisher y de PearsonDocument5 pagesCoeficientes de Asimetria de Fisher y de PearsonCarlos Ruiz HernandezNo ratings yet

- Antena Yagi-Uda de 5 elementos para banda de 70 cmDocument8 pagesAntena Yagi-Uda de 5 elementos para banda de 70 cmlismartobiasNo ratings yet

- Exposicion Fundicion NodularDocument9 pagesExposicion Fundicion NodularAzael Hernández PelcastreNo ratings yet

- Presentación Pitch THEMATICDocument13 pagesPresentación Pitch THEMATICFernando Perez PiraNo ratings yet

- Tratamiento Psicológico en El Tartamudeo.Document5 pagesTratamiento Psicológico en El Tartamudeo.Ana DezaNo ratings yet

- 03 Compass Anticolision 2012Document19 pages03 Compass Anticolision 2012damnerjoseNo ratings yet

- ValidezDocument3 pagesValidezcatalinaNo ratings yet

- Campos Baeza La Idea Construida-11-25Document25 pagesCampos Baeza La Idea Construida-11-25Luis Angel Mamani Lupaca100% (2)

- Geometria Analitica Hugo Iniguez Pdf1818302753Document313 pagesGeometria Analitica Hugo Iniguez Pdf1818302753Mario89% (28)

- La LecturaDocument5 pagesLa LecturaAlexandra NunoNo ratings yet

- Protocolo de Medicion de Resistencia de Puesta A Tierra Pozo de Alta SKID 4Document1 pageProtocolo de Medicion de Resistencia de Puesta A Tierra Pozo de Alta SKID 4Luis Enrique Yanallaye ArandaNo ratings yet

- Prueba Diagnos Tica - GRADO OCTAVODocument4 pagesPrueba Diagnos Tica - GRADO OCTAVOAdriana Bolaños CaicedoNo ratings yet

- Transmisión de movimientoDocument31 pagesTransmisión de movimientomelanyNo ratings yet

- Pauta Ejercicio Certamen 2 Hidro 2 2014Document3 pagesPauta Ejercicio Certamen 2 Hidro 2 2014gonzalo7cornejo7ramiNo ratings yet

- Com4 - Unidad1 La Exposición AcadémicaDocument8 pagesCom4 - Unidad1 La Exposición AcadémicaELVIA VASQUEZ PEREZ.No ratings yet

- Acustica Maria de Jesus Olguin MezaDocument9 pagesAcustica Maria de Jesus Olguin MezaALEXA YAIRYM BARRAGAN - MORANo ratings yet

- Examen Primero de PreescolarDocument13 pagesExamen Primero de PreescolarLUIS MIGUEL CORTES COSTILLANo ratings yet

- Instrucciones de Uso Del Menu EngineeringDocument3 pagesInstrucciones de Uso Del Menu EngineeringAntonio Jimenez RamirezNo ratings yet

- Ejemplo de TesisDocument11 pagesEjemplo de TesisERICK FEDERICO CORTES TORRESNo ratings yet

- Historia de Santa AnitaDocument5 pagesHistoria de Santa AnitaAlexander ZúñigaNo ratings yet

- SONA Framework for Intelligent Network ArchitectureDocument7 pagesSONA Framework for Intelligent Network Architecturechuckybaby06017No ratings yet

- Antología de Clima y Desarrollo Organizacional (Materia de Administración II)Document37 pagesAntología de Clima y Desarrollo Organizacional (Materia de Administración II)JoséLuisMartínezJuárezNo ratings yet

- DistribucionDocument3 pagesDistribucionAna QuinteroNo ratings yet

- Africa en SL AulaDocument29 pagesAfrica en SL AulalibreroeroNo ratings yet

- Tarea 1 - Alejandra Mesa - 1010223998Document4 pagesTarea 1 - Alejandra Mesa - 1010223998Alejandra MesaNo ratings yet

- Código I-001 Fecha Diciembre 2008 Universidad Centroccidental "Lisandro Alvarado" Dirección de Planificaciòn UniversitariaDocument56 pagesCódigo I-001 Fecha Diciembre 2008 Universidad Centroccidental "Lisandro Alvarado" Dirección de Planificaciòn UniversitariaGabriel RiveroNo ratings yet

- Aspectos Administrativos InvestigaciónDocument2 pagesAspectos Administrativos InvestigaciónCesarito PimentelNo ratings yet

- Plantilla Planificacion API. Mat. 5Document14 pagesPlantilla Planificacion API. Mat. 5EstarliNo ratings yet

- Sistema Nervioso UNCDocument64 pagesSistema Nervioso UNCLucas Abugattas SalemNo ratings yet

- Parcial I G2Document1 pageParcial I G2Cristián CordobaNo ratings yet

- Pisco ExposicionDocument17 pagesPisco ExposicionMary Trini Coari CoilaNo ratings yet

- Hipótesis - Qué Es, Definición y Concepto - 2021 - EconomipediaDocument1 pageHipótesis - Qué Es, Definición y Concepto - 2021 - EconomipediaMattius Alex MatamorosNo ratings yet