Professional Documents

Culture Documents

Dual-Phase, Quick-PWM Controllers For IMVP-IV CPU Core Power Supplies

Uploaded by

lucian1961Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dual-Phase, Quick-PWM Controllers For IMVP-IV CPU Core Power Supplies

Uploaded by

lucian1961Copyright:

Available Formats

General Descript ion

The M AX1987/M AX1988 are dual-phase, Q uick-PWM ,

step-down controllers for IM VP-IV CPU core supplies.

D ual-phase operati on reduces i nput ri pple current

requirements and output voltage ripple, while easing

component selection and layout difficulties. The Q uick-

PWM control scheme provides instantaneous response to

fast load-current steps. The M AX1987/M AX1988 include

active voltage positioning with adjustable gain and offset,

reducing power dissipation and bulk output capacitance

requirements.

The M AX1987/M AX1988 are intended for two different

notebook C PU core applications: stepping down the

battery directly or stepping down the 5V system supply

to create the core voltage. The single-stage conversion

method allows these devices to directly step down high-

voltage batteri es for the hi ghest possi ble effi ci ency.

Alternatively, two-stage conversion ( stepping down the

5V system supply i nstead of the battery) at hi gher

swi tchi ng frequency provi des the mi ni mum possi ble

physical size.

The M AX1987/M AX1988 meet the I M VP-I V specifica-

tions and can directly interface with the C PU power-

good signals from the V

C C P

and V

C C M C H

rails within

the system. The switching regulator features power-up

sequenci ng, automati cally rampi ng up to the I ntel-

specified boot voltage. The M AX1987/M AX1988 also

feature independent four-level logic inputs for setting

the boot voltage ( B0 to B2) and the suspend voltage

( S0 to S2) .

The M AX1987/M AX1988 include output undervoltage

protection, thermal protection, and system power-O K

( SYSPO K ) input. When any of these protection features

detect a fault, the controller shuts down. Additionally,

the M AX1987 includes overvoltage protection.

The M AX1987/M AX1988 are available in a low-profile

48-pin 7mm 7mm Thin Q FN package.

Applicat ions

I M VP-I V Notebook Computers

M ultiphase CPU Core Supply

Voltage-Positioned Step-Down Converters

Servers/Desktop Computers

Feat ures

o Dual-Phase, Quick-PWM Controllers

o 0.75% V

OUT

Accuracy Over Line, Load, and

Temperature

o Active Voltage Positioning with Adjustable Gain

and Offset

o 6-Bit On-Board DAC (16mV Increments)

o 0.492V to 1.708V Output Adjust Range

o Selectable 200kHz/300kHz/550kHz Switching

Frequency

o 2V to 28V Battery Input Voltage Range

o Adjustable Slew Rate Control

o Drives Large Synchronous Rectifier MOSFETs

o Output Overvoltage Protection (MAX1987 Only)

o Undervoltage and Thermal Fault Protection

o IMVP-IV Power Sequencing and Timing

o Selectable Boot and Suspend Voltages

o Low-Profile 7mm 7mm 48-Pin Thin QFN

Package

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

________________________________________________________________ Maxim Integrated Products 1

Ordering I nformat ion

19-2559; Rev 0; 7/02

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxims website at www.maxim-ic.com.

Typical Operating Circuit appears at end of data sheet.

PART TEMP RANGE PIN-PACKAGE

MAX1987ETM -40C to + 100C 48 Thin Q FN 7mm 7mm

MAX1988ETM -40C to + 100C 48 Thin Q FN 7mm 7mm

V

DD

DLM

LXM

BSTM

D1

D2

D3

D5

D4

D0

DHM B0

B1

B2

S0

S1

S2

V

CC

REF

ILIM

TON

TIME 1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

C

C

I

F

B

O

A

I

N

-

O

A

I

N

+

P

S

I

I

M

V

P

O

K

S

Y

S

O

K

N

E

G

P

O

S

C

C

V

G

N

D

C

S

N

C

M

N

C

M

P

S

U

S

V

+

B

S

T

S

L

X

S

D

H

S

P

G

N

D

D

L

S

C

S

P

7mm x 7mm THIN QFN

MAX1987

MAX1988

TOP VIEW

4

8

4

7

4

6

4

5

4

4

4

3

4

2

4

1

4

0

3

9

3

8

3

7

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

SHDN

C

L

K

E

N

DD0

D

P

S

L

P

Pin Configurat ion

Q uick-PW M is a tradem ark of M axim Integrated Products, Inc.

IM VP-IV is a tradem ark of Intel C orp.

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

( Circuit of Figure1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= 0C to +85C, unless otherwise specified.)

Stresses beyond those listed under Absolute M axim um Ratings m ay cause perm anent dam age to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not im plied. Exposure to

absolute m axim um rating conditions for extended periods m ay affect device reliability.

V+ to G ND ..............................................................-0.3V to + 30V

V

CC

to G ND ..............................................................-0.3V to + 6V

V

DD

to PG ND ............................................................-0.3V to + 6V

PSI, SUS, I M VPO K , CLKEN, DPSLP,

SYSO K , D0D5 to G ND ........................................-0.3V to + 6V

I LI M , FB, PO S, NEG , CCV, CCI , REF, O AI N+ ,

O AI N- to G ND.........................................-0.3V to ( V

CC

+ 0.3V)

CM P, CSP, CM N, CSN to G ND ..................-0.3V to ( V

CC

+ 0.3V)

DDO, TO N, TI M E, B0, B1, B2,

S0, S1, S2 to G ND ..................................-0.3V to ( V

CC

+ 0.3V)

SHDN to G ND ( Note 1) ...........................................-0.3V to + 18V

DLM , DLS to PG ND ....................................-0.3V to ( V

DD

+ 0.3V)

BSTM , BSTS to G ND ..............................................-0.3V to + 36V

DHM to LXM ...........................................-0.3V to ( V

BSTM

+ 0.3V)

LXM to BSTM ............................................................-6V to + 0.3V

DHS to LXS..............................................-0.3V to ( V

BSTS

+ 0.3V)

LXS to BSTS .............................................................-6V to + 0.3V

G ND to PG ND .......................................................-0.3V to + 0.3V

REF Short-Circuit Duration ( T

A

= + 70C) ...................Continuous

Continuous Power Dissipation

48-Pin Q FN ( derate 26.3mW/C above + 70C) ...........2.105W

O perating Temperature Range ...........................-40C to + 85C

Junction Temperature......................................................+ 150C

Storage Temperature Range .............................-65C to + 150C

Lead Temperature ( soldering, 10s) .................................+ 300C

Note 1: SHDN may be forced to 12V, for the purpose of debugging prototype boards using the no-fault test mode, which disables

fault protection and disables overlapping operation.

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

PWM CONTROLLER

Battery voltage, V+ 2 28

I nput-Voltage Range

V

CC

, V

DD

4.5 5.5

V

DAC codes from

1.276V to 1.708V

-0.75 + 0.75

DAC codes from

0.844V to 1.260V

-1.25 + 1.25

DC O utput-Voltage Accuracy

( Note 2)

V+ = 4.5V to 28V,

includes load

regulation error

DAC codes from

0.492V to 0.828V

-3.00 + 3.00

%

Line Regulation Error V

CC

= 4.5V to 5.5V, V+ = 4.5V to 28V 5 mV

I

FB

FB -2 + 2

I nput Bias Current

I

PO S,

I

NEG

PO S, NEG -0.2 + 0.2

A

PO S, NEG Common-M ode Range DPSLP = G ND 0 2 V

PO S, NEG Differential Range V

PO S

- V

NEG

, DPSLP = G ND -200 + 200 mV

PO S, NEG O ffset G ain A

O S

V

FB

/( V

PO S

- V

NEG

) ,

( V

PO S

- V

NEG

) = 100mV, DPSLP = G ND

0.95 1.00 1.05 mV/mV

PO S, NEG Enable Time t

O S

M easured from the time DPSLP goes low to

the time in which PO S, NEG affect a change

in the set point ( V

DAC

)

0.1 s

640kHz nominal, R

TI M E

= 23.5k 580 640 700

320kHz nominal, R

TI M E

= 47k 295 320 345 TI M E Frequency Accuracy f

TI M E

64kHz nominal, R

TI M E

= 235k 58 64 70

kHz

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

_______________________________________________________________________________________ 3

ELECTRICAL CHARACTERISTICS (continued)

( Circuit of Figure1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= 0C to +85C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

TO N = REF

( 550kHz)

155 180 205

TO N = open

( 300kHz)

320 355 390 O n-Time ( Note 3) t

O N

V+ = 12V,

V

FB

= V

CCI

= 1.2V

TO N = V

CC

( 200kHz)

475 525 575

ns

TO N = REF ( 550kHz) 330 375

M inimum O ff-Time ( Note 3) t

O FF( M I N)

TO N = V

CC

or open ( 200kHz or 300kHz) 435 500

ns

DDO Delay Time t

DDO

M easured from the time FB reaches the

voltage set by S0 to S2. Clock speed set by

R

TI M E

.

32 clks

SK I P Delay Time t

SK I P

M easured from the time when DDO is

asserted to the time in which the controller

begins pulse-skipping operation

30 clks

BIAS AND REFERENCE

Q uiescent Supply Current ( V

CC

) I

CC

M easured at V

CC

, FB forced above the

regulation point

1.70 2.70 mA

Q uiescent Supply Current ( V

DD

) I

DD

M easured at V

DD

, FB forced above the

regulation point

<1 5 A

Q uiescent Battery Supply

Current ( V+ )

I

V+

M easured at V+ 25 50 A

Shutdown Supply Current ( V

CC

) M easured at V

CC

, SHDN = G ND 2 5 A

Shutdown Supply Current ( V

DD

) M easured at V

DD

, SHDN = G ND <1 5 A

Shutdown Battery Supply

Current ( V+ )

M easured at V+ , SHDN = G ND,

V

CC

= V

DD

= 0 or 5V

<1 5 A

Reference Voltage V

REF

V

CC

= 4.5V to 5.5V, I

REF

= 0 1.990 2.000 2.010 V

Reference Load Regulation V

REF

I

REF

= -10A to + 100A -10 + 10 mV

FAULT PROTECTION

O utput O vervoltage Protection

Threshold ( M AX1987 O nly)

V

O VP

M easured at FB 1.95 2.00 2.05 V

O utput O vervoltage Propagation

Delay ( M AX1987 O nly)

t

O VP

FB forced above 2.05V 10 s

O utput Undervoltage Protection

Threshold

V

UVLO

M easured at FB with respect to unloaded

output voltage

67 70 73 %

O utput Undervoltage Propagation

Delay

t

UVP

FB forced 2% below trip threshold 10 s

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

4 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)

( Circuit of Figure1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= 0C to +85C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Lower threshold

( undervoltage)

-13 -10 -7

I M VPO K , CLKEN Threshold

V

SYSPO K

= 5V;

measured at FB with

respect to unloaded

output voltage

Upper threshold

( overvoltage)

+ 7 + 10 + 13

%

CLKEN Delay t

CLKEN

FB in regulation, measured from the rising

edge of SYSPO K

30 50 90 s

O utput Fault, I M VPO K , and

CLKEN Transition Blanking Time

t

BLANK

M easured from the time when FB reaches

the voltage set by the DAC code, clock

speed set by R

TI M E

( Note 4)

32 clks

I M VPO K Delay t

I M VPO K

FB in regulation, measured from the falling

edge of CLKEN

3 5 7 ms

I M VPO K , CLKEN O utput Low

Voltage

I

SI NK

= 3mA 0.3 V

I M VPO K , CLKEN Leakage

Current

High state, I M VPO K , CLKEN forced to 5.5V 1 A

V

CC

Undervoltage Lockout

Threshold

V

UVLO

( VCC)

Rising edge, hysteresis = 90mV, PWM

disabled below this level

4.0 4.2 4.4 V

Thermal Shutdown Threshold T

SHDN

Hysteresis = 15C 160 C

CURRENT LIMIT AND BALANCE

Current-Limit Threshold Voltage

( Positive, Default)

V

LI M I T

CM P - CM N, CSP - CSN; I LI M = V

CC

27 30 33 mV

V

I LI M

= 1V 47 50 53

Current-Limit Threshold Voltage

( Positive, Adjustable)

V

LI M I T

CM P - CM N,

CSP - CSN

V

I LI M

= 1.5V 72 75 78

mV

Current-Limit Threshold Voltage

( Negative)

V

LI M I T

( NEG )

CM P - CM N, CSP - CSN; I LI M = V

CC

,

SUS = G ND, and DPSLP = PSI = V

CC

-30 -36 -42 mV

Current-Limit Threshold Voltage

( Zero-Crossing)

V

ZERO

CM P - CM N, CSP - CSN; SUS = V

CC

or

DPSLP = G ND or PSI = G ND

1.5 mV

CM P, CM N, CSP,

CSN I nput Ranges

0 2 V

CM P, CM N, CSP,

CSN I nput Current

V

CSP

= V

CSN

= 0 to 5V -2 + 2 A

I LI M I nput Current I

I LI M

V

I LI M

= 0 to 5V 0.1 200 nA

Current-Limit Default Switchover

Threshold

I LI M 3

V

CC

-

1

V

CC

-

0.4

V

Current-Balance O ffset V

O S( I BAL)

( V

CM P

- V

CM N

) - ( V

CSP

- V

CSN

) ;

I

CCI

= 0, -20mV < ( V

CM P

- V

CM N

) <+ 20mV,

0.5V < V

CCI

< 2.8V

-2.0 + 2.0 mV

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

_______________________________________________________________________________________ 5

ELECTRICAL CHARACTERISTICS (continued)

( Circuit of Figure1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= 0C to +85C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Current-Balance

Transconductance

g

M ( I BAL)

400 S

GATE DRIVERS

DH_ G ate-Driver O n-Resistance R

O N( DH)

BST_ - LX_ forced to 5V 1.0 4.5

High state ( pullup) 1.0 4.5

DL_ G ate-Driver O n-Resistance R

O N( DL)

Low state ( pulldown) 0.4 2.0

DH_ G ate-Driver Source/Sink

Current

I

DH

DH_ forced to 2.5V,

BST_ - LX_ forced to 5V

1.6 A

DL_ G ate-Driver Sink Current I

DL( SI NK )

DL_ forced to 5V 4 A

DL_ G ate-Driver Source Current I

D L( S OU RC E )

DL_ forced to 2.5V 1.6 A

DL_ rising 35

Dead Time t

DEAD

DH_ rising 26

ns

VOLTAGE-POSITIONING AMPLIFIER

I nput O ffset Voltage V

O S

-1.5 + 1.5 mV

I nput Bias Current I

BI AS

O AI N+ , O AI N- 0.1 200 nA

O p Amp Disable Threshold O AI N- 3

V

CC

-

1

V

CC

-

0.4

V

Common-M ode I nput-Voltage

Range

V

CM

G uaranteed by CM RR test 0 2.5 V

Common-M ode Rejection Ratio CM RR V

O AI N+

= V

O AI N-

= 0 to 2.5V 70 100 dB

Power-Supply Rejection Ratio PSRR V

CC

= 4.5V to 5.5V 75 100 dB

Large-Signal Voltage G ain A

O A

R

L

= 1k to V

CC

/2 70 112 dB

V

CC

- V

FBH

77 300

O utput-Voltage Swing

( V

O AI N+

- V

O AI N-

) 10mV,

R

L

= 1k to V

CC

/2

V

FBL

47 200

mV

I nput Capacitance 11 pF

G ain-Bandwidth Product 3 M Hz

Slew Rate 0.3 V/s

Capacitive Load Stability No sustained oscillations 400 pF

LOGIC AND I/O

Logic-I nput High Voltage V

I H

SUS, DPSLP, SHDN, SYSPO K 2.4 V

Logic-I nput Low Voltage V

I L

SUS, DPSLP, SHDN, SYSPO K 0.8 V

Logic-I nput Current SUS, DPSLP, SHDN, SYSPO K -1 + 1 A

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

6 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)

( Circuit of Figure1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= 0C to +85C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SHDN No-Fault Threshold To enable no-fault mode 12 15 V

1V Logic-I nput High Voltage D0D5, PSI 0.7 V

1V Logic-I nput Low Voltage D0D5, PSI 0.3 V

DAC I nput Current D0D5, PSI -1 + 1 A

Driver Disable O utput High

Voltage

DDO, I

LO AD

= 1mA 2.4 V

Driver Disable O utput Low

Voltage

DDO, I

LO AD

= 1mA 0.3 V

High V

CC

- 0.4

O pen 3.15 3.85

REF 1.65 2.35

Four-Level I nput Logic Levels

TO N, S0 to S2,

B0 to B2

Low 0.5

V

Four-Level I nput Current

TO N, S0 to S2, B0 to B2 forced to

G ND or V

CC

-4 + 4 A

ELECTRICAL CHARACTERISTICS

( Circuit of Figure 1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= -40C to +100C, unless otherwise specified.) ( Note 5)

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

PWM CONTROLLER

Battery voltage, V+ 2 28

I nput-Voltage Range

V

CC

, V

DD

4.5 5.5

V

DAC codes from

1.276V to 1.708V

-1.00 + 1.00

DAC codes from

0.844V to 1.260V

-1.50 + 1.50

DC O utput-Voltage Accuracy

( Note 2)

V+ = 4.5V to 28V,

includes load

regulation error

DAC codes from

0.492V to 0.828V

-3.5 + 3.5

%

PO S, NEG O ffset G ain A

O FF

V

FB

/( V

PO S

- V

NEG

) ,

( V

PO S

- V

NEG

) = 100mV, DPSLP = G ND

0.95 1.05 mV/mV

640kHz nominal, R

TI M E

= 23.5k 580 700

320kHz nominal, R

TI M E

= 47k 295 345 TI M E Frequency Accuracy f

TI M E

64kHz nominal, R

TI M E

= 235k 58 70

kHz

TO N = REF ( 550kHz) 155 205

TO N = open ( 300kHz) 320 390 O n-Time ( Note 3) t

O N

V+ = 12V,

V

FB

= V

CCI

= 1.2V

TO N = V

CC

( 200kHz) 475 575

ns

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

_______________________________________________________________________________________ 7

ELECTRICAL CHARACTERISTICS (continued)

( Circuit of Figure 1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= -40C to +100C, unless otherwise specified.) ( Note 5)

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

TO N = REF ( 550kHz) 375

M inimum O ff-Time

( Note 3)

t

O FF( M I N) TO N = V

CC

or open

( 200kHz or 300kHz)

500

ns

BIAS AND REFERENCE

Q uiescent Supply Current ( V

CC

) I

CC

M easured at V

CC

, FB forced above the

regulation point

3.00 mA

Q uiescent Supply Current ( V

DD

) I

DD

M easured at V

DD

, FB forced above the

regulation point

30 A

Q uiescent Battery Supply

Current ( V+ )

I

V+

M easured at V+ 50 A

Shutdown Supply Current ( V

CC

) M easured at V

CC

, SHDN = G ND 20 A

Shutdown Supply Current ( V

DD

) M easured at V

DD

, SHDN = G ND 20 A

Shutdown Battery Supply

Current ( V+ )

M easured at V+ , SHDN = G ND,

V

CC

= V

DD

= 0 or 5V

20 A

Reference Voltage V

REF

V

CC

= 4.5V to 5.5V, I

REF

= 0 1.985 2.015 V

FAULT PROTECTION

O utput O vervoltage Protection

Threshold ( M AX1987 O nly)

M easured at FB 1.95 2.05 V

O utput Undervoltage Protection

Threshold

M easured at FB with respect to unloaded

output voltage

67 73 %

Lower threshold

( undervoltage)

-13 -7

I M VPO K , CLKEN Threshold

V

SYSPO K

= 5V;

measured at FB with

respect to unloaded

output voltage

Upper threshold

( overvoltage)

7 13

%

CLKEN Delay t

CLKEN

FB in regulation, measured from the rising

edge of SYSPO K

30 s

I M VPO K Delay t

I M VPO K

FB in regulation, measured from the falling

edge of CLKEN

3 ms

V

CC

Undervoltage Lockout

Threshold

V

UVLO

( VCC)

Rising edge, hysteresis = 90mV, PWM

disabled below this level

3.95 4.45 V

CURRENT LIMIT AND BALANCE

Current-Limit Threshold Voltage

( Positive, Default)

V

LI M I T

CM P - CM N, CSP - CSN; I LI M = V

CC

25 35 mV

V

I LI M

= 1V 45 55

Current-Limit Threshold Voltage

( Positive, Adjustable)

V

LI M I T

CM P - CM N,

CSP - CSN

V

I LI M

= 1.5V 70 80

mV

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

8 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)

( Circuit of Figure 1, V+ = 15V, V

CC

= V

DD

= V

SHDN

= V

TO N

= V

DPSLP

= V

PSI

= V

B1

= V

O AI N-

= 5V, V

B2

= 2V, V

FB

= V

CM P

= V

CM N

=

V

C SP

= V

C SN

= V

O AI N+

= V

NEG

= V

PO S

= 1. 26V, V

D4

= V

D3

= V

D2

= 1. 0V, V

SUS

= V

D5

= V

D1

= V

D0

= V

S0

= V

S1

= V

S2

=

V

B0

= 0, T

A

= -40C to +100C, unless otherwise specified.) ( Note 5)

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

Current-Limit Threshold Voltage

( Negative)

V

LI M I T

( NEG )

CM P - CM N, CSP - CSN; I LI M = V

CC

,

SUS = G ND and DPSLP = V

CC

-27 -45 mV

Current-Balance O ffset V

O S( I BAL)

( V

CM P

- V

CM N

) - ( V

CSP

- V

CSN

) ; I

CCI

= 0,

-20mV < ( V

CM P

- V

CM N

) < 20mV,

0.5V < V

CCI

< 2.8V

-3 + 3 mV

GATE DRIVERS

DH_G ate-Driver O n-Resistance R

O N( DH)

BST_ - LX_forced to 5V 4.5

High state ( pullup) 4.5

DL_G ate-Driver O n-Resistance R

O N( DL)

Low state ( pulldown) 2.0

VOLTAGE-POSITIONING AMPLIFIER

I nput O ffset Voltage V

O S

-2.5 + 2.5 mV

Common-M ode I nput

Voltage Range

V

CM

G uaranteed by CM RR test 0 2.5 V

V

CC

- V

FBH

300

O utput-Voltage Swing

( V

O AI N+

- V

O AI N-

) 10mV,

R

L

= 1k to V

CC

/2

V

FBL

200

mV

LOGIC AND I/O

Logic-I nput High Voltage V

I H

SUS, DPSLP, SHDN, SYSPO K 2.4 V

Logic-I nput Low Voltage V

I L

SUS, DPSLP, SHDN, SYSPO K 0.8 V

1V Logic-I nput High Voltage D0D5, PSI 0.7 V

1V Logic-I nput Low Voltage D0D5, PSI 0.3 V

High V

CC

-

0.4

O pen 3.15 3.85

REF 1.65 2.35

Four-Level I nput Logic Levels

TO N, S0 to S2,

B0 to B2

Low 0.5

V

Note 2: DC output accuracy specifications refer to the trip level of the error amplifier. The output voltage has a DC regulation higher

than the trip level by 50% of the output ripple. When pulse-skipping, the output rises by approximately 1.5% when transition-

ing from continuous conduction to no load.

Note 3: O n-time and minimum off-time specifications are measured from 50% to 50% at the DHM and DHS pins, with LX_ forced to

G ND, BST_ forced to 5V, and a 500pF capacitor from DH_ to LX_ to simulate external M O SFET gate capacitance. Actual in-

circuit times can be different due to M O SFET switching speeds.

Note 4: The output fault-blanking time is measured from the time when FB reaches the regulation voltage set by the DAC code.

During power-up, the regulation voltage is set by the boot DAC code ( B0 to B2) . During normal operation ( SUS = G ND) , the

regulation voltage is set by the VI D DAC inputs ( D0D5) . During suspend mode ( SUS = V

CC

) , the regulation voltage is set

by the suspend DAC inputs ( S0 to S2) .

Note 5: Specifications to T

A

= -40C to + 100C are guaranteed by design and are not production tested.

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

_______________________________________________________________________________________ 9

OUTPUT VOLTAGE vs. LOAD CURRENT

(V

OUT

= 1. 356V)

M

A

X

1

9

8

7

/

8

8

to

c

0

1

LOAD CURRENT (A)

O

U

T

P

U

T

V

O

L

T

A

G

E

(

V

)

30 20 10

1.20

1.25

1.30

1.35

1.40

1.15

0 40

EFFICIENCY vs. LOAD CURRENT

(V

OUT

= 1. 356V)

M

A

X

1

9

8

7

/

8

8

to

c

0

2

LOAD CURRENT (A)

E

F

F

I

C

I

E

N

C

Y

(

%

)

10 1

60

70

80

90

100

50

0.1 100

V

IN

= 12V

V

IN

= 8V

V

IN

= 20V

PSI = GND

PSI = V

CC

OUTPUT VOLTAGE vs. LOAD CURRENT

(V

OUT

= 0. 844V)

M

A

X

1

9

8

7

/

8

8

to

c

0

3

LOAD CURRENT (A)

O

U

T

P

U

T

V

O

L

T

A

G

E

(

V

)

25 20 15 10 5

0.75

0.78

0.80

0.83

0.85

0.88

0.73

0 30

EFFICIENCY vs. LOAD CURRENT

(V

OUT

= 0. 844V)

M

A

X

1

9

8

7

/

8

8

to

c

0

4

LOAD CURRENT (A)

E

F

F

I

C

I

E

N

C

Y

(

%

)

10 1

60

70

80

90

100

50

0.1 100

V

IN

= 12V

V

IN

= 8V

V

IN

= 20V

PSI = GND

PSI = V

CC

OUTPUT VOLTAGE vs. LOAD CURRENT

(V

OUT

= 0. 748V)

M

A

X

1

9

8

7

/

8

8

to

c

0

5

LOAD CURRENT (A)

O

U

T

P

U

T

V

O

L

T

A

G

E

(

V

)

15 10 5

0.68

0.69

0.70

0.71

0.72

0.73

0.74

0.75

0.76

0.77

0.67

0 20

SUS = V

CC

EFFICIENCY vs. LOAD CURRENT

(V

OUT

= 0. 748V)

M

A

X

1

9

8

7

/

8

8

to

c

0

6

LOAD CURRENT (A)

E

F

F

I

C

I

E

N

C

Y

(

%

)

10 1

60

70

80

90

100

50

0.1 100

V

IN

= 12V

V

IN

= 8V

V

IN

= 20V

PSI = GND

PSI = V

CC

- 5

- 2

- 3

- 4

0

- 1

4

3

2

1

5

- 40 - 20 0 20 40 60 80 100

REFERENCE VOLTAGE SHIFT

vs. TEMPERATURE

M

A

X

1

9

8

7

/

8

8

to

c

0

7

TEMPERATURE (C)

V

R

E

F

(

m

V

)

SWITCHING FREQUENCY

vs. LOAD CURRENT

M

A

X

1

9

8

7

/

8

8

to

c

0

8

LOAD CURRENT (A)

S

W

I

T

C

H

I

N

G

F

R

E

Q

U

E

N

C

Y

(

k

H

z

)

30 20 10

100

200

300

400

0

0 40

FORCED- PWM (V

PSI

= 5V)

SKIP MODE (V

PSI

= 0)

220

240

280

260

300

320

0 10 5 15 20 25 30

SWITCHING FREQUENCY

vs. INPUT VOLTAGE

M

A

X

1

9

8

7

/

8

8

to

c

0

9

INPUT VOLTAGE (V)

F

R

E

Q

U

E

N

C

Y

(

k

H

z

)

I

OUT

= 20A

NO LOAD

Typical Operat ing Charact erist ics

( Circuit of Figure 1, V+ = 12V, V

CC

= V

DD

= 5V, SUS = G ND, SHDN = DPSLP = PSI = V

CC

, B0 to B2 set for 1.372V, S0 to S2 set for

0.748V, T

A

= + 25C, unless otherwise specified.)

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

10 ______________________________________________________________________________________

OUTPUT OFFSET VOLTAGE vs.

POS-NEG DIFFERENTIAL VOLTAGE

M

A

X

1

9

8

7

/

8

8

to

c

1

4

POS- NEG DIFFERENTIAL VOLTAGE (mV)

O

U

T

P

U

T

O

F

F

S

E

T

V

O

L

T

A

G

E

(

m

V

)

400 200 0 - 200 - 400

- 400

- 200

0

200

400

600

- 600

- 600 600

60

- 40

0.1 10 100 1000 1 10,000

VOLTAGE-POSITIONING AMPLIFIER

GAIN AND PHASE vs. FREQUENCY

- 20

- 10

0

- 30

MAX1987/ 88 toc18

FREQUENCY (kHz)

G

A

I

N

(

d

B

)

P

H

A

S

E

(

D

E

G

R

E

E

S

)

10

20

30

40

50

180

- 180

- 108

- 72

- 36

- 144

0

36

72

108

144

GAIN

PHASE

Typical Operat ing Charact erist ics (cont inued)

( Circuit of Figure 1, V+ = 12V, V

CC

= V

DD

= 5V, SUS = G ND, SHDN = DPSLP = PSI = V

CC

, B0 to B2 set for 1.372V, S0 to S2 set for

0.748V, T

A

= + 25C, unless otherwise specified.)

200

240

220

280

260

320

300

340

- 40 0 20 - 20 40 60 80 100

SWITCHING FREQUENCY

vs. TEMPERATURE

M

A

X

1

9

8

7

/

8

8

to

c

1

0

TEMPERATURE (C)

F

R

E

Q

U

E

N

C

Y

(

k

H

z

)

NO LOAD

20A NO LOAD

V

OUT

= 1.356V

35

36

38

37

39

40

- 40 0 - 20 20 40 60 80 100

OUTPUT CURRENT AT CURRENT LIMIT

vs. TEMPERATURE

M

A

X

1

9

8

7

/

8

8

to

c

1

1

TEMPERATURE (C)

M

A

X

I

M

U

M

L

O

A

D

C

U

R

R

E

N

T

(

A

)

0

20

60

40

80

100

0 10 5 15 20 25 30

NO LOAD SUPPLY CURRENT

vs. INPUT VOLTAGE

(FORCED-PWM MODE)

M

A

X

1

9

8

7

/

8

8

to

c

1

2

INPUT VOLTAGE (V)

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

m

A

)

I

CC

+ I

DD

I+

PSI = V

CC

0

0.5

1.5

1.0

2.0

2.5

0 10 5 15 20 25 30

NO LOAD SUPPLY CURRENT

vs. INPUT VOLTAGE

(PULSE SKIPPING)

M

A

X

1

9

8

7

/

8

8

to

c

1

3

INPUT VOLTAGE (V)

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

m

A

)

I

CC

+ I

DD

I+

PSI = GND

0

10

20

30

40

50

0.834 0.839 0.844 0.849 0.854

0. 844V OUTPUT-VOLTAGE DISTRIBUTION

M

A

X

1

9

8

7

/

8

8

to

c

1

5

OUTPUT VOLTAGE (V)

S

A

M

P

L

E

P

E

R

C

E

N

T

A

G

E

(

%

)

0

5

15

10

20

25

1.995 1.999 1.997 2.001 2.003 2.005

REFERENCE VOLTAGE DISTRIBUTION

M

A

X

1

9

8

7

/

8

8

to

c

1

6

REFERENCE VOLTAGE (V)

S

A

M

P

L

E

P

E

R

C

E

N

T

A

G

E

(

%

)

0

10

5

20

15

25

30

0.98 1.00 0.99 1.01 1.02

POS-NEG OFFSET GAIN

DISTRIBUTION

M

A

X

1

9

8

7

/

8

8

to

c

1

7

POS- NEG OFFSET GAIN

S

A

M

P

E

P

E

R

C

E

N

T

A

G

E

(

%

)

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

______________________________________________________________________________________ 11

VPS AMPLIFIER OFFSET VOLTAGE

vs. COMMON-MODE VOLTAGE

M

A

X

1

9

8

7

/

8

8

to

c

1

9

COMMON- MODE VOLTAGE (V)

O

F

F

S

E

T

V

O

L

T

A

G

E

(

V

)

4 3 2 1

20

40

60

80

100

120

140

160

180

0

0 5

VPS AMPLIFIER

DISABLED

POWER-UP SEQUENCE

MAX1987/ 88 toc21

100s/ di v

0

A

B

C

D

5V

0

5V

0

0

5V

BOOT

VID

A. V

SHDN

= 0 TO 5V, 5V/ di v

B. V

OUT

= 0 TO 1.372V TO 0.844V, 500mV/ di v

C. CLKEN, 5V/ di v

D. DDO, 5V/ di v

R

LOAD

= 80m

SOFT-START

MAX1987/ 88 toc22

100s/ di v

0

A

B

C

D

5V

0

10A

0

0

BOOT

VID

A. V

SHDN

= 0 TO 5V, 5V/ di v

B. V

OUT

= 0 TO 1.372V TO 0.844V, 500mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

R

LOAD

= 80m

SYSTEM POWER-OK

MAX1987/ 88 toc23

20s/ di v

0

A

B

C

D

5V

0

5V

BOOT

(1.372V)

HIGH FREQ VID

(1.356V)

LOW FREQ VID

(0.844V)

A. V

SYSPOK

= 0 TO 5V, 5V/ di v

B. HIGH FREQ: V

OUT

= 1.356V, 200mV/ di v

C. LOW FREQ: V

OUT

= 0.844V, 200mV/ di v

D. CLKEN, 5V/ di v

IMVPOK DELAY

MAX1987/ 88 toc24

1ms/ di v

0

0

A

B

C

D

5V

0

0

5V

5V

BOOT

(1.372V)

A. V

SHDN

= 0 TO 5V, 5V/ di v

B. V

OUT

= 0 TO 0.844V, 1V/ di v

C. CLKEN, 5V/ di v

D. IMVPOK, 5V/ di v

Typical Operat ing Charact erist ics (cont inued)

( Circuit of Figure 1, V+ = 12V, V

CC

= V

DD

= 5V, SUS = G ND, SHDN = DPSLP = PSI = V

CC

, B0 to B2 set for 1.372V, S0 to S2 set for

0.748V, T

A

= + 25C, unless otherwise specified.)

0

0.2

0.6

0.4

0.8

1.0

INDUCTOR CURRENT DIFFERENCE

vs. LOAD CURRENT

M

A

X

1

9

8

7

/

8

8

to

c

2

0

LOAD CURRENT (A)

I

L

(

C

S

)

-

I

L

(

C

M

)

(

A

)

0 20 10 30 40

PSI = GND

PSI = V

CC

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

12 ______________________________________________________________________________________

SHUTDOWN SEQUENCE

MAX1987/ 88 toc25

40s/ di v

0

0.84V

0

0

A

B

C

D

E

5V

5V

0

5V

0

5V

A. V

SHDN

= 5V TO 0, 5V/ di v

B. V

OUT

= 0.844V TO 0, 500mV/ di v

C. CLKEN, 5V/ di v

D. IMVPOK, 5V/ di v

E. DDO, 5V/ di v

R

LOAD

= 80m

SOFT SHUTDOWN

MAX1987/ 88 toc26

40s/ di v

0

0.84V

0

A

B

C

D

5V

0

0

A. V

SHDN

= 5V TO 0, 5V/ di v

B. V

OUT

= 0.844V TO 0, 500mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

R

LOAD

= 80m

LOAD TRANSIENT

(V

OUT

= 1. 356V)

MAX1987/ 88 toc27

40s/ di v

0

1.356V

A

B

C

D

25A

0

0

A. I

OUT

= 0 TO 25A, 20A/ di v

B. V

OUT

= 1.356V TO 1.281V, 50mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

LOAD TRANSIENT

(V

OUT

= 0. 844V)

MAX1987/ 88 toc28

40s/ di v

0

0.844V

A

B

C

D

10A

0

0

A. I

OUT

= 0 TO 10A, 10A/ di v

B. V

OUT

= 0.844V TO 0.814V, 20mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

ENTERING DEEP-SLEEP MODE

MAX1987/ 88 toc29

20s/ di v

0

1.350V

1.318V

A

B

C

D

5V

0

0

A. V

DPSLP

= 5V TO 0, 5V/ di v

B. V

OUT

= 1.350V TO 1.318V, 50mV/ di v

C. LXM, 10V/ di v

D. LXS, 10V/ di v

SUS = GND, I

OUT

= 1A

EXITING DEEP-SLEEP MODE

MAX1987/ 88 toc30

20s/ di v

0

1.351V

1.318V

A

B

C

D

5V

0

0

A. V

DPSLP

= 0 TO 5V, 5V/ di v

B. V

OUT

= 1.318V TO 1.351V, 50mV/ di v

C. LXM, 10V/ di v

D. LXS, 10V/ di v

SUS = GND, I

OUT

= 1A

Typical Operat ing Charact erist ics (cont inued)

( Circuit of Figure 1, V+ = 12V, V

CC

= V

DD

= 5V, SUS = G ND, SHDN = DPSLP = PSI = V

CC

, B0 to B2 set for 1.372V, S0 to S2 set for

0.748V, T

A

= + 25C, unless otherwise specified.)

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

______________________________________________________________________________________ 13

DEEP-SLEEP TRANSITION

MAX1987/ 88 toc31

40s/ di v

0

1.350V

1.318V

A

B

C

D

5V

0

0

A. V

DPSLP

= 5V TO 0, 5V/ di v

B. V

OUT

= 1.350V TO 1.318V, 50mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

SUS = GND, I

OUT

= 1A

ENTERING SUSPEND MODE

MAX1987/ 88 toc32

40s/ di v

0

0.751V

1.318V

A

B

C

D

5V

0

0

A. V

SUS

= 0 TO 5V, 5V/ di v

B. V

OUT

= 1.318V TO 0.751V, 500mV/ di v

C. LXM, 10V/ di v

D. LXS, 10V/ di v

DPSLP = GND, I

OUT

= 1.0A

EXITING SUSPEND MODE

MAX1987/ 88 toc33

40s/ di v

0

0.751V

1.318V

A

B

C

D

5V

0

0

A. V

SUS

= 5V TO 0, 5V/ di v

B. V

OUT

= 0.751V TO 1.318V, 500mV/ di v

C. LXM, 10V/ di v

D. LXS, 10V/ di v

DPSLP = GND, I

OUT

= 1A

SUSPEND TRANSITION

MAX1987/ 88 toc34

100s/ di v

0

0.751V

1.318V

A

B

C

D

5V

0

0

A. V

SUS

= 0 TO 5V, 5V/ di v

B. V

OUT

= 1.318V TO 0.751V, 500mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

DPSLP = GND, I

OUT

= 1A

MAX1987/ 88 toc35

20s/ di v

0

1.356V

A

B

C

D

5V

0

0

A. V

PSI

= 5V TO 0, 5V/ di v

B. V

OUT

= 1.356V, 50mV/ di v

C. LXM, 10V/ di v

D. LXS, 10V/ di v

I

OUT

= 1A

PSI TRANSITION

Typical Operat ing Charact erist ics (cont inued)

( Circuit of Figure 1, V+ = 12V, V

CC

= V

DD

= 5V, SUS = G ND, SHDN = DPSLP = PSI = V

CC

, B0 to B2 set for 1.372V, S0 to S2 set for

0.748V, T

A

= + 25C, unless otherwise specified.)

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

14 ______________________________________________________________________________________

Pin Descript ion

MAX1987/ 88 toc37

20s/ di v

0

1.356V

1.228V

A

B

C

D

1V

0

0

A. V

D3

= 0 TO 1V, 1V/ di v

B. V

OUT

= 1.356V TO 1.228V, 100mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

DYNAMIC VID TRANSITION

(D3 = 128mV)

Typical Operat ing Charact erist ics (cont inued)

( Circuit of Figure 1, V+ = 12V, V

CC

= V

DD

= 5V, SUS = G ND, SHDN = DPSLP = PSI = V

CC

, B0 to B2 set for 1.372V, S0 to S2 set for

0.748V, T

A

= + 25C, unless otherwise specified.)

MAX1987/ 88 toc36

20s/ di v

0

1.356V

1.340V

A

B

C

D

1V

0

0

A. V

D0

= 0 TO 1V, 1V/ di v

B. V

OUT

= 1.356V TO 1.340V, 20mV/ di v

C. I

LM

, 10A/ di v

D. I

LS

, 10A/ di v

DYNAMIC VID TRANSITION

(D0 = 16mV)

PIN NAME FUNCTION

1 TI M E

Slew-Rate Adjustment Pin. Connect a resistor from TI M E to G ND to set the internal slew-rate clock. A 235k

to 23.5k resistor sets the clock from 64kHz to 640kHz, f

SLEW

= 320kHz 47k/R

TI M E

.

2 TO N

O n-Time Selection Control I nput. This four-level input sets the K -factor value ( Table 3) used to determine the

DH on-time ( see the O n-Tim e O ne-Shot section) : G ND = 1000kHz ( untested) , REF = 550kHz,

open = 300kHz, V

CC

= 200kHz per phase

3, 4, 5

B0, B1,

B2

Boot-M ode Voltage Select I nputs. B0 to B2 are four-level digital inputs that select the boot-mode VI D code

( Table 6) for the boot-mode multiplexer inputs. During power-up, the boot-mode VI D code is delivered to the

DAC ( see the Internal M ultiplexers section) .

6, 7, 8

S0, S1,

S2

Suspend-M ode Voltage Select I nputs. S0 to S2 are four-level digital inputs that select the suspend-mode VI D

code ( Table 5) for the suspend-mode multiplexer inputs. I f SUS is high, the suspend-mode VI D code is

delivered to the DAC ( see the Internal M ultiplexers section) , overriding any other voltage setting ( Figure 9) .

9 SHDN

Shutdown Control I nput. This input cannot withstand the battery voltage. Connect to V

CC

for normal

operation. Connect to ground to put the I C into its 1A shutdown state. During the transition from normal

operation to shutdown, the output voltage is ramped down at the output voltage slew rate programmed by

the TI M E pin. I n shutdown mode, DLM and DLS are forced to V

DD

to clamp the output to ground. Forcing

SHDN to 12V~ 15V disables both overvoltage protection and undervoltage protection circuits, disables

overlap operation, and clears the fault latch. Do not connect SHDN to >15V.

10 REF

2V Reference O utput. Bypass to G ND with a 0.22F or greater ceramic capacitor. The reference can source

100A for external loads. Loading REF degrades output-voltage accuracy according to the REF load

regulation error.

11 I LI M

Current-Limit Adjustment. The current-limit threshold defaults to 30mV if I LI M is connected to V

CC

. I n

adjustable mode, the current-limit threshold voltage is precisely 1/20th the voltage seen at I LI M over a

200mV to 1.5V range. The logic threshold for switchover to the 30mV default value is approximately V

CC

- 1V.

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

______________________________________________________________________________________ 15

Pin Descript ion (cont inued)

PIN NAME FUNCTION

12 V

CC

Analog Supply Voltage I nput for PWM Core. Connect V

CC

to the system supply voltage ( 4.5V to 5.5V) with a

series 10 resistor. Bypass to G ND with a 1F or greater ceramic capacitor, as close to the I C as possible.

13 G ND Analog G round. Connect the M AX1987/M AX1988s exposed pad to analog ground.

14 CCV

Voltage I ntegrator Capacitor Connection. Connect a 47pF to 1000pF ( 270pF typ) capacitor from CCV to

analog ground ( G ND) to set the integration time constant.

15 PO S

Feedback O ffset Adjust Positive I nput. The output shifts by 100% ( typ) of the differential input voltage

appearing between PO S and NEG when DPSLP is low. The common-mode range of PO S and NEG is 0 to

2V. PO S and NEG should be generated from resistor-dividers from the output.

16 NEG

Feedback O ffset Adjust Negative I nput. The output shifts by 100% ( typ) of differential input voltage

appearing between PO S and NEG when DPSLP is low. The common-mode range of PO S and NEG is 0 to

2V. PO S and NEG should be generated from resistor-dividers from the output.

17 CCI

Current Balance Compensation. Connect a 470pF capacitor between CCI and FB ( see the C urrent Balance

C om pensation section) . An additional 470k to 1M resistor between CCI and FB for low-frequency

operation.

18 FB

Feedback I nput. FB is internally connected to both the feedback input and the output of the voltage-

positioning op amp ( Figure 2) . Connect a resistor between FB and O AI N- ( Figure 1) to set the voltage-

positioning gain ( see the Setting Voltage Positioning section) .

19 O AI N-

Dual-M ode O p Amp I nverting I nput and O p Amp Disable I nput. When using the internal op amp for

additional voltage-positioning gain ( Figure 1) , connect to the negative terminal of the current-sense resistor

through a 1.0k 1% resistor as described in the Setting Voltage Positioning section. Connect O AI N- to V

CC

to disable the op amp. The logic threshold to disable the op amp is approximately V

CC

- 1V.

20 O AI N+

O p Amp Noninverting I nput. When using the internal op amp for additional voltage-positioning gain

( Figure 1) , connect to the positive terminal of the current-sense resistor through a resistor as described in the

Setting Voltage Positioning section.

21 PSI

Power-Status I ndicator I nput. When PSI is pulled low, the M AX1987/M AX1988 immediately enter pulse-

skipping operation, blank the I M VPO K output high, and blank the CLKEN output low.

22 SYSPO K

System Power-G ood I nput. Primarily, SYSPO K serves as the wired NO R junction of the open-drain power-

good signals for the V

CCP

and V

CCM CH

supplies. A falling edge on SYSPO K shuts down the

M AX1987/M AX1988 and sets the fault latch. Toggle SHDN or cycle V

CC

power below 1V to restart the

controller.

23 I M VPO K

O pen-Drain Power-G ood O utput. After output voltage transitions, except during power-up and power-down,

if O UT is in regulation, then I M VPO K is high impedance. I M VPO K is high impedance whenever the slew rate

control is active ( output voltage transitions) . I M VPO K is forced low in shutdown. A pullup resistor on I M VPO K

causes additional finite shutdown current. I M VPO K also reflects the state of SYSPO K and includes a 3ms

( min) delay for power-up.

24 CLKEN

Clock Enable Logic O utput. This inverted logic output indicates when SYSPO K is high and the output voltage

sensed at FB is in regulation. CLKEN is forced low during VI D transitions.

2530 D5D0

Low-Voltage VI D DAC Code I nputs. D0 is the LSB, and D5 is the M SB of the internal 6-bit VI D DAC ( Table 4) .

The D0D5 inputs do not have internal pullups. These 1.0V logic inputs are designed to interface directly with

the CPU. I n all normal active modes ( modes other than suspend mode and boot mode) , the output voltage is

set by the VI D code indicated by the D0D5 logic-level voltages on D0D5. I n suspend mode ( SUS = high) ,

the decoded state of the four-level S0 to S2 inputs sets the output voltage. I n boot mode ( see the Pow er-U p

Sequence section) , the decoded state of the four-level B0 to B2 inputs set the output voltage.

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

16 ______________________________________________________________________________________

Pin Descript ion (cont inued)

PIN NAME FUNCTION

31 DDO

Driver-Disable O utput. This TTL logic output can be used to disable the driver outputs on slave-switching

regulator controllers, such as the M AX1980 forcing a high-impedance condition and making it possible for

the M AX1987/M AX1988 master controller to operate in low-current SK I P mode. DDO goes low 32 R

TI M E

clock cycles after the M AX1987/M AX1988 complete a transition to the suspend mode or deep-sleep voltage

( see the Low -Pow er Pulse Skipping section) . Another 32 clock cycles later, the M AX1987/M AX1988 enter

automatic pulse-skipping operation.

32 BSTM

M ain Boost Flying Capacitor Connection. An optional resistor in series with BSTM allows the DHM pullup

current to be adjusted.

33 LXM M ain I nductor Connection. LXM is the internal lower supply rail for the DHM high-side gate driver.

34 DHM M ain High-Side G ate-Driver O utput Swings LXM to BSTM

35 DLM

M ain Low-Side G ate Driver O utput. DLM swings from PG ND to V

DD

. DLM is forced high after the

M AX1987/M AX1988 power down ( SHDN = G ND) or when the M AX1987 detects an overvoltage fault. The

M AX1988 does not include overvoltage protection.

36 V

DD

Supply Voltage I nput for the DLM and DLS G ate Drivers. Connect to the system supply voltage ( 4.5V to

5.5V) . Bypass V

DD

to PG ND with a 2.2F or greater ceramic capacitor, as close to the I C as possible.

37 PG ND Power G round. G round connection for the low-side gate drivers DLM and DLS.

38 DLS

Secondary Low-Side G ate Driver O utput. DLS swings from PG ND to V

DD

. DLS is forced high after the

M AX1987/M AX1988 power down ( SHDN = G ND) or when the M AX1987 detects an overvoltage fault. The

M AX1988 does not include overvoltage protection.

39 DHS Secondary High-Side G ate-Driver O utput Swings LXS to BSTS

40 LXS Secondary I nductor Connection. LXS is the internal lower supply rail for the DHS high-side gate driver.

41 BSTS

Secondary Boost Flying Capacitor Connection. An optional resistor in series with BSTS allows the DHS pullup

current to be adjusted.

42 V+

Battery Voltage Sense Connection. Used only for PWM one-shot timing. DH_ on-time is inversely proportional

to input voltage over a range of 2V to 28V.

43 SUS

Suspend-M ode Control I nput. When SUS is high, the regulator slews to the suspend voltage level. This level

is set with four-level logic signals at the S0 to S2 inputs. 32 clock cycles after the transition to the suspend-

mode voltage is completed, DDO goes low ( see the Low -Pow er Pulse Skipping section) . Another 32 clock

cycles later, the M AX1987/M AX1988 are allowed to enter pulse-skipping operation.

44 DPSLP

Deep-Sleep Control I nput. When DPSLP is low, the system enters the deep-sleep state and the regulator

applies the appropriate deep-sleep offset. The M AX1987/M AX1988 add the offset measured at the PO S and

NEG pins to the output. 32 clock cycles after the deep-sleep transition is completed, DDO goes low ( see the

Low -Pow er Pulse Skipping section) . Another 32 clock cycles later, the M AX1987/M AX1988 are allowed to

enter pulse-skipping operation.

45 CM P M ain I nductor Positive Current-Sense I nput

46 CM N M ain I nductor Negative Current-Sense I nput

47 CSN Secondary I nductor Negative Current-Sense I nput

48 CSP Secondary I nductor Positive Current-Sense I nput

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

PRELI MI NARY

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

______________________________________________________________________________________ 17

Table 1. Component Selection for Standard Multiphase Applications (Figure 1)

DESIGNATION COMPONENT

I nput Voltage Range* 7V to 24V

VI D O utput Voltage ( D5D0) 1.356V ( D5D0 = 010110)

Boot Voltage ( B0 to B2) 1.372V ( B2 = REF, B1 = REF, B0 = REF)

Suspend Voltage ( S0 to S2) 0.748V ( S2 = V

CC

, S1 = V

CC

, S0 = G ND)

Deep-Sleep O ffset Voltage ( PO S, NEG ) 2.7%

M aximum Load Current ( typ) 40A

I nductor ( L

M

, L

S

)

0.6H

Panasonic ETQ P1H0R6BFA or Sumida CDEP134H-0R6

Switching Frequency 300kHz ( TO N = float)

High-Side M O SFET ( N

H

, per phase) Fairchild ( 2) FDS6694 or Siliconix ( 2) Si4860DY

Low-Side M O SFET ( N

L

, per phase) Fairchild ( 2) FDS6688 or Siliconix ( 2) Si4362DY

I nput Capacitance ( C

I N

)

( 6) 10F, 25V

Taiyo Yuden TM K 432BJ106K M or TDK C4532X5R1E106M

O utput Capacitance ( C

O UT

)

( 3) 470F, 2.5V Sanyo 2R5TPD470M or

( 4) 330F, 2.5V Panasonic EEFUEO D33I XR

Current-Sense Resistor ( R

SENSE

, per phase)

1.5m

Panasonic ERJM 1WTJ1M 5U

*Input voltages less than 7V require additional input capacitance.

Table 2. Component Suppliers

MANUFACTURER PHONE WEBSITE

BI Technologies 714-447-2345 ( USA) www.bitechnologies.com

Central Semiconductor 631-435-1110 ( USA) www.centralsemi.com

Coilcraft 800-322-2645 ( USA) www.coilcraft.com

Coiltronics 561-752-5000 ( USA) www.coiltronics.com

Fairchild Semiconductor 888-522-5372 ( USA) www.fairchildsemi.com

I nternational Rectifier 310-322-3331 ( USA) www.irf.com

K emet 408-986-0424 ( USA) www.kemet.com

Panasonic 847-468-5624 ( USA) www.panasonic.com

Sanyo

65-281-3226 ( Singapore)

408-749-9714 ( USA)

www.secc.co.jp

Siliconix ( Vishay) 203-268-6261 ( USA) www.vishay.com

Sumida 408-982-9660 ( USA) www.sumida.com

Taiyo Yuden

03-3667-3408 ( Japan)

408-573-4150 ( USA)

www.t-yuden.com

TDK

847-803-6100 ( USA)

81-3-5201-7241 ( Japan)

www.component.tdk.com

Toko 858-675-8013 ( USA) www.tokoam.com

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

18 ______________________________________________________________________________________

PRELI MI NARY

OFF

ON

BSTM

DHM

LXM

DLM

V

DD

V

CC

D0

D1

D3

D4

FB

DAC INPUTS

(1V LOGIC)

REF

C

REF

0.22F

C

CCV

270pF

PGND

V+

CCV

NEG

CCI

S0

S1

SUSPEND INPUTS

(FOUR- LEVEL LOGIC)

POS

CSP

ILIM

TIME

SUS

PSI

MODE

CONTROL

C3

100pF

R

TIME

28k

R8

100k

POWER GROUND

ANALOG GROUND

GND

D5

S2

B0

B1

BOOT INPUTS

(FOUR- LEVEL LOGIC)

B2

OAIN-

OAIN+

CMN

CMP

IMVPOK

SYSPOK

R12

100k

R13

100k

R11

100k

C2

1F

TON

FLOAT

(300kHz)

P

O

W

E

R

-

G

O

O

D

L

O

G

I

C

S

I

G

N

A

L

S

R2

750

R3

1.0k

C

CCI

470pF

R9

30.1k

INPUT*

8V TO 24V

L

M

C

IN

N

H(M)

N

L(M)

R

CM

C

BST(M)

0.1F

R10

10

5V BIAS

SUPPLY

C1

2.2F

DDO

SHDN

DPSLP

CLKEN

MAX1987

MAX1988

L

S

C

IN

N

H(S)

N

L(S)

R

CS

C

BST(S)

0.1F

BST

DIODES

R1

1.5k

R7

100k R4

750

R5

1.0k

R6

2.74k

CSN

BSTS

DHS

LXS

DLS

R

CCI

1M

OUTPUT

C

OUT

C

OUT

* LOWER INPUT VOLTAGES

REQUIRE ADDTIONAL

INPUT CAPACITANCE

D2

R14

4.7k

C4

4.7nF

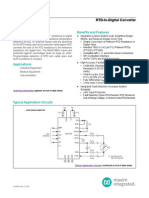

Figure 1. Standard Application C ircuit (M aster)

CONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

Det ailed Descript ion

5V Bias Supply (V

CC

and V

DD

)

The M AX1987/M AX1988 require an external 5V bias sup-

ply in addition to the battery. Typically, this 5V bias sup-

ply is the notebooks 95% efficient 5V system supply.

K eeping the bias supply external to the IC improves effi-

ciency and eliminates the cost associated with the 5V lin-

ear regulator that would otherwise be needed to supply

the PWM circuit and gate drivers. If standalone capability

is needed, the + 5V bias supply can be generated with

an external linear regulator.

The 5V bias supply must provide V

CC

( PWM controller)

and V

DD

( gate-drive power) , so the maximum current

drawn is:

I

BI AS

= I

CC

+ f

SW

( Q

G ( LO W)

+ Q

G ( HI G H)

)

= 10mA to 100mA ( typ)

where I

CC

is 1.7mA ( typ) , f

SW

is the switching frequency,

and Q

G ( LO W)

and Q

G ( HIG H)

are the M O SFET data sheets

total gate-charge specification limits at V

G S

= 5V.

V+ and V

DD

can be connected together i f the i nput

power source is a fixed 4.5V to 5.5V supply. I f the 5V

bias supply is powered up prior to the battery supply,

the enable signal ( SHDN going from low to high) must

be delayed until the battery voltage is present to ensure

startup.

Free-Running, Const ant On-Time PWM

Cont roller wit h I nput Feedforward

The Q uick-PWM control architecture is a pseudo-fixed-

frequency, constant-on-ti me, current-mode regulator

with voltage feedforward ( Figure 2) . This architecture

relies on the output filter capacitors ESR to act as the

current-sense resistor, so the output ripple voltage pro-

vides the PWM ramp signal. The control algorithm is

simple: the high-side switch on-time is determined sole-

ly by a one-shot whose period is inversely proportional

to input voltage, and directly proportional to output volt-

age and the di fference between the mai n and sec-

ondary inductor currents ( see the O n-Tim e O ne-Shot

section) . Another one-shot sets a minimum off-time. The

on-time one-shot is triggered if the error comparator is

low, the low-side switch currents are below the current-

limit threshold, and the minimum off-time one-shot has

timed out. The controller maintains 180 out-of-phase

operation by alternately triggering the main and sec-

ondary phases after the error comparator drops below

the output voltage set point.

On-Time One-Shot (TON)

T he core of each phase contai ns a fast, low-j i tter,

adjustable one-shot that sets the high-side M O SFETs

on-time. The one-shot for the main phase simply varies

the on-time in response to the input and feedback volt-

ages. The main high-side switch on-time is inversely

proportional to the input voltage as measured by the V+

input, and proportional to the feedback voltage ( V

FB

) :

where K is set by the TO N pin-strap connection ( Table

3) and 0.075V is an approximation to accommodate the

expected drop across the low-side M O SFET switch.

The one-shot for the secondary phase varies the on-

time in response to the input voltage and the difference

between the mai n and secondary i nductor currents.

Two identical transconductance amplifiers integrate the

difference between the master and slave current-sense

signals. The summed output is internally connected to

C C I , allowing adjustment of the integration time con-

stant with a compensation network connected between

C C I and FB. The resulting compensation current and

voltage are determined by the following equations:

where Z

CCI

is the impedance at the CCI output.

The secondary on-time one-shot uses this integrated

signal ( V

CCI

) to set the secondary high-side M O SFETs

on-time. When the main and secondary current-sense

signals ( V

CM

= V

CM P

- V

CM N

and V

CS

= V

CSP

- V

CSM

)

become unbalanced, the transconductance amplifiers

adj ust the secondary on ti me, whi ch i ncreases or

decreases the secondary inductor current until the cur-

rent-sense signals are properly balanced:

This algorithm results in a nearly constant switching fre-

quency and balanced inductor currents, despite the

lack of a fixed-frequency clock generator. The benefits

of a constant switching frequency are twofold: first, the

t K

V V

V

K

V V

V

K

I Z

V

M ain O n time SecondaryCurrent

Balance Correction

O N ND

CCI

I N

FB

I N

CCI CCI

I N

( )

.

.

( ) (

)

2

0 075

0 075

_

,

_

,

_

,

+

I g V V g V V

V V I Z

CCI M CM P CM N M CSP CSN

CCI FB CCI CCI

+

( ) ( )

t

K V V

V

O N M AI N

FB

I N

( )

( . )

+ 0 075

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

Dual-Phase, Quick-PWM Cont rollers for I MVP-I V

CPU Core Power Supplies

______________________________________________________________________________________ 19

PRELI MI NARYCONFIDENTIAL INFORMATIONRESTRICTED TO INTEL IMVP LICENSEES

M

A

X

1

9

8

7

/

M

A

X

1

9

8

8

frequency can be selected to avoi d noi se-sensi ti ve

regi ons such as the 455kHz I F band; second, the

inductor ripple-current operating point remains relative-

ly constant, resulting in easy design methodology and

predi ctable output-voltage ri pple. T he on-ti me one-

shots have good accuracy at the operati ng poi nts

speci fi ed i n the Electrical C haracteristics ( 10% at

200kHz and 300kHz, 12% at 550kHz) . O n-ti mes at

operating points far removed from the conditions speci-

fi ed i n the Electrical C haracteristics can vary over a

wider range. For example, the 550kHz setting typically

runs about 10% slower with inputs much greater than

12V due to the very short on-times required.

O n-times translate only roughly to switching frequencies.

The on-times guaranteed in the Electrical C haracteristics

are influenced by switching delays in the external high-

side M O SFET. Resistive losses, including the inductor,

both M O SFETs, output capacitor ESR, and PC board

copper losses in the output and ground tend to raise

the switching frequency at higher output currents. Also,

the dead-time effect increases the effective on-time,

reduci ng the swi tchi ng frequency. I t occurs only i n