Professional Documents

Culture Documents

Apostila - Exp.3 PDF

Uploaded by

gustavofaggion0 ratings0% found this document useful (0 votes)

28 views22 pagesOriginal Title

Apostila - Exp.3.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

28 views22 pagesApostila - Exp.3 PDF

Uploaded by

gustavofaggionCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 22

ESCOLA POLITCNICA DA UNIVERSIDADE DE SO PAULO

Departamento de Engenharia Mecatrnica e de Sistemas Mecnicos

PMR 2433 Eletrnica Analgica e Digital

2

o

Semestre 2014

Experincia 3

CIRCUITOS SEQUENCIAIS & FPGA (REV. A)

A FPGA (Field Programmable Gate Array) uma das tecnologias mais avanadas para a implementao de

circuitos lgicos digitais. So dispositivos facilmente programveis, de alta densidade, com os quais podemos

implementar a um custo muito baixo sistemas digitais equivalentes a milhes de transistores.

Esta experincia uma introduo ao ambiente de desenvolvimento Foundation Series para a

programao de FPGAs. Vamos programar e testar uma FPGA utilizando a placa de desenvolvimento Digilab,

da Digilent. O projeto do circuito feito no computador com o programa Foundation Series, e o arquivo de

configurao resultante transferido para a FPGA atravs da porta paralela do computador.

Alm desta apostila, voc vai precisar do manual de usurio da placa de desenvolvimento Digilab XL, que

ser utilizada no laboratrio para testar nossos projetos em FPGA. Opcionalmente, voc pode obter o manual do

software Foundation Series, que usaremos para projetar os circuitos. Esse manual est disponvel no endereo

http://www.poli.usp.br/d/pmr2433. No estritamente necessrio ler esse manual, mas essa leitura prvia

certamente facilitar sua vida durante a aula.

Usaremos esse sistema de desenvolvimento para estudar alguns circuitos sequenciais utilizando latches e

flip-flops. Portanto, faa uma reviso do captulo 6 do livro texto.

PARTE I TEORIA

3.1 FPGA (Field Programmable Gate Array)

Internamente, uma FPGA composta por clulas padro que podem ser programadas individualmente para

constituir funes lgicas de n entradas e m sadas, chamadas de PLB (programmable logic block). As m sadas de um

PLB podem ser conectadas a suas prprias entradas (formando circuitos realimentados) ou a entradas de outros

PLBs, atravs de matrizes de interconexes denominadas de SM (switch matrix). As SMs tambm podem ser

programadas individualmente. Como uma FPGA possui milhares de PLBs e SMs, temos um dispositivo capaz de

implementar desde funes lgicas simples a sistemas digitais bastante complexos.

A Figura 3.1 ilustra a estrutura simplificada de uma FPGA. Neste exemplo, cada PLB contm duas

memrias programveis (do tipo RAM), cada uma contendo 16 posies de 1 bit. Essa memria chamada LUT

(look up table), e cada uma delas permite implementar qualquer funo booleana de 4 variveis de entrada, como se

fossem tabelas da verdade eletrnicas.

Note que, neste exemplo, temos n = 8 e m = 2. Observe que a estrutura desse exemplo de PLB no

permite realizar qualquer funo lgica de 8 variveis, e sim duas funes de 4 variveis cada. Alm disso, a

matriz de interconexo SM no permite conectar quaisquer PLBs. Mas estas restries podem ser superadas,

interconectando-se vrios PLBs.

A Figura 3.2 mostra como implementar um somador completo de 1 bit em uma PLB. Repare que a LUT

superior (G) reproduz a tabela da verdade do vai-um (ci+1) e a inferior (H) contm a tabela da verdade do i-simo

bit da soma (si). Como so funes de trs variveis, uma das entradas de cada LUT no utilizada. No caso da

LUT G, por exemplo, a entrada g1 foi deixada em aberto, e portanto o contedo da LUT deve ser o mesmo tanto

para g1 = 0 como para g1 = 1 (na figura, isto indicado com X na coluna g1 de endereos). Analogamente, na

LUT H, a entrada h4 no foi utilizada.

Uma FPGA tem vrios pinos que podem ser configurados para servir de entradas ou de sadas para as

funes programadas. A programao de PLBs, SMs e pinos armazenada internamente em memria voltil, o

que significa que uma pastilha pode ser reprogramada milhares de vezes. Isso as torna uma excelente tecnologia

para a prototipagem rpida de sistemas digitais. Projetistas de circuitos integrados, por exemplo, costumam

utiliz-las para testar por partes o projeto de CIs complexos, como um microprocessador moderno.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 2

(a) (b)

Figura 3.1 a) Estrutura matricial de uma FPGA, com PLBs interconectadas por SMs

b) Exemplo de PLB, composta por duas LUTs de 4 variveis

Figura 3.2 Somador completo (ci+1 si) implementado com uma PLB

3.2 Programao

A programao interna de PLBs e SMs normalmente bastante complexa, mesmo para se implementar funes

lgicas bem simples. Para facilitar a sua vida, os fabricantes de FPGAs investem pesadamente no

desenvolvimento de softwares integrados para a programao automtica desses dispositivos. So os chamados

compiladores de silcio. A ideia permitir que voc faa o projeto utilizando portas lgicas e bibliotecas de funes,

de forma hierrquica. O compilador cuida de converter seu projeto em sequncias de bits que posteriormente so

transferidas para a memria da FPGA.

Em linhas gerais, o ciclo de desenvolvimento com uma FPGA envolve as seguintes etapas.

Projeto digital (design entry): o projeto propriamente dito do circuito que ser implementado dentro da

FPGA. Em projetos mais simples, utilizam-se normalmente editores grficos para se desenhar o diagrama

lgico do circuito o chamado modo de captura esquemtica (schematic entry). Em casos mais complicados,

podem ser utilizadas linguagens de programao (HDL, hardware description language), como as linguagens

ABEL, VHDL e Verilog. So linguagens que lembram C, por exemplo, onde funes lgicas so definidas

por expresses algbricas (do tipo Y = A & B) e chamadas de sub-rotinas.

Simulao funcional: simula o funcionamento do circuito projetado com portas lgicas, sem considerar os

atrasos de propagao, para que se possa verificar se a lgica implementada corresponde ao esperado.

Implementao: quando o projeto compilado para formar os bits de programao da FPGA. hora de se

verificar se o modelo de FPGA a ser utilizada (target) comporta o projeto, isto , se o CI contm PLBs e SMs

em quantidade suficiente para implementar o circuito desejado.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 3

Verificao: simula eletricamente o circuito implementado na FPGA, considerando tempos de atraso, para se

verificar se o circuito capaz de operar na velocidade desejada, e se problemas como harzard no afetam o

funcionamento do circuito.

Nesta experincia, utilizaremos o software Foundation Series, da Xilinx. Trata-se de um ambiente de

desenvolvimento profissional bastante complexo. Nesta aula, procuraremos aprender a usar as funes

elementares do programa. Ao utiliz-lo em sala, procure ler os manuais on-line disponveis no menu Help e, em

algumas situaes, teclando-se F1 aps selecionar algum elemento das janelas. As dicas desta apostila visam dar a

voc um ponto de partida, mas ao se limitar apenas a elas, voc acabar com uma viso muito fragmentada do

poderoso sistema que ter em mos.

3.3 Placa de Desenvolvimento Digilab

No laboratrio, vamos testar os circuitos projetados utilizando a placa de desenvolvimento Digilab XL, da

Digilent. Ela contm uma FPGA Spartan XCS10 PC84, da Xilinx, de 84 pinos, capaz de acomodar circuitos

equivalentes a at 10.000 portas lgicas, aproximadamente. A programao da FPGA feita por um cabo

conectado porta paralela de um computador.

A placa contm ainda vrios conectores e dispositivos que permitem verificar o funcionamento do

circuito programado na FPGA. Dentre eles, temos 4 displays de 7 segmentos, 8 chaves de duas posies, 8 leds

(Light-Emitting Diodes), 4 botes de contato momentneo (push buttons). Veja, em anexo, o manual de usurio da

placa. Nesta experincia, utilizaremos apenas esses dispositivos citados.

Veja a pgina 12 do manual. A tabela indica em que pinos da FPGA esses dispositivos esto conectados,

e essa informao deve ser levada em conta no projeto do circuito. Por exemplo, para acender e apagar o led

LD1, devemos conectar o pino 69 da FPGA a uma sada do circuito projetado.

Veja na pgina 13 do manual um exemplo de um circuito que controla o led LD1 atravs de um AND

entre as chaves SW1 (pino 28 da FPGA) e SW2 (pino 27). Note que, para configurar um pino da FPGA como

entrada, devemos incluir no projeto dois elementos: o IPAD e o IBUF. O primeiro determina o nmero do pino

a ser usado, e o segundo insere um circuito eltrico (buffer) que permite utilizar o sinal presente no pino como

entrada de portas lgicas.

Analogamente, a configurao de um pino da FPGA como sada exige os elementos OBUF (buffer eltrico

de sada) e OPAD (definio do pino).

3.4 Contadores Sncronos

Uma aplicao bastante simples porm muito importante dos flip-flops a construo de contadores binrios. A

Figura 3.3 mostra como construir um contador de um bit, usando um flip-flop tipo D com a sada invertida

realimentada na entrada. A cada borda de subida do sinal C, a sada Q se inverte de 0 para 1 e de 1 para 0,

sucessivamente.

C

D Q

Q

0 1 3 2

Q

D

C

Figura 3.3 Contador de um bit

Repare que este circuito somente funciona porque h atrasos envolvidos. Se todos os sinais mudassem

instantaneamente, o valor de Q ficaria indefinido pois D igual a Q e teramos Q = Q (estranho, no?) aps a

borda de clock. No entanto, como o sinal D leva alguns nano-segundos para se inverter aps uma mudana em Q,

o prximo valor da sada Q aps a borda de clock ser o inverso do valor atual depois de um pequeno atraso,

conforme mostra a carta de tempos da Figura 3.3. Ou seja, para o instante k, temos Q

k+1

= (Q

k

).

Repare que o sinal C uma onda quadrada ideal, enquanto que mudanas nos sinas D e Q aparecem

como bordas inclinadas, indicando que as mudanas de nvel levam algum tempo para se consumarem. Note que

exageramos o atraso do sinal D com relao a Q. Como mostra a figura, instantes antes da borda 0 do clock,

temos Q = 0 e (devido ao inversor) D = 1. Aps a borda 0, a sada Q do flip-flop copia o valor de D, e depois de

um certo atraso D se inverte.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 4

Podemos cascatear vrios contadores de 1 bit para formar um contador binrio de n bits. Mas para isso

vamos usar flip-flops tipo JK, que so mais adequados para esta aplicao. A Figura 3.4 ilustra um flip-flop JK

com entrada de clear (CLR) assncrono, que zera a sada Q quando em 1, independentemente do sinal de clock C.

Com CLR = 0, a sada Q atualizada na borda de subida do clock, conforme o valor das entradas de comando J e

K. A entrada J leva a sada a 1, enquanto que K zera a sada; para JK = 00, a sada se mantm no valor atual, e

para JK = 11 a sada se inverte.

CLR C J K Q

k+1

1 X X X 0 (clear assncrono)

0

0 0 Q

k

(mantm)

0

0 1 0 (reset)

0

1 0 1 (set)

0

1 1 (Q

k

) (inverte)

Figura 3.4 Flip-flop tipo JK e sua tabela caracterstica

Podemos usar esse flip-flop para construir um contador sncrono de 2 bits, denominado xxCB2, ilustrado

na Figura 3.5. A entrada CLR zera o contador, assincronamente com o sinal de clock C. A entrada CE, chamada

count enable, habilita a contagem quando em 1, fazendo as sadas Q1 Q0 contarem ciclicamente de 00 a 11 nas

bordas de subida do clock. Na tabela, a notao Q[1:0] representa a palavra de dois bits Q1Q0 (nessa ordem), e

a notao usada pelo software de programao de FPGA Foundation Series para dar nomes a barramentos (ou

buses) constitudos por vrios bits numerados, como o caso dos bits Q1 e Q0.

CLR CE C Q[1:0]

k+1

CEO TC

1 X X 0 0 0 0 (clear assncrono)

0 0 X Q[1:0]

k

0 Q1.Q0 (clock desabilitado)

0 1

Q[1:0]

k

+ 1 Q1.Q0 Q1.Q0 (incremento mdulo 4)

Figura 3.5 Contador sncrono de 2 bits, com clear assncrono (CLR) e count enable (CE)

As sadas TC (terminal count) e CEO (count-enable output) so sadas de status (ou flags) do contador. A sada

TC quando em 1 indica que a contagem atingiu o valor mximo (ou seja, Q[1:0] = 11). O flag CEO tambm

indica o fim de contagem, mas vale 1 somente se, alm de termos Q[1:0] = 11, o contador tambm se encontra

habilitado (CE = 1). Por esse motivo, a sada CEO geralmente usada para fazer o cascateamento desses

contadores, como se ver mais a frente.

A Figura 3.6 mostra do diagrama lgico do circuito do contador. Repare que, por ser um circuito

sncrono, o sinal de clock o mesmo para os dois flip-flops. O primeiro flip-flop complementa a sada Q0 a cada

borda de clock, desde que esteja habilitado (CE =1) e no haja sinal de clear (CLR = 0). Nessas mesmas condies

(CE = 1 e CLR = 0), o segundo flip-flop complementa a sada Q1 sempre que a anterior for 1, ou seja, quando o

bit menos significativo atinge seu final de contagem. As portas AND2 geram as sadas TC e CEO, seguindo a

tabela da Figura 3.5.

Figura 3.6 Circuito do contador sncrono de dois bits

A carta de tempos da Figura 3.7 ilustra a diferena entre CEO e TC. A contagem em Q1Q0 atinge 11 no

instante de clock 3, ao mesmo tempo em que o contador desabilitado (CE = 0), fazendo com que CEO

permanea em zero. A sada CEO vai para 1 somente aps o instante 4, em que o contador novamente

habilitado (CE = 1). Por sua vez, a sada TC vai a 1 j no instante 4, to logo a contagem atinge 11.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 5

X

X

0 1 2 3 4 5 6

C

Q[1:0]

CEO

CE

TC

...

...

...

...

...

00 10 01 01 00 11 XX

CLR

Figura 3.7 Carta de tempos do contador de dois bits

Para deixar a carta de tempos mais concisa, representamos apenas as bordas de subida do sinal de clock

por um trem de impulsos, e os bits Q1 e Q0 so representados na forma de barramento condensado (Q[1:0]),

onde indicamos apenas as transies e o valor da contagem em binrio. Essa carta de tempos tambm ilustra um

fato comum em circuitos sncronos. Repare que a entrada CE tambm varia sincronamente com o sinal de clock C

nas bordas 0, 3 e 4. Na borda 0, a contagem em Q[1:0] no se altera porque temos CE = 0 no instante

imediatamente anterior borda, e o mesmo acontece na borda 4. J na borda 3, CE = 1 antes da borda e o

contador incrementa Q[1:0]. Concluindo: em circuitos sncronos, considere o valor presente nas entradas no

momento anterior borda de clock.

3.5 Cascateamento de contadores sncronos

A sada CEO serve para cascatear contadores. Nesse caso, basta interligar todas entradas C ao mesmo sinal de

clock, e ligar a sada CEO entrada CE do contador seguinte, como mostra a Figura 3.8.

Fazendo a entrada CE igual a zero, o primeiro contador desabilitado e a sada CEO_A tambm vai a

zero, garantindo que o segundo contador tambm seja desabilitado. Quando CE estiver ativo e o primeiro

contador atingir o final de contagem (Q1Q0 = 11), teremos CEO_A = 1 e o segundo contador ser habilitado.

Na borda seguinte do clock, as sadas Q3Q2 sero incrementadas juntamente com Q1Q0.

Figura 3.8 Contador de quatro bits usando dois contadores em cascata.

A carta de tempos da Figura 3.9 ilustra o mecanismo de cascateamento usando os mesmos sinais de

entrada da Figura 3.7, na qual inclumos os sinais CEO_A e Q[3:2]. Na borda de clock 3, o primeiro contador

desabilitado, desabilitando tambm o segundo (CEO_A = 0), e a contagem de ambos se mantm a mesma na

borda 4. No instante 5, ambos esto habilitados e a contagem nos bits Q[3:2] e Q[1:0] passa de 00 11 para 01 00.

2 3 4 5 6

00 10 11

01 00

...

...

...

...

...

...

...

...

01

...

CLK

Q[1:0]

CEO_A

CE

Q[3:2]

01

Figura 3.9 Carta de tempos resumida do contador de quatro bits em cascata

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 6

3.6 Divisores de Freqncia

Contadores tambm so conhecidos como divisores de frequncia. Suponha, por exemplo, que o sinal de clock C

na Figura 3.6 seja uma onda quadrada peridica de frequncia fC. Como a sada Q0 se inverte a cada borda de

subida do clock, temos em Q0 uma onda quadrada de frequncia fC/2 (ou com o dobro do perodo).

Analogamente, em Q1 teramos uma frequncia fC/4 e assim por diante.

3.7 Aplicao: Acionamento do Mostrador de Sete Segmentos

A placa Digilab tem quatro mostradores de sete segmentos. Cada segmento formado por um led, um dispositivo

semicondutor que estudaremos futuramente, representado na Figura 3.10 pelos tringulos com traos. Por hora,

acredite que um led se acende quando uma corrente eltrica o atravessa no sentido apontado pelo tringulo. O

terminal de entrada da corrente (base do tringulo) se chama anodo, e o de sada (trao) se chama catodo.

H quatro terminais de alimentao (chamados de anodo comum), sendo um para cada mostrador, que

so acionados atravs sinais A1 a A4 ligados aos pinos P44, P40, P39 e P38 respectivamente (confira na pgina 12

do manual da placa). Os sinais CA, CB, ... CF e DP comandam cada um dos sete segmentos e o ponto decimal.

Por exemplo, o segmento a (trao superior) se acende sempre que fazemos CA = 0, aterrando o catodo do led a e

permitindo que uma corrente flua atravs dele.

a

b

c

d

e

f

g

dp

A

i

CA

CB

CC

CD

CE

CF

CG

DP

A

i

...

CA CB CG DP

a b g dp

Figura 3.10 Estrutura do mostrador de sete segmentos

Hexa 0 1 2 3 4 5 6 7

Caracter

Hexa 8 9 A B C D E F

Caracter

Figura 3.11 Padro de apresentao de dgitos hexadecimais em 7 segmentos (sem o ponto decimal)

A Figura 3.11 mostra como esse mostrador pode ser utilizado para apresentar (de forma um tanto

precria) dgitos hexadecimais, de 0 a F. Dessa forma, para mostrar o dgito 0, por exemplo, devemos fazer os

sinais de CA a CF em zero para acender os leds de a a f, e fazer CG e DP iguais a um para apagar os leds g e dp;

para mostrar o dgito 2 fazemos apenas CB e CC iguais a zero, e assim por diante.

Na FPGA, os catodos CA a CF esto ligados aos pinos P51 a P45. O catodo DP (do ponto decimal) no

est ligado FPGA, mas est disponvel no conector J1 da placa (confira na pgina 11 do manual).

Note, no entanto, que os catodos (CA a CG) so comuns aos quatro mostradores. Ou seja, ativando os

quatro anodos (A1 a A4) ao mesmo tempo, os mostradores mostraro o mesmo dgito imposto nos catodos CA a

CG. Como faramos, ento, para mostrar dgitos diferentes nos mostradores?

A soluo acionar um anodo de cada vez, ciclicamente, e utilizar multiplexadores para colocar nos

catodos o padro de cada dgito, de forma sincronizada com a ativao dos anodos. Ou seja, cada mostrador

piscaria um dgito diferente, um de cada vez. Se a taxa de varredura dos mostradores for alta (acima de trinta

vezes por segundo, aproximadamente), ficaremos com a impresso que os mostradores esto sempre ligados, j

que no conseguiremos mais observar o efeito pisca-pisca.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 7

A Figura 3.12 mostra um circuito para mostrar quatro dgitos hexadecimais (DA a DD) nos mostradores

da placa Digilent. Os dgitos entram em um multiplexador qudruplo de 4 bits (bloco H2), que a cada instante

passa adiante apenas um deles. O bloco H3 faz a converso do nmero em binrio para o padro correspondente

para apresentao no mostrador de sete seguimentos (o ponto decimal foi omitido no esquema). O bloco H1

representa um contador cclico de 2 bits, que gera os bits de seleo do multiplexador e tambm do decodificador

(bloco H3), garantindo a sincronizao entre o dgito selecionado no mux e o mostrador a ser ligado.

CA Z

0

A

1 A

2

A

3 A

4

Conversor

Hex / 7 seg

Z

3

Mux

qudruplo

de 4 bits

DA[3:0]

DB[3:0]

DC[3:0]

DD[3:0]

Contador

Mdulo 4

CG

CLOCK

Decodificador

2:4

Q

1

Q

0

H1

H2

H3

H4

ENABLE

Figura 3.12 Circuito para acionamento dos mostradores de sete segmentos.

O sinal de CLOCK deve ter uma frequncia superior a 4 x 30 = 120 Hz. Essa a taxa mnima necessria

para que cada mostrador seja ligado pelo menos 30 vezes por segundo. O sinal ENABLE permite ligar e desligar

todos os mostradores conjuntamente, desabilitando o decodificador e o contador.

Para construir esse circuito no laboratrio, voc poder usar os componentes mostrados na Figura 3.13.

Figura 3.13 Componentes para o projeto do acionador de mostrador de sete segmentos

O CB2CE um contador de dois bits, com entradas de Clock Enable (CE = 1 habilita a contagem) e

Clear assncrono (CLR = 1 zera o contador, independentemente do sinal de Clock). A sada TC (Terminal Count)

vai a 1 sempre que a contagem em Q1Q0 atinge o valor mximo neste caso, 11 em binrio. A sada CEO

simplesmente um AND entre TC e a entrada CE.

As macros MUX4_4_1 e 7SEG implementam o multiplexador qudruplo e o conversor de cdigo para

sete segmentos. Os diagramas lgicos destas duas macros esto em anexo.

Finalmente, o bloco D2_4E um decodificador 2:4 com entrada de Enable (E). Quando o decodificador

se encontra habilitado (E = 1), a sada Di endereada pelas entradas A1A0 vai a um, enquanto as demais

permanecem em zero; quando E = 0, todas as sadas permanecem em zero. Observe que este decodificador

diferente do 74138 usado em experincia anterior, que tinha sadas ativas em zero.

3.8 PR-RELATRIO

O pr-relatrio composto pelos EXERCCIOS a seguir e os contidos na Parte II. Voc dever entregar o pr-

relatrio at o comeo da aula de sua turma, caso contrrio no poder fazer a experincia.

Trata-se de um documento de sua autoria que voc estar submetendo avaliao. Portanto, faa-o com

esmero. Os exerccios podem ser resolvidos a lpis, mas as respostas finais devem ser escritas caneta. Faa-os

com antecedncia, para ter tempo para tirar dvidas e fazer todos os exerccios.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 8

Durante a aula, voc dever elaborar o relatrio das atividades, fazendo as ANOTAES pedidas na parte

prtica. O relatrio tambm individual. Procure faz-lo mo livre e com esmero: isto uma habilidade

importante para quem vai precisar se comunicar graficamente em reunies de trabalho!

Leia com ateno todas as atividades da Parte II antes da aula, e no apenas os exerccios.

Assim, voc ter uma noo das atividades a serem desenvolvidas e perder menos tempo durante a aula.

Traga para a aula a apostila IMPRESSA. Os pontos importantes das atividades devem estar destacados

ou grifados. Na aula, essas anotaes sero avaliadas e contaro na nota final da experincia.

PARTE II PRTICA

LEIA tudo com ateno

NO tente apenas REPRODUZIR as figuras sem ler a apostila.

ATENO: h um problema de configurao no Windows Vista que IMPEDE que o primeiro projeto

implementado no computador seja reimplementado uma segunda vez! Para contornar, sempre que o computador

for religado ou seja feito um login, primeiramente carregue o projeto XLA5, clique em

Project | Clear Implementation Data e implemente, conforme descrito a seguir.

Atividade 1 Teste da placa

Anotao 1a Anote no cabealho do relatrio: nome dos integrantes da equipe, nmero da bancada, nmero da

placa XLA5 e a hora de incio das atividades.

Veja o diagrama lgico XLA5 em anexo. No canto esquerdo, h trs blocos, CB8 e CB16 e CD4CE,

conectados em sequncia. Isto forma um contador, cuja funo dividir a frequncia do clock de entrada presente

em P13. Por hora, acredite apenas que CD4CE conta ciclicamente de 0 a 9, em binrio, e o bloco H4 faz a

converso para acionar os displays de 7 segmentos, que esto ligados aos pinos P45 a P51.

Atente para o restante do circuito, concentrado na parte inferior direita. Ele implementa uma lgica que

acende os leds atravs das chaves e dos botes da placa. Vamos testar a placa XL com esse circuito. Os arquivos

necessrios para este teste se encontram compactados no arquivo XLA5.ZIP, disponvel no servidor, no endereo

\\ts02-00\pmr2433.

(Lembre-se: os resultados finais dos exerccios devem ser escritos caneta!)

Exerccio 1 Determine a equao lgica que faz o i-simo led LDi acender, em funo das chaves (SWi) e dos

botes (BTNi).

Copie o arquivo XLA5.ZIP do servidor para o diretrio C:\PMR2433\_ARQ (e SOBREESCREVA se

ele j existe). Carregue o software de programao: menu Start Programs Xilinx Foundation Series Project

Manager. Na janela de abertura (Getting Started), clique em Cancel, para iniciar o programa sem carregar nenhum

projeto. Na barra de menus do Project Manager, clique em File, e em seguida em Restore Project... Entre no

diretrio C:\PMR2433\_ARQ, e abra o arquivo XLA5.ZIP.

Na janela Restore Project Wizard..., localize o campo Destination e digite C:\PMR2433\seugrupo,

onde seugrupo o nome de guerra do seu grupo. Ateno: ao dar nomes a elementos, arquivos e diretrios dentro

do Foundation, no use nomes com mais de 8 caracteres, nem acentos ou espaos em branco!

Deixe o box Open restored project selecionado e clique em Avanar. Clique em Yes to All para

ignorar todos os arquivos j existentes. O projeto ser descompactado e carregado pelo programa.

Abra o editor esquemtico, dando um duplo clique no arquivo XLA51.SCH que aparece na sub-janela

Files ( esquerda). Voc ver o diagrama lgico do circuito de teste (anexo XLA5). Vamos agora programar a

FPGA com este projeto. Retorne janela principal do programa Project Manager, e clique no menu Project

Clear Implementation Data. Isso fora o programa a passar por todos os passos da implementao (e vai

convenientemente ativar o bug do Windows em cima do desse projeto de teste, que no poder mais ser alterado).

Caso contrrio, se algum j tiver implementado o projeto XLA5 antes de voc, o programa detectar que no

necessrio fazer nada e o bug do Windows aparecer quando voc for trabalhar no seu projeto!

Ainda na janela do Project Manager, clique agora no boto Implementation que aparece na janela

Flow direita, e em seguida no boto RUN na janela que se abre (no clique em OK, pois isto apenas

fecha a janela).

O programa vai implementar o projeto (ou seja, compilar a descrio do circuito) para gerar o arquivo

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 9

de configurao (ou programao) da FPGA. Acompanhe os passos dessa transcrio:

Translate e Map: converte seu projeto em funes lgicas que podem ser implementadas nos PLBs

Place and Route: decide em quais PLBs da FPGA as funes lgicas sero programadas e faz a programao

das interconexes entre elas (SMs).

Configure: gera o arquivo binrio (extenso bit) que ser enviado FPGA para program-la.

VERIFIQUE: se o programa no mostrou os passos citados sendo executados, RELEIA as instrues

desta atividade at este ponto!

Exerccio 2 Por que deve-se clicar em Project | Clear Implementation Data antes de implementar o projeto?

Conecte o cabo da porta paralela do PC na placa e ligue a fonte de alimentao. ATENO: NO deixe

coisas metlicas sob a placa! Isso pode causar um curto-circuito entre os pontos de solda.

Agora, verifique se a chave SW9 est na posio PROG e transfira o arquivo bit gerado para a FPGA

da placa. Isso feito com o programa C:\Xilinx4\XLA5\ConfigXP.pif (h um link na rea de trabalho).

Esse aplicativo deve ser executado com as prerrogativas de administrador para poder acessar a porta

paralela do computador. Para isso, clique sobre ele com o boto da direita do mouse e clique em seguida em

Executar como Administrador. Na janela Configure Digilab que o programa abre, clique no menu Control

Configure Device from File, e selecione o arquivo C:\PMR2433\seugrupo\XLA5\XLA5.bit.

Verifique se o circuito est funcionando corretamente. Em funcionamento normal, os displays

mostraro os dgitos de 0 a 9, ciclicamente. Acione os leds atravs das chaves e dos botes e verifique se isso

condiz com o previsto no exerccio. Verifique se todos os botes, chaves e leds esto funcionando.

ATENO: Ao contrrio do painel LSD utilizado nas experincias anteriores, uma chave da placa

Digilab envia FPGA o nvel lgico 0 quando est para frente, e 1 quando est para trs. O boto envia 1

quando pressionado.

Anotao 1b Verifique se a resposta no seu pr-relatrio condiz com o funcionamento dos leds observado nesta

atividade. Caso contrrio, comente os erros detectados.

Atividade 2 Restaurando os Arquivos de Projeto

O disco de seu computador contm alguns arquivos que sero utilizados nessa experincia, tais como macros

prontas e esquemticos incompletos. Copie o arquivo 2433_E3.ZIP do servidor (\\ts02-00\pmr2433) para o

diretrio C:\PMR2433\_ARQ (mesmo que ele j exista).

Volte janela do programa Project Manager. Clique no menu File Restore Project... Selecione o

arquivo 2433_E3.ZIP no diretrio C:\PMR2433\_ARQ. Na janela Restore Project Wizard... , campo

Destination, digite C:\PMR2433\seugrupo, onde seugrupo o nome de guerra do seu grupo.

Deixe o box Open restored project selecionado e clique em Avanar. Clique em Yes to All para

ignorar todos os arquivos j existentes. O projeto ser descompactado e carregado pelo programa. No vamos

trabalhar com esse projeto. Ao invs disso, vamos copi-lo com outro nome para o seu diretrio de trabalho.

Clique no menu File | Copy Project. O campo Source Project, j deve estar preenchido com

C:\PMR2433\seugrupo\2433_E3.PDF. No campo Destination Directory, digite c:\PMR2433\seugrupo. No campo

Destination Name, digite algo como xxFF, onde xx so as 2 primeiras letras do nome seugrupo. Clique em OK.

Podemos agora carregar o projeto copiado no Project Manager. Clique no menu File | Open Project, e

localize o arquivo xxFF.PDF no diretrio C:\PMR2433\seugrupo. Selecione o arquivo e clique em Open.

Estamos prontos para comear a experincia.

Anotao 2a Acrescente o nome do diretrio de trabalho no cabealho do relatrio.

Atividade 3 Latch RS Negativo

Vamos construir uma macro para implementar um latch RS negativo. Uma macro como uma sub-rotina, que

pode ser inserida vrias vezes em outros projetos.

Dispare o editor de esquemticos: no menu Tools, selecione Design Entry | Schematic Editor (ou clique

no cone correspondente na sub-janela Flow). O editor cria o arquivo de nvel hierrquico mais alto do projeto,

xxFF1.sch. O latch ser uma macro, de nvel hierrquico inferior (a famosa caixa-preta).

Para criar a macro, no menu Tools, selecione Symbol Wizard. Esse mdulo define as interfaces de

entrada e sada da macro, e cria um smbolo (a cara da caixa-preta). Passe pela janela de apresentao do mdulo

e avance para a janela Design Wizard Contents. No campo Symbol Name, digite xxNRS (xx so as iniciais do

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 10

seu grupo) e selecione Schematic no campo Contents. Clique em Next.

Na janela Design Wizard Ports, defina os sinais _R e _S de entrada e os sinais _Q e Q de sada (o trao

indica que os sinais so ativos em 0). Clique em New, e digite _R no campo Name, e selecione Input no campo

Direction. Repita esse processo para criar a entrada _S.

Em seguida, crie a sada _Q (clique em New, digite _Q no campo Name e selecione Output no campo

Direction) e Q. Neste ponto, a definio de sua macro deve ter o aspecto mostrado na Figura 3.14. Avance para

a janela seguinte com Next.

Figura 3.14 Definio da macro xxNRS

Na janela seguinte, Attributes, digite no campo Longer Comment algo como Latch RS negativo (deixe

o campo Shorter em branco). Clique em Next, e na janela seguinte em Finish. O programa constri o esqueleto

da macro, j com os pontos de entrada e sada rotulados.

Complete o esquema, conforme mostra a Figura 3.15, e salve o arquivo (menu File | Save). Uma dica:

insira primeiro todos os smbolos (no caso, dois NANDs), acionando o modo de inserso atravs do menu Mode

| Symbols, ou clicando no cone de um AND que aparece na barra lateral esquerda. Voc ver uma extensa lista

de nomes mneumnicos dos smbolos. Digitando no campo inferior dessa janela, fica mais fcil para encontrar o

smbolo desejado. Selecione e inclua-o no projeto, clicando na posio desejada. Para incluir outras cpias, clique

em um smbolo j posicionado e posicione a nova cpia.

Figura 3.15 Macro xxNRS

OBSERVE: a sada Q deve ser a da porta NAND ligada entrada _S!

Ao incluir um smbolo, estamos instanciando a macro correspondente a ele, ou seja, estamos fisicamente

inserindo no nosso projeto os componentes do circuito representado pela macro. Esses componentes sero

repetidos tantas vezes quanto a macro for instanciada no projeto.

Complete as conexes ativando o menu Mode | Draw Wires. Clique num terminal de um smbolo e

depois em outro para lig-los. Clicando em posies intermedirias, possvel definir uma rota. Para inserir uma

derivao em um fio, basta clicar sobre ele no ponto desejado.

ATENO: para conectar o terminal de um smbolo ao terminal de outro, no basta sobrep-los ao

posicionar os smbolos. Uma conexo somente se d atravs de um fio. Por isso, posicione os smbolos

mantendo uma certa distncia entre os terminais a serem conectados.

Voc ainda pode mover os smbolos e fios, copiar, colar... etc. Consulte o manual on-line do editor, no

menu Help | Schematic Editor.

Verifique se est tudo em ordem. Clique no menu Options | Integrity Test for Current Sheet. Se houver

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 11

algo errado, aparecero mensagens na tela (Console) do Project Manager. Nesse caso, corrija, teste de novo, e

salve. IMPORTANTE: se precisar alterar a macro mais tarde, NUNCA a abra com o comando File | Open...

use o comando File | Open macro, ou clique sobre ela com o boto da direita e clique em Hierarchy Push.

Agora, vamos fazer um teste rpido na macro xxNRS que voc acabou de editar, ligando uma

instanciao da macro s chaves e leds da placa Digilab, e ver se est funcionando direito.

Volte folha xxFF1. Insira nela a macro xxNRS: clique no menu Mode | Symbols, ou clique no cone

correspondente na barra esquerda. O smbolo xxNRS est no fim da lista, debaixo da hierarquia do nosso

projeto (xxFF). Complete as ligaes, como mostra a Figura 3.16. Atente para a ordem dos pinos de entrada e

sada nas faces laterais do smbolo U1. Se voc no incluiu os sinais na ordem descrita anteriormente,

provavelmente eles estaro diferentes. Voc pode corrigir isso, atravs do editor de smbolos: no Schematic

Editor, clique no menu Tools | Symbol Editor. Na janela do Symbol Editor, abra o arquivo xxNRS atravs do

menu File | Open, e reordene os terminais arraste um por vez para a posio correta.

Figura 3.16 Circuito de teste do latch xxNRS

Lembre-se que necessrio mapear cada IPAD e OPAD em um pino da FPGA. Clique duas vezes em

um deles para abrir a janela Symbol Properties. Na parte inferior da janela (Parameters), selecione LOC no

campo Name, e digite a identificao do pino no campo Description (por exemplo, P59). Clique em Add, caso

contrrio isso no ter efeito. Veja a Figura 3.17. Clicando sobre a marca preta direita de LOC, voc pode

ajustar a forma como esse parmetro ser exibido no desenho: uma marca exibir apenas o valor do parmetro

(P59), duas exibir LOC=P59, e nenhuma marca far com que o programa no exiba o parmetro.

Experimente.

Figura 3.17 Configurao de um IPAD

Os identificadores dos fios, tais como BTN1 e LD1, podem ser inseridas clicando-se duas vezes

sobre os fios. Isto abre a janela Net Name. Digite o nome e clique em OK.

VEFIRIQUE: se na barra de ttulo da janela do Schematic Editor contar algo como Schematic Editor

[Non-Project xxNRS.SCH], voc NO est editando a macro! Volte ao comeo desta atividade e RELEIA-A

at este ponto.

Por fim, salve o arquivo. Clique no boto Implementation do programa Project Manager para gerar a

implementao do circuito. Descarregue o arquivo bit (c:\pmr2433\seugrupo\xxFF\xxFF1.bit) na placa, com o

programa ConfigXP, conforme descrito na Atividade 1.

Teste o funcionamento do latch acionando os botes. O boto BTN1 seta o latch, acendendo o led LD1

e apagando o led LD2. J o boto BNT2 causa o reset do latch, apagando LD1 e acendendo LD2.

Anotao 3a Faa uma tabela da verdade em funo do estado dos botes BTN1 e BNT2 (0 ou 1) e tabele os

correspondentes valores de _R, _S , Q e _Q. Lembre-se que os botes em repouso fornecem nvel lgico 0 e que

esto ligados s entradas _R e _S do latch por meio de inversores.

Anotao 3b Verifique o que acontece quando os dois botes so pressionados ao mesmo tempo. Em seguida,

tente soltar os botes tambm ao mesmo tempo. O estado final sempre o mesmo em vrias tentativas? Discuta

a razo do comportamento observado.

Anotao 3c Anote a hora atual. Apresente o circuito funcionando e suas concluses para o professor.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 12

Exerccio 3 Faa a tabela caracterstica (ou da verdade) do latch RS negativo.

Exerccio 4 Por que foram inseridos inversores entre os botes BTN 1 e 2 e as entradas _R e _S do latch?

Atividade 4 Contador Sncrono com 4 Flip-Flops tipo JK

Projete um contador sncrono de 4 bits, adicionando mais dois flip-flop JK e portas lgicas no circuito da Figura

3.6 (no utilize dois contadores de 2 bits em cascata!). No pr-relatrio, desenhe um circuito de teste no qual o

boto BTN1 esteja ligado entrada de clock C, o boto BTN4 entrada CLR, e a chave SW1 entrada CE. As

sadas Q3Q2Q1Q0 devem ser ligadas aos leds LD5 a LD8; TC e CEO devem ser ligados aos leds LD2 e LD3; e o

sinal de clock C deve ser ligado ao led LD1.

Inicialmente, encerre o simulador e o Schematic Editor. Na janela do Project Manager, remova o arquivo

xxFF1.SCH da hierarquia do projeto. Para isso, clique sobre ele para seleciona-lo e clique no menu Document |

Remove, confirmando em seguida (o arquivo no apagado e permanece no disco; apenas retirado da lista de

arquivos que compe o projeto). Em seguida, clique no menu Document | Add... e selecione o arquivo

TestCB4.SCH (que deve estar no seu diretrio de projeto c:\pmr2433\seugrupo\xxFF).

Abra esse arquivo no Schematic Editor. Repare que o sinal de clock C do contador gerado por um

latch RS positivo, denominado XXRS. O boto BTN1 zera o clock, enquanto que o boto BTN2 o leva a 1. O

boto BTN4 permite zerar o contador, e a entrada count enable CE pode ser controlada pela chave SW1.

Abra em seguida a macro XXCB4; para isso, clique sobre ela com o boto da direita e clique em

Hierarchy Push, ou clique no menu File | Open macro... e selecione essa macro (lembre-se: NO use o comando

File | Open...). Note que ela contm apenas o contador de 2 bits que foi descrito no incio da apostila. Complete

e modifique esse circuito seguindo o seu projeto, e salve.

VERIFIQUE: se no tab Files da janela do Project Manager constar outros arquivos com extenso .sch

na hierarquia do projeto (que deveria se chamar algo como xxFF), alm do arquivo TestCB4.sch, voc

DEIXOU DE REMOVER o arquivo anterior da hierarquia. Volte e RELEIA esta atividade at este ponto.

Complete e modifique esse circuito seguindo o seu projeto, e salve. Feche o Schematic Editor,

implemente o contador e configure a FPGA (usando o programa ConfigXP).

Teste o circuito: mantenha a chave SW1 em 1, pressione alternadamente os botes BTN1 e 2 para gerar o

sinal de clock e acompanhe as sadas nos leds. Coloque a chave SW1 em 0 algumas vezes antes de fazer o clock

subir, e verifique se o contador fica desabilitado corretamente.

Em particular, teste o contador com os sinais CLR e CE mostrados na Figura 3.18: desabilite o contador

quando a contagem atingir 3 (Q[3:0] = 0011) e o valor mximo 15 (Q[3:0] = 1111). Note: quando Q[3:0] chegar a

1111, as sadas TC e CEO (leds LD2 e 3) devem ir para 1; fazendo CE = 0 (chave SW1), apenas CEO deve zerar.

CE

CLR

C

15 16 17 18 4 5 6 0 1 3 2 . . .

. . .

. . .

Figura 3.18 Sinais de excitao.

Anotao 4a Faa mo livre a carta de tempos do contador para o caso particular descrito acima (CE muda de

1 para 0 com Q[3:0] igual a 0011 e 1111). NO necessrio desenhar todos os clocks entre 0 e 18 indique a

continuidade por reticncias. Desenhe as formas de onda das sadas Q[3:0] de forma condensada.

Anotao 4b Anote a hora atual e mostre o contador funcionando para o professor. Caso encontre algum

erro no projeto dos pr-relatrios de membros da equipe, aponte-o e descreva o efeito causado.

Exerccio 5 Faa o diagrama lgico do contador e do circuito de teste conforme descrito acima, incluindo os

elementos necessrios (I/O PADs, I/O BUFs, LOCs) para ligar o contador placa. Veja quais pinos usar no

enunciado desta atividade.

Exerccio 6 Considere que os sinais da Figura 3.18 sejam aplicados s entradas do contador da Figura 3.8

(NO o contador de 4 bits que voc projetou o contador construdo com 2 contadores em cascata!).

Desenhe as formas de onda das sadas Q[1:0], CEO_A, TC_A, Q[3:2], nesta ordem desenhe Q[1:0] e Q[3:2]

de forma condensada, e com capricho! Elas devem estar sincronizadas com o sinal de clock, caso contrrio

sero de pouca utilidade. LEMBRE-SE: considere o estado de um sinal de entrada no instante imediatamente

anterior a uma borda por exemplo, na borda 0 de clock, o sinal CE vale 1.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 13

Exerccio 7 Determine o valor de contagem nas sadas Q[3:0] aps as bordas de clock em 3, 4 e 5.

Atividade 5 Controlador do Display de 7 Segmentos

Vamos criar uma macro para implementar o acionador de mostrador de sete segmentos.

Comece ativando a ferramenta Symbol Wizard (menu Tools do Schematic Editor), e d ao smbolo um

nome como xxDsDrv (no esquea de definir Contents como Schematic). A Figura 3.19 mostra o smbolo

resultante ao final da definio dos pinos. As entradas DA, DB, DC e DD so barramentos (buses), de quatro bits

cada. Para defini-las, clique em New na janela Ports, digite o nome do bus no campo Name (por exemplo, DA), e

ajuste a dimenso do bus para [3:0] no campos Bus (ao lado do campo Name). Defina as demais entradas e sadas

da macro: habilitao EN e clock CLK. As sadas so os sinais de ativao dos anodos (A1 a A4) e dos catodos

(CA a CG) dos mostradores.

Figura 3.19 Definio do smbolo xxDsDrv

As linhas grossas indicam barramentos (buses). Os barramentos de entrada podem ser ligados

diretamente aos barramentos da macro MUX4_4_1, como mostra a Figura 3.20. Para desenhar um barramento

no Schematic Editor, clique em Mode | Draw Bus (ou clicando no cone correspondente). Para terminar o bus,

clique duas vezes sobre ele.

Figura 3.20 Ligao entre barramentos

As macros MUX4_4_1 e 7SEG j esto disponveis no disco do seu computador, como parte da

biblioteca xxFF, e podem ser instanciadas (isto , inseridas) dentro do seu circuito. Complete o esquema do

circuito e salve. Dica: os barramentos de entrada podem ser ligados diretamente aos barramentos da macro

MUX4_4_1, como mostra a Figura 3.20.

Nota: para impor entradas em 0 ou 1, existem os componentes GND e VCC na biblioteca.

Vamos testar o acionador utilizando o circuito de um cronmetro, mostrado na Figura 3.21. O sinal de

clock gerado pelo smbolo OSC4, cuja sada F490 fornece um sinal de 400 Hz. Esse sinal ser utilizado para

fazer a varredura do mostrador, e portanto cada mostrador piscar a uma taxa de 100 vezes por segundo.

O contador CB2CE divide a frequncia do sinal por 4, resultando em uma base de tempo de um

centsimo de segundo. frente deste, temos quatro contadores CD4CE de quatro bits que contam ciclicamente

de 0 a 9 (so os chamados contadores de dcada ou contadores BCD). Portanto, cada um deles divide a

frequncia por 10. Como o primeiro contador acionado a cada 0,01 s, temos no barramento DD a contagem

decimal em centsimos de segundo. Analogamente, em DC temos a contagem em dcimos de segundo, e assim

por diante.

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 14

Figura 3.21 Circuito do cronmetro

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 15

Note como o cascateamento dos contadores feito. O sinal de clock de 400 Hz conectado em todas as

entradas C, mas apenas o contador CB2CE (de mdulo 4) est habilitado continuamente. A sada CEO deste

contador habilita o primeiro contador CD4CE. Como vimos na Parte I, essa sada CEO vai a um somente nos

perodos em que a contagem passa pelo mximo (3, neste caso) e portanto o primeiro contador CD4CE

incrementado apenas a cada 4 ciclos de clock. Pelo mesmo princpio, o segundo contador CD4CE

incrementado a cada 40 ciclos, o terceiro a cada 400 ciclos, e o ltimo a cada 4000 ciclos.

O boto BTN4 est ligado s entradas CLR (Clear) dos contadores. Dessa forma, o cronmetro zerado

sempre que pressionamos esse boto.

No Project Manager, remova do projeto o arquivo utilizado na atividade anterior: clique sobre o nome do

arquivo na rvore do projeto e clique no menu Document | Remove, e confirme.

Voc no precisar construir todo o circuito da Figura 3.21. No diretrio do projeto j existe um arquivo

parcialmente feito. No Schematic Editor, use o menu File | Open para abrir o arquivo CronSemi.SCH no

diretrio C:\PMR2433\seugrupo\xxFF. Em seguida, salve-o com outro nome, por exemplo xxCron.SCH (onde

xx so as iniciais do seu grupo), no diretrio do seu projeto, usando o menu File | Save as. Para incluir o arquivo

no projeto, clique no menu Hierarchy | Add Current Sheet to Project.

Complete o esquemtico com a instanciao da macro xxDsDrv que voc criou.

Para conectar os pinos do primeiro CD4CE ao bus DD, clique no menu Mode | Draw Bus Taps. Em

seguida, basta clicar num pino que o programa automaticamente faz a ligao com o bus que estiver em frente.

Em seguida, necessrio indicar qual via do bus foi ligada (por exemplo, DD0). Para isso clique duas vezes no

fio e digite o nome da via no campo Net Name.

Implemente o circuito e transfira para a FPGA. Verifique o funcionamento do circuito.

Anotao 5a Se o seu projeto do acionador de display (feito no pr-relatrio) apresentou algum erro, descreva-o

no relatrio, juntamente com a correo feita.

Exerccio 8 Analise o diagrama da macro 7SEG em anexo, que converte um nmero binrio de 0 a 15,

codificado nos 4 bits de entrada B3B2B1B0, para o padro de acionamento de um mostrador de 7 segmentos

com anodo comum. Uma sada Ci em 0 faz o led i correspondente acender, e vice-versa. Inspecionando o

circuito, indique que leds sero apagados quando nas entradas B3B2B1B0 tivermos:

a.1) 0010 a.2) 0111 a.3) 1101

Exerccio 9 Faa o diagrama lgico do circuito de acionamento do mostrador de sete segmentos, mostrado na

Figura 3.12. O circuito a ser implementado o que se encontra delimitado pela linha tracejada; o display de 7

segmentos no faz parte dele, j que um componente separado. No seu projeto, utilize os elementos

mostrados na Figura 3.13. No se esquea de aterrar a entrada CLR do contador, que no ser usada.

Atividade 6 Run / Stop

Modifique o circuito do cronmetro para incluir mais dois botes: Run (BTN1) e Stop (BTN2).

Ao se pressionar o boto Run, o cronmetro deve disparar. Pressionando-se Stop, a cronometragem se

detm; nessa condio, pressionando-se Run novamente o cronmetro continua a partir da contagem em que

parou.

Ateno: o boto Clear (BTN4) somente pode zerar o cronmetro quando este estiver parado. Dica: use

um latch para controlar a habilitao dos contadores (pino CE).

Anotao 6a Faa o diagrama lgico do circuito modificado de forma resumida: no inclua PADS e BUFS;

havendo componentes repetidos com ligaes iguais, desenhe somente o primeiro e o ltimo com reticncias

entre eles. No entanto, indique os botes e leds da placa XLA usados nas entradas e sadas do circuito.

Anotao 6b Anote a hora atual e mostre o circuito funcionando para o professor.

Atividade 7 Finalizao

Deixe a bancada em ordem e limpa. Falhas nesse procedimento sero penalizadas.

Check list Verifique e anote no relatrio os seguintes itens.

i. Equipamentos Liste todos os equipamentos usados. Todos esto desligados? Em especial, certifique-se

que o COMPUTADOR e o MONITOR estejam DESLIGADOS (NO deixe o computador em

STAND-BY).

PMR2433 Eletrnica Analgica e Digital Experincia 3 (rev. A) Celso M. Furukawa

Escola Politcnica da USP Departamento de Engenharia Mecatrnica 2

o

sem. 2014 16

ii. Multmetro Os cabos das pontas de prova do multmetro esto arrumados? Deixe o multmetro sobre o

tampo baixo da bancada, para que possamos conferir facilmente se est desligado.

iii. Osciloscpio Os cabos das pontas de prova do osciloscpio esto arrumados?

iv. Cabos Liste todos os cabos de conexo usados. Os cabos foram recolocados nos lugares de origem? (O

cabo paralelo da placa deve ser deixado conectado ao computador)

v. Placa XLA a placa foi embalada no plstico anti-esttico e guarda da na caixa com sua fonte?

vi. Emprstimos Usou alguma coisa de outra bancada? O qu? Foi devolvido?

vii. Defeitos Encontrou algum defeito? Preencheu a Comunicao de Defeito?

viii. Limpeza A bancada est limpa?

Equipamentos com defeito devem ser deixados na prpria bancada. Cabos, cabinhos e outros acessrios

com defeito devem ser entregues ao professor, juntamente com a Comunicao de Defeito.

Entregue o relatrio feito em sala e o seu pr-relatrio

Copyright Digilenet, Inc. Digilab XL Users Manual 3/3

Board Graphic

C

2

4

L

D

9

J

8

U

6

C

2

3

C

2

0

S

W

9

PROG

PORT

C22

C21

C19

R3

R

P

1

5

R

P

1

6

R

P

1

2

R

P

1

4

RP13

C

1

8

U

4

J

3

R

4

R

6

R

5

C

L

K

2

CLK1

C

1

7

C

1

3C12

C16

C

1

1

U

3

C

1

0

C

9

C

1

4

C

1

5

J

7

C

8

C

7

R

P

1

1

R

P

1

0

R

O

M

R

2

C

3

C

5

J

6

C

2

J

5

C

4

C

6U

2

J

4

A

U

D

J

2

R

P

8

R

P

9R

1

U

1

C

1

J

1

B

N

C

B

T

N

1

B

T

N

2

B

T

N

3

B

T

N

4

R

P

7

R

P

6

L

D

1

L

D

2

L

D

3

L

D

4

L

D

5

L

D

6

L

D

7

L

D

8

R

P

5

R

P

4

S

W

1

S

W

2

S

W

3

S

W

4

S

W

5

S

W

6

S

W

7

S

W

8

Q

4

Q

3

Q

2

Q

1

RP1

R

P

2

R

P

3

DSP2

DSP1

WWW.DIGILENT.CC DIGILAB XL

D

I

G

I

L

E

N

T

,

I

N

C

2

0

0

0

VDD

GND

SW1

SW2

SW3

SW4

SW5

SW6

SW7

SW8

LD1

LD2

LD3

LD4

LD5

LD6

LD7

LD8

LDG

BTN1

BTN2

VDD

GND

O2

O1

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

GND

ASFT

ATIP

VDD

GND

DP

CA

CB

CC

CD

CE

CF

CG

A1

A2

A3

A4

RXD

TXD

O4

O5

CLK2

BTN3

BTN4

VDD

GND

O3

PINT

PAS

PDS

PWE

VDD

VDD

VDD

GND

GND

GND

BNCS

BNCP

PWE

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PAS

PINT

PRS

PWT

PDS

GND

GND

O1

O2

O3

O4

O5

R

G

B

HS

VS

RXD

TXD

PS2C

PS2D

1

Copyright Digilenet, Inc. Digilab XL Users Manual 12/12

FPGA

The Digilab board can accommodate a Xilinx Spartan XCS05, XCS10, XCS05XL, and XCS10XL

FPGA in the 84-pin PLCC socket (the XL parts require a 390 ohm R6 for 3.3V operation). Any of

these SRAM-based FPGAs may be programmed using a parallel cable or an SPROM (see above). The

parallel cable provides an inexpensive programming solution that is compatible with the Xilinx CAD-

tool cable detection software, so that the FPGA can be programmed without leaving the Xilinx

environment. Refer to the Xilinx Spartan data sheet (http://www.xilinx.com/partinfo/spartan.pdf) for

technical data regarding the FPGAs.

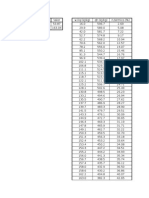

Pin # Function Pin # Function Pin # Function

1

GND

29 O1 57 BTN3

2

Vdd

30

M1_NC

58 BTN2

3 PWE 31

GND

59 BTN1

4 PD0 32

MODE

60 LD8

5 PD1 33

Vdd

61 LD7

6 PD2 34

M2_NC

62 LD6

7 PD3 35 CLK2 63

Vdd

8 PD4 36 O2 64

GND

9 PAS 37 O3 65 LD5

10 PRS 38 A4 66 LD4

11

Vdd

39 A3 67 LD3

12

GND

40 A2 68 LD2

13 CLK1 41 INIT (O4) 69 LD1

14 PDS 42

Vdd

70 LDG

15 PWT 43

GND

71 DIN (O5)

16 PD5 44 A1 72 DOUT (RXD)

17 PD7 45 CG 73

CCLK

18 PD6 46 CF 74

Vdd

19 SW8 47 CE 75 TXD (PINT)

20 SW7 48 CD 76

GND

21

GND

49 CC 77 R

22

Vdd

50 CB 78 G

23 SW6 51 CA 79 B

24 SW5 52

GND

80 HS

25 SW4 53

DONE

81 VS

26 SW3 54

Vdd

82 PS2C

27 SW2 55

PROG

83 PS2D

28 SW1 56 BTN4 84 PINT

The table on the right shows all

FPGA pin connections. In this

pin-list, gray boxes indicate

dedicated pins that are not

available for use. Italicized

names indicate dual-purpose

pins; for these pins, the Xilinx

function is shown first followed

by Digilabs assignment in

parenthesis.

Some FPGA signals, including

the LED drive signals and the

unassigned (or open) signals are

available on the J1 prototyping

connector. Care should be taken

to ensure that these signals are

not simultaneously driven by

both the FPGA and by other

drivers. If the FPGA is loaded

in the U3 socket and external

circuits must drive these signals,

it would be best to tri-state the

FPGA signals.

The parallel port connector can

be used as the FPGA

programming port or as a

parallel port. When

downloading a circuit that

drives the parallel port data

signals, ensure that the signals

are not driven until SW9 has

been moved to the PORT

position. See the parallel port

demo project on the Digilent

web site.

2

Copyright Digilenet, Inc. Digilab XL Users Manual 13/13

Any CAD-tool-designed circuit that requires fewer than about 5K 10K gates can be programmed into

the Xilinx FPGA. However, the circuit description must first be transformed into the format required

by the FPGA. This transformation proceeds in several steps, typically beginning with an EDIF, VHDL,

or Verilog file format and ending with a Xilinx bit file format. Xilinx (of course) produces a tool that

accomplishes this transformation, which is available in the Xilinx Alliance and Foundation products

(see the Xilinx web site). Although other methods of transforming files may be available, only the

Xilinx solution has been used with the Digilab board. Although the use of the Xilinx tools is beyond

the scope of this document, Xilinx has several good tutorials and helpful documentation available at

their web site.

All signals on the Digilab board that connect the buttons, switches, and LEDs to the J1 connector are

connected to the Xilinx FPGA chip as well. Any circuit implemented in the FPGA can use the buttons

and switches as inputs and the LEDs as outputs. When the Digilab board was fabricated, the buttons,

switches, and LEDs were connected to particular pins on the FPGA (see the table in the previous

section for all FPGA pin definitions). To connect an FPGA-based circuit to these devices, you must

include information in your schematic to map circuit inputs and outputs to particular FPGA pins.

Mapping is accomplished by including special components in your schematic called IPADs, IBUFs,

OPADs and OBUFs. These components exist solely to allow you to define physical pin connections,

and so they only need be used in circuit schematics that you intend to download.

Once you have a complete and error-free schematic, you may add IBUFs and IPADs to all inputs, and

OBUFs and OPADs to all outputs. Then, the IPADs and OPADs can be connected to particular pins

by double-clicking the pads and entering the LOC parameter and pin number in the appropriate

fields (Name and Description, respectively). In the example circuit below, two switches (SW1 on pin

P28 and SW2 on pin P27) are connected via an AND gate to LED1 (LD1 on pin P69). If this circuit

were downloaded to the FPGA, then LD1 would illuminate whenever SW1 and SW2 were asserted.

Once all IPADs, IBUFs, OPADs, and OBUFs have been added and edited with pin locations, you can

begin the implementation process by choosing the Implementation button from the Xilinx main

screen. In the first dialog box that appears, choose Yes to update the netlist from the schematic editor.

In the second dialog box, make sure the device is S10PC84 and speed is 3 before proceeding; the

version and revision names can use the defaults. Press the Run button, and then wait for the status

window showing Translate, Map, Place & Route, Timing, and Configure processes to terminate.

Before proceeding, make sure that the Digilab board is powered on and connected to the PC via the

parallel cable, and that SW9 is in the PROG position. Then select the Programming option from the

Xilinx main window, and hardware debugger from the subsequent dialog box. The cable should be

auto-detected; if not, manually choose the parallel cable in the Cable communications dialog box.

AND2

IBUF

IBUF

OBUF

OPAD

IPAD

IPAD

LOC=P28

LOC=P27

LOC=P69

For simulation purposes, labes can be added to wires between the IBUF's and the circuit.

Labels are added by doule-clicking the wire and entering the name in the dialog box.

"LOC" parameters are added by double-clicking the pad symbol and entering LOC in the Parameters

Name feild and Pnn in the Parameters Description feild, and then pressing Add and OK.

3

Celso M. Furukawa

Escola Politcnica da USP

PMR

Project: PMR2433

Macro: 7SEG

Date: 8/21/00

Date Last Modified: 9/10/02

D4_16E

A0

A1

A2

A3

D0

D1

D10

D11

D12

D13

D14

D15

D2

D3

D4

D5

D6

D7

D8

D9

E

OR4

OR6

OR4

OR5

OR6

OR5

OR4

VCC

CG

CA

CB

CC

CD

CE

CF

B0

B2

B1

B3

Celso M. Furukawa

Escola Politcnica da USP

PMR

Project: PMR2433

Macro: MUX4_4_1

Date: 5/5/02

Date Last Modified: 9/10/02

M

4

_

1

E

D

0

D

1

D

2

D

3 E

O

S

0

S

1

VCC

M

4

_

1

E

D

0

D

1

D

2

D

3 E

O

S

0

S

1

M

4

_

1

E

D

0

D

1

D

2

D

3 E

O

S

0

S

1

M

4

_

1

E

D

0

D

1

D

2

D

3 E

O

S

0

S

1

DA[3:0]

DB[3:0]

DC[3:0]

DD[3:0]

S0

S1

Z0

Z1

Z2

Z3

DA0 DA1 DA2 DA3

DB0 DB1 DB2 DB3

DC0

DD0

DC1

DD1

DC2

DD2

DC3

DD3

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

E E

F F

G G

H H

Xilinx Corporation

2100 Logic Drive

San Jose, CA 95124

Project: XLA5

Sheet: XLA51

Date: 8/21/00

Date Last Modified: 4/18/02

OBUF

P69

OPAD

OR2

OR2

OBUF

P68

OPAD

OR2

OR2

OBUF

P67

OPAD

OR2

OR2

OBUF

P66

OPAD

OR2

OR2

OBUF

P65

OPAD

IBUF

IBUF

OBUF

P62

OPAD

P19

IPAD

P20

IPAD

OBUF

P61

OPAD

P23

IPAD

IBUF

OBUF

P60

OPAD

H4

B0

B1

B2

B3

CA

CB

CC

CD

CE

CF

CG

P24

IPAD

CD4CE

C

CE CEO

CLR

Q0

Q1

Q2

Q3

TC

IBUF

OR4

P57

IPAD

IBUF

P28

IPAD

P59

IPAD

P58

IPAD

CB8CE

C

CE CEO

CLR

Q[7:0]

TC

P40

OPAD

P39

OPAD

OBUF

OBUF

OBUF

OBUF

P51

OPAD

P50

OPAD

P49

OPAD

P48

OPAD

IBUF

P56

IPAD

P25

IPAD

IBUF

OBUF

P38

OPAD

IBUF

OBUF

P13

IPAD

OBUF

BUFG

OBUF

CB16CE

C

CE CEO

CLR

Q[15:0]

TC

P46

OPAD

P47

OPAD

OBUF

P45

OPAD

OBUF

OBUF

VCC

P44

OPAD

P26

IPAD

IBUF

P27

IPAD

IBUF

IBUF

IBUF

Q[7:0]

VCC

VCC

Q7

GND

You might also like

- Abnt NBR 14724 Trabalhos Acadêmicos - ApresentaçãoDocument6 pagesAbnt NBR 14724 Trabalhos Acadêmicos - ApresentaçãoJosé Antonio Meira da Rocha47% (17)

- Relatório 2 - Correção Do Fator de PotênciaDocument4 pagesRelatório 2 - Correção Do Fator de PotênciaericlesmauricioNo ratings yet

- Diretrizes de Elaboração Do Trabalho FinalDocument21 pagesDiretrizes de Elaboração Do Trabalho FinalgustavofaggionNo ratings yet

- Planilha de Simulação, MicroturbinaDocument32 pagesPlanilha de Simulação, MicroturbinagustavofaggionNo ratings yet

- Escola Politécnica Da Universidade de São Paulo Departamento de Engenharia MecânicaDocument3 pagesEscola Politécnica Da Universidade de São Paulo Departamento de Engenharia MecânicagustavofaggionNo ratings yet

- Apostila 5 - Chavetas e EstriasDocument39 pagesApostila 5 - Chavetas e EstriasEduardo MartiniNo ratings yet

- Instrumentação Básica para Operadores de RefinariaDocument98 pagesInstrumentação Básica para Operadores de RefinariaEduardo BandeiraNo ratings yet

- Dimensionamento ApontadeiraDocument19 pagesDimensionamento ApontadeiragustavofaggionNo ratings yet

- Circuito RC - Medidas de corrente e tensão durante o carregamentoDocument7 pagesCircuito RC - Medidas de corrente e tensão durante o carregamentoPablo GabrielNo ratings yet

- Manual da Central de Alarmes Safira L-XXXADocument61 pagesManual da Central de Alarmes Safira L-XXXAReinaldo Souza0% (1)

- Hangar MmaDocument35 pagesHangar MmaAlisson RamosNo ratings yet

- Lista 5 - Marcone Gabriel Da SilvaDocument3 pagesLista 5 - Marcone Gabriel Da SilvaMARCONE GABRIEL DA SILVANo ratings yet

- Diagrama Unifilar simplificadoDocument27 pagesDiagrama Unifilar simplificadoLarissaNo ratings yet

- Manual técnico de sistema de som compacto MHC-RG77Document33 pagesManual técnico de sistema de som compacto MHC-RG77gustavo0% (1)

- Circuitos em SérieDocument5 pagesCircuitos em SérieLuiz Lemes Barbosa NetoNo ratings yet

- Gs - OC16 SG 406Document2 pagesGs - OC16 SG 406itamarpereiraNo ratings yet

- Configuração de LEDs, teclado e displays no PIC16F877ADocument4 pagesConfiguração de LEDs, teclado e displays no PIC16F877AEvandro Fernandes LedemaNo ratings yet

- Catálogo Peças Diversas - WertuoDocument13 pagesCatálogo Peças Diversas - Wertuomarianilsasousamoreira458No ratings yet

- KLYSTRON e MagnetronDocument6 pagesKLYSTRON e MagnetronHenrique NetoNo ratings yet

- Roteiro Curso Qi ElétricoDocument6 pagesRoteiro Curso Qi ElétricoISAAC MOURA DA SILVANo ratings yet

- Motor SolenoideDocument13 pagesMotor SolenoideJoão Henrique0% (1)

- Check List nr12Document3 pagesCheck List nr12jvborgptcNo ratings yet

- Contadores e registradoresDocument8 pagesContadores e registradoresVinicius MendonçaNo ratings yet

- Visita técnica à subestação da Cermoful descreve sistemas de energia elétricaDocument10 pagesVisita técnica à subestação da Cermoful descreve sistemas de energia elétricaJOÃO PAULONo ratings yet

- Sucatas de cabos e fios de alumínioDocument47 pagesSucatas de cabos e fios de alumínioFelipe CarlosNo ratings yet

- Medidor compacto de tensão e corrente para painéis elétricosDocument1 pageMedidor compacto de tensão e corrente para painéis elétricosWellington CamargoNo ratings yet

- Canticle 2Document7 pagesCanticle 2Inok Pinto QUICAXIAMONo ratings yet

- Experimento 1 - Osciloscópio de Raios CatódicosDocument6 pagesExperimento 1 - Osciloscópio de Raios CatódicosMurilo Aguiar SilvaNo ratings yet

- 2.2 Orientacoes Projeto SubestacaoDocument5 pages2.2 Orientacoes Projeto SubestacaoEL Projetos e Interiores Emanoel LucenaNo ratings yet

- Cubículos MT SF6 Catálogo TécnicoDocument12 pagesCubículos MT SF6 Catálogo TécnicoFabianoNo ratings yet

- Manual operação GPSDocument33 pagesManual operação GPSjorgeNo ratings yet

- Audio Amps m3 A6 ProjectDocument19 pagesAudio Amps m3 A6 ProjectJoão Pedro de Sá FlorentinoNo ratings yet

- Autoridades e Responsabilidades Do Operador de SubestaçãoDocument18 pagesAutoridades e Responsabilidades Do Operador de SubestaçãoJaime SousaNo ratings yet

- Manual do usuário do ventilador eXtendDocument114 pagesManual do usuário do ventilador eXtendRenatoMonteiroNo ratings yet

- Lista de exercícios de eletromagnetismoDocument3 pagesLista de exercícios de eletromagnetismoMontuNo ratings yet

- Manual Instruções VHF UHF Transceptor iV82 iU82Document51 pagesManual Instruções VHF UHF Transceptor iV82 iU82Estúdio André LuísNo ratings yet

- Transformador TrifásicoDocument36 pagesTransformador TrifásicoNuno Lopes100% (2)