Professional Documents

Culture Documents

ModelSim Tutorial and Installation Guide

Uploaded by

reach.tarunp95100 ratings0% found this document useful (0 votes)

546 views10 pagesThis is the installation guide and a short tutorial for ModelSim PE student edition.

UCI Fall 2014 EECS31L

Original Title

ModelSim tutorial and installation guide

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis is the installation guide and a short tutorial for ModelSim PE student edition.

UCI Fall 2014 EECS31L

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

546 views10 pagesModelSim Tutorial and Installation Guide

Uploaded by

reach.tarunp9510This is the installation guide and a short tutorial for ModelSim PE student edition.

UCI Fall 2014 EECS31L

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 10

1

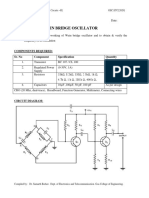

Digital Design Laboratory (EECS/CSE 31L)

Installation guide and short tutorial for Mentor Graphics

ModelSim PE Student Edition 10.3c

Prepared by: Tarun Prakash

EECS Department

Henry Samueli School of Engineering

University of California, Irvine

October 4, 2014

Introduction

In this document we will cover the basics of Installing ModelSim, compiling and simulating

VHDL/Verilog code.

Please note this tutorial is targeted to Windows users. If you are a MAC user, we suggest you

install a windows virtual machine which lets you run Windows on your MAC. There are many

tutorials available on the internet to install virtual machine.

Installation and Setup

This is a step by step guide for installation and set-up of ModelSim PE Student Edition 10.3c.

1. Download ModelSim PE Student Edition from

http://www.mentor.com/company/higher_ed/modelsim-student-edition

2. After the download is complete, a 243MB .exe file should be available on your PC.

3. Double click on the .exe file to begin installation process.

4. Make sure you agree to Mentor Graphics End-User License agreement during

installation.

2

5. At the end of the installation process, click on finish and the browser window will open

with the license request form. The license request form should look like this.

6. Complete all of the form fields with extra attention to email address field and submit the

request form.

7. Once youve submitted your license request form, you will receive an email with the

subject line ModelSim Student Edition License which contains student_license.dat

file.

8. Please note, this student_license.dat file is mapped to a specific .exe file and the host

computer. You will not be able to copy your friends .exe/student_license.dat files and

install in your PC.

9. Last step of installation is to save this student_license.dat file in your top level

installation directory (ex., C:\Modeltech_pe_edu_10.3c).

10. Congratulations you have successfully installed ModelSim PE student edition 10.3c.

3

ModelSim Basics

ModelSim is a fantastic digital simulator for both Verilog and VHDL hardware description

languages (HDL).

The following diagram shows the basic steps for simulation in ModelSim.

Create a working directory

Start ModelSim and create a new project

Write your VHDL code or add your code to the project

Compile your VHDL code and debugg errors

Load and run sumulations

Debugging

1. Create a directory for your simulation. For example., D:\EECS31L\ModelSim

ModelSim creates large output files, by creating a project directory it will be easier to

manage all the project files.

2. Start ModelSim, you will be able to find a shortcut on your desktop or else it will be

present in your start menu.

3. To create a new project go to File -> New -> Project

4. A new window will appear.

a. Enter the project name, ex., test

b. Change the project location to your simulation directory ex.,

D:\EECS31L\ModelSim

c. You can leave the default library name as work

d. Click OK.

4

5. In the next window you can either add an existing file or create new file. We shall create

a new file for this example.

a. Click on Create New File

b. In the next window, type a file name (for this example we shall design an OR

gate)

c. Make sure the file type is VHDL and the folder is Top Level

d. Click OK.

e. Close Add items to the Project window.

f. Note: you can also add existing VHDL files to your current project by selecting

Add existing file. You can also add multiple files by selecting this option.

6. An empty orgate.vhd should be created in your project window. Double click on the

orgate.vhd file to type the code.

5

7. Copy & paste the following code snippet.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY orgate IS

PORT ( IN1 : in STD_LOGIC; -- OR gate input

IN2 : in STD_LOGIC; -- OR gate input

OUT1 : out STD_LOGIC); -- OR gate output

END orgate;

ARCHITECTURE Behavioral of orgate IS

BEGIN

OUT1 <= IN1 or IN2; -- 2 input OR gate

END Behavioral;

6

8. Save and compile

To save the code click on the small floppy drive or use the shortcut Ctrl+s

To compile the code click on compile icon , or right click orgare.vhd -> Compile ->

Compile All.

9. If the compilation is successful a message will appear in the transcript window and the

status of the orgate.vhd will be changed.

10. A little more information about the status of the VHLD files:

a. A means that the file has not been compiled since the last edit.

b. A means that the file could not be compiled, it has an error.

Double clicking the will bring up a list of errors with line numbers

c. A means that the file has been compiled successfully.

7

11. Simulate.

After compilation, the next step is to simulate the VHDL code. To simulate the

compiled code click on simulate icon or simulate->start Simulation to bring up the

simulation dialog box.

12. Click the plus next to the work library and select your entity (in this case, its orgate).

Click OK.

13. A new window should appear and your design should be loaded and ready to simulate.

8

14. Adding signals to the waveform window.

a. Go to the signals window or the signals panel (this window will be in the middle

of the main window). This window will list all the signals in the current instance.

b. To add the signals to your wave window right click on the signals and click Add

Wave.

c. You can shift+select multiple signals and add them together to the wave

window.

15. In the wave window you can force the input signals to either 0 or 1 or you can assign

a clock.

a. To assign a clock to IN1, right click on /orgate/IN1 in you wave window and

click on clock to open a clock definition dialog box.

9

b. Please feel free to play with these parameters to get random signal.

c. For this example we will keep the default values for /orgate/IN1. Click OK

d. Next, we shall assign clock to IN2. Right click on /orgate/IN2 and click on clock

to open a clock definition dialog box. Here change the period to 200 and click

OK.

e. Now we have assigned the inputs, we need to simulate to get OUT1

f. To simulate, update the simulation time to 1us and click run

g. You should see the simulated output in the wave window. The output wave can

be verified by comparing it with the truth table on OR gate.

h. You can end simulation by clicking Simulate -> End Simulation

i. Similarly Simulation can be restarted by clicking Simulate -> Restart

10

User manual

To find out more about ModelSim please go through the user manual. The user manual is

available in Help -> PDF Documentation -> Users Manual

Also feel free to contact any TAs for more information.

You might also like

- Veilog HDL Module 3Document62 pagesVeilog HDL Module 3Mallik KglNo ratings yet

- CS2405 Computer Graphics Lab ManualDocument60 pagesCS2405 Computer Graphics Lab ManualSonia DudleyNo ratings yet

- 06-Verilog Behavioral ModelingDocument27 pages06-Verilog Behavioral ModelingSreekanth PagadapalliNo ratings yet

- Digital Logic Lab ManualDocument81 pagesDigital Logic Lab ManualArslan Majid100% (1)

- Verilog For TestbenchesDocument18 pagesVerilog For TestbenchesAhmed Fathy Moustafa100% (1)

- Verilog Lec s03Document126 pagesVerilog Lec s03Bruno SilvaNo ratings yet

- Xilinx Project Navigator HDL Lab ManualDocument72 pagesXilinx Project Navigator HDL Lab Manualshubham100% (1)

- CS 102 Lab 1Document18 pagesCS 102 Lab 1Abdulaziz Altararwah0% (1)

- Sending Temperature and Humidity Data from Arduino to InternetDocument30 pagesSending Temperature and Humidity Data from Arduino to InternetRJ RoxXNo ratings yet

- Verilog Designs: Introduction To Simulation of Using Modelsim-AlteraDocument31 pagesVerilog Designs: Introduction To Simulation of Using Modelsim-AlteraLinh PhanNo ratings yet

- Verilog HDL - Introduction to Typical Design Flow and BasicsDocument59 pagesVerilog HDL - Introduction to Typical Design Flow and BasicsBhargavi AndraNo ratings yet

- Krypton ManualDocument10 pagesKrypton ManualNaman JainNo ratings yet

- DLD Lab Manual 2014 - LatestDocument70 pagesDLD Lab Manual 2014 - LatestNabeel ZahurNo ratings yet

- To Verilog: Digital DesignDocument27 pagesTo Verilog: Digital Designbits_who_am_iNo ratings yet

- New DSD Manual Rvitm (4-7)Document72 pagesNew DSD Manual Rvitm (4-7)Spam SpamNo ratings yet

- Introductiontohdl: Laboratory No. 2Document9 pagesIntroductiontohdl: Laboratory No. 2Clint Agustin M. RoblesNo ratings yet

- Department of Electronics & Communication Engineering Lab Manual B.Tech Year: 3rd Semester: VIDocument53 pagesDepartment of Electronics & Communication Engineering Lab Manual B.Tech Year: 3rd Semester: VImacfready100% (1)

- Composition and AggregationDocument17 pagesComposition and AggregationPatel PritNo ratings yet

- DLD Lab 01 - Getting Started With Tinkercad-EditedDocument23 pagesDLD Lab 01 - Getting Started With Tinkercad-Editedsyed mottaquiNo ratings yet

- Matlab Basics Tutorial: VectorsDocument52 pagesMatlab Basics Tutorial: VectorsMohit Bathla MontyNo ratings yet

- Intro To ArduinoDocument23 pagesIntro To ArduinobelieveroftheimpossibleNo ratings yet

- M S Engineering College: HDL Lab ManualDocument78 pagesM S Engineering College: HDL Lab Manualvivek jNo ratings yet

- DipTrace TutorialDocument134 pagesDipTrace TutorialMetalloyNo ratings yet

- HDL Manual 2020 5th Sem E&CE 18ECL58Document74 pagesHDL Manual 2020 5th Sem E&CE 18ECL58vishvakiranaNo ratings yet

- Verilog HDL Lab Gate Level and Data Flow ModelsDocument42 pagesVerilog HDL Lab Gate Level and Data Flow ModelsRishabhBatraNo ratings yet

- Designing Finite State Machines (FSM) Using VerilogDocument8 pagesDesigning Finite State Machines (FSM) Using VerilogusaravanakumarNo ratings yet

- VerilogDocument44 pagesVerilogPreethi SamNo ratings yet

- Ecad & Vlsi LabDocument98 pagesEcad & Vlsi LabbitseceNo ratings yet

- HDL Verilog Programs Vtu 5th SemDocument12 pagesHDL Verilog Programs Vtu 5th SemNikhil KulkarniNo ratings yet

- DLD Lab Manual 01Document6 pagesDLD Lab Manual 01Sana gullNo ratings yet

- DLD-2014 - Practical BookDocument75 pagesDLD-2014 - Practical BookMuhammad Ishtiaq0% (1)

- Oop Lab ManualDocument56 pagesOop Lab Manualapi-247102572No ratings yet

- Combinational Logic DesignDocument217 pagesCombinational Logic DesignAnand GharuNo ratings yet

- CPP 1Document7 pagesCPP 1minaleNo ratings yet

- Hardware Design Lab CCE 355: Introduction To VHDLDocument78 pagesHardware Design Lab CCE 355: Introduction To VHDLabdullah samdi100% (1)

- Microprocessor - Lab 6 StudentDocument18 pagesMicroprocessor - Lab 6 Studenttj millarNo ratings yet

- Data Structures Lab Manual For VTU 15CS38-DSLDocument9 pagesData Structures Lab Manual For VTU 15CS38-DSLmeetnischay100% (3)

- VLSI LAB - Backend DesignDocument40 pagesVLSI LAB - Backend DesignKalidindi TejasreeNo ratings yet

- Practical: 1 Introduction To Arduino Board, Arduino IDE and CablesDocument33 pagesPractical: 1 Introduction To Arduino Board, Arduino IDE and CablesCkNo ratings yet

- VerilogDocument61 pagesVerilogAnonymous 13LTklH9myNo ratings yet

- CSE Exp-1Document3 pagesCSE Exp-1Piyas ChowdhuryNo ratings yet

- Keil Uvision 3 TutorialDocument12 pagesKeil Uvision 3 Tutorialapi-3697475100% (1)

- Cse 3200 Lab ManualDocument26 pagesCse 3200 Lab ManualTanveer Ahmed BelalNo ratings yet

- Expt 5 - Wein Bridge Oscillator (2020)Document3 pagesExpt 5 - Wein Bridge Oscillator (2020)samarthNo ratings yet

- Labview ReportDocument16 pagesLabview ReportMd. Shah Kamal SaimumNo ratings yet

- BTECH ISDF IOT Security QPDocument8 pagesBTECH ISDF IOT Security QPJince JoeNo ratings yet

- VLSI Lab Manual V Sem July16Document65 pagesVLSI Lab Manual V Sem July16Aditya RanjanNo ratings yet

- rr311901 Embedded Systems DesignDocument1 pagerr311901 Embedded Systems Designsivabharathamurthy100% (1)

- How To Use Dev-C++Document7 pagesHow To Use Dev-C++QaiserNo ratings yet

- Computer Organization Lab ManualDocument56 pagesComputer Organization Lab ManualRakesh DeverakondaNo ratings yet

- Calculate Fibonacci Numbers in Assembly LanguageDocument2 pagesCalculate Fibonacci Numbers in Assembly LanguageDilawarNo ratings yet

- Experiment 3 FinalDocument13 pagesExperiment 3 Finalhello876230% (1)

- Project ReportDocument3 pagesProject ReportzabithNo ratings yet

- Arduino Programming Part1 NotesDocument7 pagesArduino Programming Part1 Notesnortheix100% (1)

- Collect and Prepare Human Activity Sensor DataDocument7 pagesCollect and Prepare Human Activity Sensor DataagamdeepNo ratings yet

- Verilog Basic ExperimentsDocument62 pagesVerilog Basic ExperimentsGaurav Soni0% (1)

- CAD Tools for Digital Systems CourseDocument22 pagesCAD Tools for Digital Systems CourseNasir Ali100% (1)

- EEN 222 Lab No. 1: Introduction to Verilog and Xilinx ToolsDocument22 pagesEEN 222 Lab No. 1: Introduction to Verilog and Xilinx ToolsArslan MajidNo ratings yet

- Introduction To Modelsim: Installation and Simulating A Decoder InstallationDocument8 pagesIntroduction To Modelsim: Installation and Simulating A Decoder InstallationAyush ThakurNo ratings yet

- 001 Joseph Vs - BautistacxDocument2 pages001 Joseph Vs - BautistacxTelle MarieNo ratings yet

- Thesis Proposal On Human Resource ManagementDocument8 pagesThesis Proposal On Human Resource Managementsdeaqoikd100% (2)

- Introduction to Networks Visual GuideDocument1 pageIntroduction to Networks Visual GuideWorldNo ratings yet

- Case Digest in Special ProceedingsDocument42 pagesCase Digest in Special ProceedingsGuiller MagsumbolNo ratings yet

- Trinity R&P Keyboards Syllabus From 2018Document54 pagesTrinity R&P Keyboards Syllabus From 2018VickyNo ratings yet

- Successfull Weight Loss: Beginner'S Guide ToDocument12 pagesSuccessfull Weight Loss: Beginner'S Guide ToDenise V. FongNo ratings yet

- Motorizovaná Pechota RotaDocument12 pagesMotorizovaná Pechota RotaFran BejaranoNo ratings yet

- Kina Finalan CHAPTER 1-5 LIVED EXPERIENCES OF STUDENT-ATHLETESDocument124 pagesKina Finalan CHAPTER 1-5 LIVED EXPERIENCES OF STUDENT-ATHLETESDazel Dizon GumaNo ratings yet

- Álvaro García Linera A Marxist Seduced BookDocument47 pagesÁlvaro García Linera A Marxist Seduced BookTomás TorresNo ratings yet

- Erp Software Internship Report of Union GroupDocument66 pagesErp Software Internship Report of Union GroupMOHAMMAD MOHSINNo ratings yet

- Monohybrid Cross WorksheetDocument2 pagesMonohybrid Cross WorksheetLovie Alfonso0% (1)

- Focus 4 Unit 2 Grammar Quiz 2.5 A GrupaDocument1 pageFocus 4 Unit 2 Grammar Quiz 2.5 A GrupaЕвгения КоноваловаNo ratings yet

- Ruby Tuesday LawsuitDocument17 pagesRuby Tuesday LawsuitChloé MorrisonNo ratings yet

- Message and Responses From TaoshobuddhaDocument4 pagesMessage and Responses From TaoshobuddhaTaoshobuddhaNo ratings yet

- Drill Works Release NotesDocument29 pagesDrill Works Release NotesMichelle DuncanNo ratings yet

- USP 11 ArgumentArraysDocument52 pagesUSP 11 ArgumentArraysKanha NayakNo ratings yet

- A Christmas Carol AdaptationDocument9 pagesA Christmas Carol AdaptationTockington Manor SchoolNo ratings yet

- Characteristics and Elements of A Business Letter Characteristics of A Business LetterDocument3 pagesCharacteristics and Elements of A Business Letter Characteristics of A Business LetterPamela Galang100% (1)

- A Brief History of The White Nationalist MovementDocument73 pagesA Brief History of The White Nationalist MovementHugenNo ratings yet

- Bo de On Thi Hoc Ki 1 Lop 3 Mon Tieng AnhDocument66 pagesBo de On Thi Hoc Ki 1 Lop 3 Mon Tieng AnhHằng DiệuNo ratings yet

- SPACES Nepal - Green Schools Building The FutureDocument3 pagesSPACES Nepal - Green Schools Building The FutureBimal ThapaNo ratings yet

- Sky Education: Organisation of Commerce and ManagementDocument12 pagesSky Education: Organisation of Commerce and ManagementKiyaara RathoreNo ratings yet

- HM5 - ScriptDocument4 pagesHM5 - ScriptCamilleTizonNo ratings yet

- (Click Here) : Watch All Paid Porn Sites For FreeDocument16 pages(Click Here) : Watch All Paid Porn Sites For Freexboxlivecode2011No ratings yet

- Fundamentals of Financial ManagementDocument550 pagesFundamentals of Financial ManagementShivaang Maheshwari67% (3)

- Hospitality Marketing Management PDFDocument642 pagesHospitality Marketing Management PDFMuhamad Armawaddin100% (6)

- Rev Transcription Style Guide v3.3Document18 pagesRev Transcription Style Guide v3.3jhjNo ratings yet

- Marylebone Construction UpdateDocument2 pagesMarylebone Construction UpdatePedro SousaNo ratings yet

- Invoice Inv0006: Er. Mohamed Irshadh P MDocument1 pageInvoice Inv0006: Er. Mohamed Irshadh P Mmanoj100% (1)

- MEAB Enewsletter 14 IssueDocument5 pagesMEAB Enewsletter 14 Issuekristine8018No ratings yet