Professional Documents

Culture Documents

Stacked Multi-Chip Product

Uploaded by

Ricky CoxCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Stacked Multi-Chip Product

Uploaded by

Ricky CoxCopyright:

Available Formats

S75WS-N Based MCPs

Stacked Multi-Chip Product (MCP)

256 Megabit (16M x 16-bit) CMOS 1.8 Volt-only

Simultaneous Read/Write, Burst-mode Flash Memory

with 128 Mb (8M x 16-Bit) RAM Type 4 and

512 Mb (32M x 16-bit) Data Flash or 1 Gb ORNAND Flash

Data Sheet

PRELIMINARY

Notice to Readers: This document indicates states the current technical

specifications regarding the Spansion product(s) described herein. The

Preliminary status of this document indicates that a product qualification has

been completed, and that initial production has begun. Due to the phases of

the manufacturing process that require maintaining efficiency and quality, this

document may be revised by subsequent versions or modifications due to

changes in technical specifications.

Publication Number S75WS-N_02

Revision A

Amendment 2

Issue Date October 6, 2005

P r e l i m i n a r y

Notice On Data Sheet Designations

Spansion LLC issues data sheets with Advance Information or Preliminary designations to advise

readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however,

readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Spansion data sheet designations are presented here to highlight their presence and definitions.

Advance Information

The Advance Information designation indicates that Spansion LLC is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product

may discontinue. Spansion LLC therefore places the following conditions upon Advance Information content:

This document contains information on one or more products under development at Spansion LLC. The

information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed

product without notice.

Preliminary

The Preliminary designation indicates that the product development has progressed such that a

commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the

manufacturing process that occur before full production is achieved. Changes to the technical

specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Spansion places the following conditions upon Preliminary content:

This document states the current technical specifications regarding the Spansion product(s) described

herein. The Preliminary status of this document indicates that product qualification has been completed,

and that initial production has begun. Due to the phases of the manufacturing process that require

maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications.

Combination

Some data sheets will contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document will distinguish these products

and their designations wherever necessary, typically on the first page, the ordering information

page, and pages with DC Characteristics table and AC Erase and Program table (in the table

notes). The disclaimer on the first page refers the reader to the notice on this page.

Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal

changes are expected, the Preliminary designation is removed from the data sheet. Nominal

changes may include those affecting the number of ordering part numbers available, such as the

addition or deletion of a speed option, temperature range, package type, or VIO range. Changes

may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Spansion LLC applies the following conditions to documents in this category:

This document states the current technical specifications regarding the Spansion product(s) described

herein. Spansion LLC deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification

corrections, or modifications to the valid combinations offered may occur.

Questions regarding these document designations may be directed to your local AMD or Fujitsu

sales office.

ii

S75WS-N Based MCPs

S75WS-N_02_A2 October 6, 2005

S75WS-N Based MCPs

Stacked Multi-Chip Product (MCP)

256 Megabit (16M x 16-bit) CMOS 1.8 Volt-only

Simultaneous Read/Write, Burst-mode Flash Memory with

128 Mb (8M x 16-Bit) RAM Type 4 and

512 Mb (32M x 16-bit) Data Flash or 1Gb ORNAND Flash

Data Sheet

PRELIMINARY

General Description

The S75WS-N Series is a product line of stacked Multi-Chip Product (MCP) packages and consists

of the following items:

One or more S29WS-N code Flash

RAM Type 4

One or more S29WS-N data Flash, or one or more S30MS-P ORNAND Flash

The products covered by this document are listed in the table below:

Device

Code Flash

Density

RAM

Density

256 Mb

128 Mb

S75WS256NDF

S75WS256NEG

256 Mb

NOR Data Flash

Density

ORNAND Data Flash

Density

512 Mb

1024 Mb

Distinctive Characteristics

MCP Features

Power supply voltage of 1.7 V to 1.95 V

High Performance

54 MHz, 66 Mhz, 80 MHz

Packages

9 x 12 mm 84 ball FBGA

11 x 13 mm 115 ball FBGA

Operating Temperature

Wireless, 25C to +85C

Publication Number S75WS-N_02

Revision A

Amendment 2

Issue Date October 6, 2005

P r e l i m i n a r y

Contents

S75WS-N Based MCPs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . i

1

2

3

4

5

Tables

Product Selector Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.1 NOR Flash + pSRAM + ORNAND Flash MCPs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Input/Output Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

MCP Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Connection Diagrams/Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

5.1 Special Handling Instructions for FBGA Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

5.2 Connection Diagram NOR Flash & 1.8 V RAM Type 4 Based Pinout, 9 x 12 mm . . . . . . . . . . . . . . . . . . . . . . . 8

5.3 Connection Diagram ORNAND-Based Pinout, 11 x 13 mm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5.4 Physical Dimensions FEA084 Fine Pitch Ball Grid Array 9 x 12 mm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

5.5 Physical Dimensions FND115 Fine Pitch Ball Grid Array 11 x 13 mm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

MCP Revisions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 2.1

MCP Configurations and Valid Combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 2.2

ORNAND Configurations and Valid Combinations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 3.1

NOR Flash and RAM Input/Output Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 3.2

ORNAND Flash Input/Output Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figures

Figure 4.1

Figure 4.2

MCP Block Diagram 1 ......................................................................................................................... 6

ORNAND Block Diagram ...................................................................................................................... 7

S75WS-N Based MCPs

S75WS-N_02_A2 October 6, 2005

P r e l i m i n a r y

Product Selector Guide

Device

MCP Configuration

Model

Numbers

Code

Flash

RAM

(Mb)

Code

RAM

Data Storage Density Density

(Mb)

(Mb)

Flash

DYB

pSRAM

Data Flash Flash pSRAM

Power-Up

(RAM Type 4)

Density

Speed Speed

State

Supplier

(Mb)

(MHz) (MHz)

(See Note)

LK

NK

S75WS256NDF

LJ

NJ

WS256N

128

2xWS256N

256

128

512

LH

NH

54

54

66

66

80

80

Package

84 ball

FBGA

(mm)

0

1

0

1

9x12

0

1

Note: 0 (Protected), 1 (Unprotected [Default State])

1.1

NOR Flash + pSRAM + ORNAND Flash MCPs

Device

S75WS256NEG

Model

Numbers

NOR Flash

Density

ORNAND Flash

Density

pSRAM

Density

MCP Speed

UK

54 MHz

UJ

66 MHz

UH

SK

512 Mb

1024 Mb

256 Mb

80 MHz

54 MHz

SJ

66 MHz

SH

80 MHz

October 6, 2005 S75WS-N_02_A2

S75WS-N Based MCPs

Supplier

ORNAND Bus

Width

Package

x16

1.8 V

pSRAM

Type 4

11 x 13 x 1.4 mm

x8

P r e l i m i n a r y

Ordering Information

The ordering part number is formed by a valid combination of the following:

S75WS

256

BA

K 0

Packing

0

=

2

=

3

=

RAM

K

J

H

Type

Tray

7 Tape and Reel

13 Tape and Reel

Supplier; Speed Combination

= RAM Type 4, 54 MHz

= RAM Type 4, 66 MHz

= RAM Type 4, 80 MHz

Package Dimensions and Ball Count; DYB Power Up;

Flash Device Family (Data Storage)

L

= 1.4 mm, 9 x 12, 84 ball; 0, WS as Data Flash

N

= 1.4 mm, 9 x 12, 84 ball; 1, WS as Data Flash

U

= 1.4mm, 11x13, 115-ball, x16 ORNAND Data Flash

S

= 1.4mm, 11x13, 115-ball, x8 ORNAND Data Flash

Temperature Range

W

= Wireless (25C to +85C)

Package Type And Material

BA

= Very Thin Fine-Pitch Ball Grid Array (BGA),

Lead (Pb)-free Compliant Package

BF

= Very Thin Fine-Pitch Ball Grid Array (BGA),

Lead (Pb)-free Package

Data Flash Density

F

= 512 Mb

G

= 1024 Mb

RAM Density

D

= 128 Mb

E

= 256 Mb

Process Technology

N

= 110 nm, Mirror Bit Technology

Code Flash Density

256

= 256 Mb

Device Family

S75WS = Multi-chip Product (MCP)

1.8-volt Burst Mode Flash Memory, RAM, and data flash

Table 2.1

MCP Configurations and Valid Combinations

S75WS256N

Table 2.2

S75WS256N

Valid Combination

BA, BF

L, N

K, H

ORNAND Configurations and Valid Combinations

E

Valid Combination

BA, BF

U, S

K, J, H

Package Marking Note:

The BGA package marking omits the leading S75 and packing type designator from the ordering part number.

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult

your local sales office to confirm availability of specific valid combinations and to check on newly

released combinations.

S75WS-N Based MCPs

S75WS-N_02_A2 October 6, 2005

P r e l i m i n a r y

Input/Output Descriptions

Table 3.1 identifies the input and output package connections provided on the device.

Table 3.1

NOR Flash and RAM Input/Output Descriptions

Symbol

Description

Amax A0

Address Inputs

DQ15 - DQ0

Data Inputs/Outputs

OE#

Output Enable input

WE#

Write Enable input

VSS

Ground

(Common)

NC

No Connect; not connected internally.

RDY

Ready output. Indicates the status of the Burst read.

(Flash)

CLK

Clock input. In burst mode, after the initial word is output, subsequent

active edges of CLK increment the internal address counter. Should be at

VIL or VIH while in asynchronous mode.

(Common)

AVD#

Address Valid input.

Indicates to device that the valid address is present on the address inputs.

F-RST#

Hardware reset input.

F-WP#

Hardware write protect input.

At VIL, disables program and erase functions in the four outermost sectors.

Should be at VIH for all other conditions.

F-ACC

Accelerated input.

At VHH, accelerates programming; automatically places device in unlock

bypass mode. At VIL, disables all program and erase functions. Should be

at VIH for all other conditions.

R-CE#

Chip-enable input for pSRAM

F1-CE#

Chip-enable input for Code Flash.

F2-CE#

Chip-enable input for Data Flash 1.

F2-CE#

Chip-enable input for Data Flash 2.

R-MRS#

Control Register Enable.

F-VCC

Flash 1.8 Volt-only single power supply.

R-VCC

pSRAM Power Supply.

R-UB#

Upper Byte Control.

R-LB#

Lower Byte Control .

(Flash)

Asynchronous relative to

CLK for Burst Mode.

(pSRAM RAM Type 4 only)

(pSRAM)

Table 3.2 identifies the ORNAND input and output connections provided on the device.

Table 3.2

ORNAND Flash Input/Output Descriptions

Symbol

Description

N-PRE

ORNAND Power-On Read Enable. Tie to VSS on customer board if not used.

N-ALE

ORNAND Address Latch Enable

N-CLE

ORNAND Command Latch Enable

N-CE#

ORNAND Chip-enable

N-WP#

ORNAND Write-protect

N-WE#

ORNAND Write-enable

N-RE#

ORNAND Read-enable

N-RY/BY#

ORNAND Ready-Busythis is shared with NOR RDY

N-I/O0-N-I/O15

ORNAND I/O signals (I/O0-I/O7 for x8 bus width)

N-VCC

ORNAND Power supply

October 6, 2005 S75WS-N_02_A2

S75WS-N Based MCPs

P r e l i m i n a r y

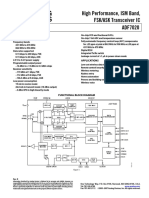

MCP Block Diagram

A0-A22

A0-A22

A23

A23

RDY

RDY

CLK

AVD#

F1-CE#

OE#

F-RST#

F-ACC

F1-WP#

F-WE#

CLK

AVD#

CE#

OE#

RESET#

ACC

WP#

WE#

DQ0-DQ15

WS256N

Flash

Memory

DQ0-DQ15

VSS

VSS

VCC

VCCQ

F-VCC

F-VCCQ

A0-A22

DQ0-DQ15

WAIT#

CLK

AVD#

CE#

OE#

R-CE#

R-LB#

R-UB#

128Mb

Memory

LB#

UB#

WE#

MRS#

R-MRS#

VSS

VCC

VCCQ

R-VCC

R-VCCQ

A0-A22

A23

DQ0-DQ15

RDY

CLK

AVD#

CE#

OE#

RESET#

ACC

WP#

WE#

F2-CE#

FD-WP#

WS256N

Flash

Memory

VSS

VCC

VCCQ

A0-A22

A23

DQ0-DQ15

RDY

F3-CE#

v

CLK

AVD#

CE#

OE#

RESET#

ACC

WP#

WE#

WS256N

Flash

Memory

VSS

VCC

VCCQ

Notes:

1.

2.

MRS is only present in RAM Type 4.

CE#f1, CE#f2, and CE#f3 are the chip enable pins for the first, second and third Flash devices, respectively.

Figure 4.1

MCP Block Diagram 1

S75WS-N Based MCPs

S75WS-N_02_A2 October 6, 2005

P r e l i m i n a r y

x16 MS01GP-based MCP

A0-A22

A0-A22

A23

A23

RDY

RDY

CLK

AVD#

F-CE#

OE#

F-RST#

F-ACC

F1-WP#

WE#

CLK

AVD#

CE#

OE#

RESET#

ACC

WP#

WE#

DQ0-DQ15

WS256N

Flash

Memory

VSS

VCC

VCCQ

DQ0-DQ15

VSS

F-VCC

A0-A22

DQ0-DQ15

WAIT#

R1-CE#

R-LB#

R-UB#

R-MRS#

CLK

AVD#

CE#

OE#

LB#

UB#

WE#

MRS#

128 Mb

RAM

Memory

VSS

VCC

VCCQ

R-VCC

A0-A22

DQ0-DQ15

WAIT#

R2-CE#

CLK

AVD#

CE#

OE#

LB#

UB#

WE#

MRS#

I/O0-I/O15

128 Mb

RAM

Memory

VSS

VCC

VCCQ

I/O0-I/O15

N-RY/BY#

RB#

N-CLE

N-CE#

N-ALE

CLE

CE#

ALE

N-RE#

N-WP#

N-WE#

RE#

WP#

WE#

MS01GP

x16 ORNAND

Memory

VSS

PRE

N-VSS

N-PRE

VCC

N-VCC

Figure 4.2 ORNAND Block Diagram

October 6, 2005 S75WS-N_02_A2

S75WS-N Based MCPs

P r e l i m i n a r y

Connection Diagrams/Physical Dimensions

This section contains the I/O designations and package specifications for the S75WS.

5.1

Special Handling Instructions for FBGA Package

Special handling is required for Flash Memory products in FBGA packages.

Flash memory devices in FBGA packages may be damaged if exposed to ultrasonic cleaning methods. The package and/or data integrity may be compromised if the package body is exposed to

temperatures above 150C for prolonged periods of time.

5.2

Connection Diagram NOR Flash & 1.8 V RAM Type 4 Based Pinout, 9 x 12 mm

Legend:

A1

A10

DNU

DNU

B2

B3

B4

B5

B6

B7

B8

B9

ADV#

VSS

CLK

RFU

F-VCC

RFU

RFU

RFU

C2

C3

C4

C5

C6

C7

C8

C9

F1-WP#

A7

R-LB#

F-ACC

WE#

A8

A11

F2-CE#

D2

D3

D4

D5

D6

D7

D8

D9

A3

A6

R-UB#

F-RST#

RFU

A19

A12

A15

Flash 2

Data Only

E2

E3

E4

E5

E6

E7

E8

E9

A2

A5

A18

RDY

A20

A9

A13

A21

F2

F3

F4

F5

F6

F7

F8

F9

A1

A4

A17

RFU

A23

A10

A14

A22

G2

G3

G4

G5

G6

G7

G8

G9

Flash 1

Code Only

A0

VSS

DQ1

RFU

RFU

DQ6

RFU

A16

H2

H3

H4

H5

H6

H7

H8

H9

RAM Only

OE#

DQ9

DQ3

DQ4

DQ13

DQ15

J2

J3

J4

J5

J6

J7

J8

J9

All Shared

R-CE1#

DQ0

DQ10

F-VCC

R-VCC

DQ12

DQ7

VSS

K2

K3

K4

K5

K6

K7

K8

K9

All Flash

Shared Only

RFU

DQ8

DQ2

DQ11

RFU

DQ5

DQ14

L2

L3

L4

L5

L6

L7

L8

L9

RFU

RFU

VSS

F-VCC

F3-CE#

RFU

F-VCCQ

DNU

F1-CE#

X

RFU

(Reserved for

Future Use)

X

Data Flash

Shared Only

X

Flash 3

Data Only

R-MRS#

FD-WP#

X

Do Not Use

M1

M10

DNU

DNU

S75WS-N Based MCPs

S75WS-N_02_A2 October 6, 2005

P r e l i m i n a r y

5.3

Connection Diagram ORNAND-Based Pinout, 11 x 13 mm

Legend

A1

A2

A9

A10

DNU

DNU

DNU

DNU

B1

B2

B9

B10

DNU

DNU

DNU

DNU

Reserved for

Future Use

Do Not Use

C2

C3

C4

C5

C6

C7

C8

C9

C10

AVD#

VSS

CLK

RFU

IO15

IO14

IO13

IO12

DNU

D2

D3

D4

D5

D6

D7

D8

D9

D10

A7

R-LB#

F-ACC

WE#

A8

A11

IO11

IO10

E2

E3

E4

E5

E6

E7

E8

E9

E10

A3

A6

R-UB#

F-RST#

R2-CE#

A19

A12

A15

IO9

F2

F3

F4

F5

F6

F7

F8

F9

F10

N-CE#

A2

A5

A18

RDY

A20

A9

A13

A21

IO8

G1

G2

G3

G4

G5

G6

G7

G8

G9

G10

N-VCC

A1

A4

A17

RFU

A23

A10

A14

A22

N-VCC

H1

H2

H3

H4

H5

H6

H7

H8

H9

H10

N-VSS

A0

VSS

DQ1

RFU

RFU

DQ6

RFU

A16

N-VSS

J1

J2

J3

J4

J5

J6

J7

J8

J9

J10

N-CLE#

F1-CE#

OE#

DQ9

DQ3

DQ4

DQ13

DQ15

R-MRS

IO7

K1

K2

K3

K4

K5

K6

K7

K8

K9

K10

N-ALE#

R1-CE#

DQ0

DQ10

F-VCC

R-VCC

DQ12

DQ7

VSS

IO6

L1

L2

L3

L4

L5

L6

L7

L8

L9

L10

N-WE#

N-WP#

DQ8

DQ2

DQ11

RFU

DQ5

DQ14

IO4

IO5

M1

M2

M3

M4

M5

M6

M7

M8

M9

M10

DNU

RFU

RFU

VSS

F-VCC

IO0

IO1

IO2

IO3

PRE

N1

N2

N9

N10

DNU

DNU

DNU

DNU

P1

P2

P9

DNU

DNU

DNU

D1

N-RY/BY# F-WP#

E1

N-RE#

F1

NOR Flash Only

NAND Flash Only

PSRAM 1 Only

PSRAM 2 Only

PSRAM Shared Only

NOR Flash &

PSRAM Shared

P10

DNU

Note: Bus 1: NOR Flash + pSRAM, Bus 2: ORNAND Flash

October 6, 2005 S75WS-N_02_A2

S75WS-N Based MCPs

P r e l i m i n a r y

5.4

Physical Dimensions FEA084 Fine Pitch Ball Grid Array 9 x 12 mm

D1

eD

0.15 C

(2X)

10

9

SE

7

6

E1

5

4

eE

3

2

1

M L K J

INDEX MARK

PIN A1

CORNER

10

TOP VIEW

H G F

E D C

B A

PIN A1

CORNER

SD

0.15 C

(2X)

BOTTOM VIEW

0.20 C

A A2

A1

0.08 C

SIDE VIEW

84X

0.15

0.08

M C A B

M C

NOTES:

PACKAGE

FEA 084

JEDEC

N/A

DxE

12.00 mm x 9.00 mm

PACKAGE

SYMBOL

MIN

NOM

MAX

---

---

1.40

A1

0.10

---

---

A2

1.11

---

1.26

12.00 BSC.

NOTE

PROFILE

9.00 BSC.

BODY SIZE

MATRIX FOOTPRINT

E1

7.20 BSC.

MATRIX FOOTPRINT

MD

12

MATRIX SIZE D DIRECTION

ME

10

MATRIX SIZE E DIRECTION

84

0.40

ALL DIMENSIONS ARE IN MILLIMETERS.

3.

BALL POSITION DESIGNATION PER JESD 95-1, SPP-010.

4.

e REPRESENTS THE SOLDER BALL GRID PITCH.

5.

SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D"

DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE

"E" DIRECTION.

BODY SIZE

8.80 BSC.

0.35

2.

BODY THICKNESS

DIMENSIONING AND TOLERANCING METHODS PER

ASME Y14.5M-1994.

BALL HEIGHT

D1

1.

n IS THE NUMBER OF POPULTED SOLDER BALL POSITIONS

FOR MATRIX SIZE MD X ME.

6

DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL

DIAMETER IN A PLANE PARALLEL TO DATUM C.

SD AND SE ARE MEASURED WITH RESPECT TO DATUMS A

AND B AND DEFINE THE POSITION OF THE CENTER SOLDER

BALL IN THE OUTER ROW.

BALL COUNT

0.45

eE

0.80 BSC.

BALL PITCH

eD

0.80 BSC

BALL PITCH

SD / SE

0.40 BSC.

SOLDER BALL PLACEMENT

A2,A3,A4,A5,A6,A7,A8,A9

B1,B10,C1,C10,D1,D10

E1,E10,F1,F10,G1,G10

H1,H10,J1,J10,K1,K10,L1,L10

M2,M3,M4,M5,M6,M7,M8,M9

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE

OUTER ROW SD OR SE = 0.000.

BALL DIAMETER

DEPOPULATED SOLDER BALLS

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE

OUTER ROW, SD OR SE = e/2

8.

"+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED

BALLS.

9.

N/A

10 A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK

MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

3423 \ 16-038.21a

10

S75WS-N Based MCPs

S75WS-N_02_A2 October 6, 2005

P r e l i m i n a r y

5.5

Physical Dimensions FND115 Fine Pitch Ball Grid Array 11 x 13 mm

A

D1

eD

0.15 C

(2X)

10

9

8

7

6

E

eE

SE

E1

5

4

3

2

1

PIN A1

CORNER

N M

INDEX MARK

H G F

D C B

PIN A1

CORNER

SD

0.15 C

TOP VIEW

L K

(2X)

BOTTOM VIEW

0.20 C

A A2

A1

SIDE VIEW

0.08 C

115X

0.15

0.08

M C A B

M C

NOTES:

PACKAGE

FND 115

JEDEC

N/A

DxE

13.00 mm x 11.00 mm

PACKAGE

SYMBOL

MIN

NOM

MAX

---

---

1.40

A1

0.17

---

---

A2

0.98

---

1.15

13.00 BSC.

PROFILE

BALL HEIGHT

11.00 BSC.

BODY SIZE

MATRIX FOOTPRINT

E1

7.20 BSC.

MD

14

MATRIX SIZE D DIRECTION

ME

10

MATRIX SIZE E DIRECTION

MATRIX FOOTPRINT

115

0.40

BALL POSITION DESIGNATION PER JEP95, SECTION

4.3, SPP-010.

4.

e REPRESENTS THE SOLDER BALL GRID PITCH.

5.

SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D"

DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E"

DIRECTION.

n IS THE NUMBER OF POPULTED SOLDER BALL

POSITIONS FOR MATRIX SIZE MD X ME.

DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL

DIAMETER IN A PLANE PARALLEL TO DATUM C.

SD AND SE ARE MEASURED WITH RESPECT TO

DATUMS A AND B AND DEFINE THE POSITION OF THE

CENTER SOLDER BALL IN THE OUTER ROW.

BALL COUNT

0.45

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS

IN THE OUTER ROW SD OR SE = 0.000.

BALL DIAMETER

eE

0.80 BSC.

BALL PITCH

eD

0.80 BSC

BALL PITCH

0.40 BSC.

SOLDER BALL PLACEMENT

SD SE

ALL DIMENSIONS ARE IN MILLIMETERS.

3.

BODY SIZE

10.40 BSC.

0.35

2.

BODY THICKNESS

DIMENSIONING AND TOLERANCING METHODS PER

ASME Y14.5M-1994.

NOTE

D1

1.

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS

IN THE OUTER ROW, SD OR SE = e/2

8.

"+" INDICATES THE THEORETICAL CENTER OF

DEPOPULATED BALLS.

9.

A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER

OR INK MARK, METALLIZED MARK INDENTATION OR

OTHER MEANS.

A3-A8,B3-B8,C1,N3-N8,P3-P8 DEPOPULATED SOLDER BALLS

3524 \ 16-038.19 \ 10.5.05

October 6, 2005 S75WS-N_02_A2

S75WS-N Based MCPs

11

A d v a n c e

I n f o r m a t i o n

MCP Revisions

Revision A0 (February 17, 2005)

Initial Release

Revision A1 (September 8, 2005)

Global

Removed references to the S29RS-N data sheet

Product Selector Guide

Updated table and added 80 MHz options

Ordering Information

Updated table with new options

MCP Configurations and Valid Combinations

Updated table to reflect new options

Input/Output Descriptions

Updated table and changed some pin names

MCP Block Diagram

Updated the illustration

Connection Diagram

Updated the pinout diagram

Physical Dimensions

Added the FEA084 package diagram

Look-Ahead Connection Diagram

Removed from data sheet

S29WS-N Flash Module

Updated to the latest revision

Revision A2 (October 6, 2005)

Global

Added ORNAND Flash information

Product Selector Guide

Added ORNAND options

Ordering Information

Updated table with new options

MCP Block Diagram

Added the ORNAND illustration

Connection Diagram

Added the pinout diagram for the ORNAND device

Physical Dimensions

Added the FND115 package diagram

12

S75WS-N Based MCPs

S75WS_02_A2 October 6, 2005

A d v a n c e

I n f o r m a t i o n

S29WS-N Flash Module

Removed from MCP. Available as a standalone document.

1.8 V Type 4 pSRAM Module

Removed from MCP. Available as a standalone document.

Colophon

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary

industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for any use that

includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal

injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control,

medical life support system, missile launch control in weapon system), or (2) for any use where chance of failure is intolerable (i.e., submersible repeater and

artificial satellite). Please note that Spansion LLC will not be liable to you and/or any third party for any claims or damages arising in connection with abovementioned uses of the products. Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such

failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels

and other abnormal operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the US Export Administration Regulations or the applicable laws of any other country, the

prior authorization by the respective government entity will be required for export of those products.

Trademarks and Notice

The contents of this document are subject to change without notice. This document may contain information on a Spansion LLC product under development

by Spansion LLC. Spansion LLC reserves the right to change or discontinue work on any product without notice. The information in this document is provided

as is without warranty or guarantee of any kind as to its accuracy, completeness, operability, fitness for particular purpose, merchantability, non-infringement

of third-party rights, or any other warranty, express, implied, or statutory. Spansion LLC assumes no liability for any damages of any kind arising out of the

use of the information in this document.

Copyright 2005 Spansion LLC. All rights reserved. Spansion, the Spansion logo, and MirrorBit are trademarks of Spansion LLC. Other company and product

names used in this publication are for identification purposes only and may be trademarks of their respective companies.

October 6, 2005 S75WS_02_A2

S75WS-N Based MCPs

13

You might also like

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Mini TOP Views LEDsDocument11 pagesMini TOP Views LEDsRicky CoxNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- ACCU-Torq® MotorsDocument2 pagesACCU-Torq® MotorsRicky CoxNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- AN1269 Application Note MPC555Document15 pagesAN1269 Application Note MPC555Ricky CoxNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- TIPC400B DatasheetDocument1 pageTIPC400B DatasheetRicky CoxNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- JEFT Phillips J212Document7 pagesJEFT Phillips J212Ricky CoxNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- SFP Bidirectional Single Fiber TransceiversDocument4 pagesSFP Bidirectional Single Fiber TransceiversRicky CoxNo ratings yet

- SDK Redrat Com APIDocument17 pagesSDK Redrat Com APIRicky CoxNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- J212 PDFDocument7 pagesJ212 PDFRicky CoxNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Temt600 Datasheet PDFDocument5 pagesTemt600 Datasheet PDFRicky CoxNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- PowerMesh IGBT 120HDDocument13 pagesPowerMesh IGBT 120HDRicky CoxNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- GN2470Document5 pagesGN2470Alejandro BandaNo ratings yet

- High Efficiency SMD Power InductorsDocument1 pageHigh Efficiency SMD Power InductorsRicky CoxNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Cisco Icon LibraryDocument6 pagesCisco Icon LibraryYunow MendozaNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- DAC0808 DatasheetDocument12 pagesDAC0808 DatasheetRicky CoxNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Xfs Filesystem BackgroundDocument16 pagesXfs Filesystem BackgroundRicky CoxNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Pic Timer0 Tutorial Part1Document18 pagesPic Timer0 Tutorial Part1ivan10mNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Led Backlight Driver Panel Selection GuideDocument2 pagesLed Backlight Driver Panel Selection GuideRicky CoxNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- VV6404 Datasheet PDFDocument54 pagesVV6404 Datasheet PDFRicky CoxNo ratings yet

- ThePomodoroTechnique v1-3 PDFDocument45 pagesThePomodoroTechnique v1-3 PDFRebecca SalmanNo ratings yet

- Differential Translator/Repeater: Features DescriptionDocument25 pagesDifferential Translator/Repeater: Features DescriptionRicky CoxNo ratings yet

- STV0672 Datasheet PDFDocument2 pagesSTV0672 Datasheet PDFRicky CoxNo ratings yet

- Lvds Cable DataDocument20 pagesLvds Cable DataAnura MaddumageNo ratings yet

- Duracell 9V Battery Performance DataDocument2 pagesDuracell 9V Battery Performance DataRicky CoxNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Raster Graphics Drawing LinesDocument25 pagesRaster Graphics Drawing LinesVishal FalakeNo ratings yet

- AsRock K7S41GX ManualDocument31 pagesAsRock K7S41GX ManualjamesNo ratings yet

- Product Overview: LA6584M: BTL Driver Single-Phase Full-Wave Fan Motor DriverDocument1 pageProduct Overview: LA6584M: BTL Driver Single-Phase Full-Wave Fan Motor DriverRicky CoxNo ratings yet

- Atmel LED Driver-MSLB9082 LED Backlight Driver Module: DatasheetDocument20 pagesAtmel LED Driver-MSLB9082 LED Backlight Driver Module: DatasheetRicky CoxNo ratings yet

- 1.5 Amp Positive Voltage Regulator: EZ1086BC, EZ1086C & EZ1086IDocument6 pages1.5 Amp Positive Voltage Regulator: EZ1086BC, EZ1086C & EZ1086IRicky CoxNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Chapter2 Payroll SystemDocument5 pagesChapter2 Payroll SystemJohn David Bildan84% (25)

- Myc - Ya157c - Pin List20191001Document13 pagesMyc - Ya157c - Pin List20191001lostin ANo ratings yet

- FM1120 User Manual v5.2 - 47.07.XX - 47.08.XXDocument93 pagesFM1120 User Manual v5.2 - 47.07.XX - 47.08.XXJennsett SastreNo ratings yet

- Vivo Gallery Log ErrorsDocument6 pagesVivo Gallery Log ErrorsHaniagaNo ratings yet

- Dip Switch Settings ReadDocument3 pagesDip Switch Settings ReadRuzhen Dimitrov100% (1)

- Urddo Commands Manual (UBy-17003787)Document198 pagesUrddo Commands Manual (UBy-17003787)kingtakNo ratings yet

- Calibration of Tr-Rec ESPDocument17 pagesCalibration of Tr-Rec ESPNuris ApriyantoNo ratings yet

- Manual Reference 2 (1) .9Document624 pagesManual Reference 2 (1) .9Aly MaqfurNo ratings yet

- Podar International School Chinchwad STD Xi - (I Unit Test) Subject: Computer Science Date: 8-9-2020 Marks: 40Document3 pagesPodar International School Chinchwad STD Xi - (I Unit Test) Subject: Computer Science Date: 8-9-2020 Marks: 40Shriniwas KulkarniNo ratings yet

- Textual Learning Material - Module 3Document36 pagesTextual Learning Material - Module 3admondalNo ratings yet

- Kyocera M8124cidn M8130cidn BrochureDocument4 pagesKyocera M8124cidn M8130cidn BrochureNBS Marketing100% (1)

- Seminar Report On Programmable Logic Controller (PLC)Document37 pagesSeminar Report On Programmable Logic Controller (PLC)Manish Kumar sharma92% (13)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- LTE DRX and Signaling Control ISSUE 1.00Document65 pagesLTE DRX and Signaling Control ISSUE 1.00trio7884No ratings yet

- DP610SACB ManualDocument24 pagesDP610SACB ManualChase SmytheNo ratings yet

- Cpu RtaDocument212 pagesCpu RtaRamesh GrandheNo ratings yet

- Yet Another Haskell TutorialDocument192 pagesYet Another Haskell TutorialfembemNo ratings yet

- 3900 & 5900 Series Base Station Technical Description (V100R017C00 - Draft A) (PDF) - ENDocument36 pages3900 & 5900 Series Base Station Technical Description (V100R017C00 - Draft A) (PDF) - ENlaabidi salemNo ratings yet

- RESTful API DesignDocument25 pagesRESTful API DesignSikasaro KembarenNo ratings yet

- XBOX 360 Back up and Burn ToolKit GuideDocument103 pagesXBOX 360 Back up and Burn ToolKit GuideLeeann TaverasNo ratings yet

- Lecture 2 Block Diagram Representation of Control SystemsDocument57 pagesLecture 2 Block Diagram Representation of Control SystemsAmeer FauwazNo ratings yet

- Task 1Document3 pagesTask 1Dhiviyansh Punamiya OT3 - 433No ratings yet

- ESX Server Cluster & Resource Pool GuideDocument4 pagesESX Server Cluster & Resource Pool GuideMaroozi SamadNo ratings yet

- 2 Obstacle Avoiding Robot PDFDocument7 pages2 Obstacle Avoiding Robot PDFRaj AryanNo ratings yet

- chapter 10 dbmsDocument9 pageschapter 10 dbmsSaloni VaniNo ratings yet

- 5eb9e9cd6a6768fe5b9515e262eda2a2Document5 pages5eb9e9cd6a6768fe5b9515e262eda2a2Arturo ReyNo ratings yet

- Presented By: Ankita Khuteta 090187Document31 pagesPresented By: Ankita Khuteta 090187Ankita KhutetaNo ratings yet

- Unit 4 ADocument10 pagesUnit 4 AChetan p ShirahattiNo ratings yet

- High Performance, ISM Band, FSK/ASK Transceiver IC ADF7020: FeaturesDocument48 pagesHigh Performance, ISM Band, FSK/ASK Transceiver IC ADF7020: FeaturesDNo ratings yet

- Open Source GIS, DATAMINING and Statistics: Dr. V.V. Venkata RamanaDocument197 pagesOpen Source GIS, DATAMINING and Statistics: Dr. V.V. Venkata RamanaAmaranatha Reddy PNo ratings yet

- Solo Ibs EngDocument4 pagesSolo Ibs Engb.ljubisaNo ratings yet

- Chip War: The Quest to Dominate the World's Most Critical TechnologyFrom EverandChip War: The Quest to Dominate the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (227)

- Chip War: The Fight for the World's Most Critical TechnologyFrom EverandChip War: The Fight for the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (82)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002From EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Rating: 5 out of 5 stars5/5 (1)

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)