Professional Documents

Culture Documents

Memoria Virtual

Uploaded by

Joao TlvCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Memoria Virtual

Uploaded by

Joao TlvCopyright:

Available Formats

1

TEORIA DE LOS SISTEMAS OPERATIVOS

ORGANIZACIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

INTRODUCCIN.

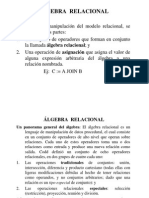

La evolucin de la organizacin del almacenamiento, se puede representar de la manera que se

expresa en el cuadro que figura a continuacin:

Sistemas

Monoprogramados

Sistemas Multiprogramados (varios usuarios)

Almacenamiento Real

Un solo Usuario

Memoria Contigua

Particiones

Fijas

Variables

Almacenamiento Virtual

Memoria no Contigua

Combinacin

Segmentacin Paginacin Segmentacin

y Paginacin

El trmino memoria virtual suele asociarse, con la capacidad que tienen algunos sistemas, para

acceder a direcciones, situadas en un espacio de almacenamiento virtual, mucho mayor, que el

disponible en el almacenamiento real de un sistema informtico determinado.

El concepto de memoria virtual no es un concepto nuevo, ya que aparece en 1.960 en un sistema

informtico denominado ATLAS, diseado y construido en la Universidad de Manchester; pero las

tecnologas existentes en aquel tiempo, no proporcionaban la ayuda necesaria para su implantacin, sin

embargo, actualmente con la ayuda de esas tecnologas, se ha generalizado el empleo de la memoria

virtual y la mayor parte de los ordenadores actuales, ya pueden gestionar el almacenamiento virtual.

Los mtodos ms comunes para gestionar la memoria de los sistemas, que permiten la existencia

de un almacenamiento virtual, son la paginacin y la segmentacin y en algunos sistemas, se puede

utilizar una combinacin de los dos mtodos.

En los sistemas de almacenamiento real, para que un proceso se pudiera ejecutar, era necesario

que el proceso completo, estuviese cargado en el almacenamiento real, sin embargo, los sistemas de

memoria virtual, se caracterizan muy especialmente, porque las direcciones utilizadas por los programas

en ejecucin, no necesitan estar todas ellas en el almacenamiento real.

La clave del concepto de memoria virtual, consiste en la diferenciacin que es preciso realizar,

entre las direcciones a las que hace referencia un programa en ejecucin y las direcciones disponibles en

el almacenamiento real.

Las direcciones a las que hace referencia un programa en ejecucin, se denominan direcciones

lgicas o virtuales y las direcciones disponibles en el almacenamiento real, se denominan se denominan

direcciones fsicas o reales.

El intervalo de direcciones lgicas o virtuales, a las que hace referencia un programa en

ejecucin, constituyen espacio de direcciones virtuales (V) y el intervalo de direcciones fsicas o reales,

disponibles en el almacenamiento real, constituyen el espacio de direcciones reales (R).

En los sistemas de almacenamiento virtual ya implantados, lo normal es que (V) > (R), aunque se

han construido algunos sistemas en los que (V) < (R).

Lgicamente, aunque los procesos solamente hacen referencia a direcciones virtuales, estas

deben ejecutarse en el almacenamiento real, por lo tanto, es preciso establecer la correspondencia entre

las direcciones virtuales y las direcciones reales durante la ejecucin del proceso.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Adems, esto debe hacerse con rapidez, pues de lo contrario, el rendimiento del sistema se

degradara a niveles inaceptables, eliminando as, las ganancias logradas, por el empleo del concepto de

almacenamiento virtual.

Los mecanismos de traduccin dinmica de direcciones, DAT (Dynamic Address Translation),

convierten las direcciones virtuales en direcciones reales, mientras se ejecuta un proceso.

Todos estos sistemas tienen la propiedad, de que las direcciones contiguas en el espacio de

direcciones virtuales de un proceso, no son necesariamente contiguas en el almacenamiento real, por lo

tanto, el usuario queda liberado de la preocupacin por la posicin de los procedimientos y los datos en

el almacenamiento real.

ORGANIZACIN DEL ALMACENAMIENTO DE VARIOS NIVELES.

Si se va a permitir, que el espacio de direcciones virtuales del usuario, sea ms grande que el

espacio de direcciones reales y adems se va a multiprogramar el sistema, permitiendo que varios

usuarios compartan el recurso de almacenamiento real, ser preciso proporcionar un almacenamiento

auxiliar, que toma el nombre de memoria virtual, para mantener los programas y los datos, que no caben

en el almacenamiento real y esto se consigue con un esquema de almacenamiento a dos niveles:

El primer nivel es el almacenamiento real, en el que se ejecutan los procesos y en el que

deben encontrarse, las instrucciones y los datos del proceso, que esta ejecutando en cada

momento.

El segundo nivel, se encuentra en la memoria virtual, de un tamao mucho mayor, capaz de

almacenar los datos y los programas, que no se pueden mantener en el almacenamiento real.

Como el almacenamiento real es compartido por muchos procesos y cada proceso puede tener

un espacio de direcciones virtuales, mucho ms grande que el almacenamiento real, en un momento

dado, solo ser posible mantener una pequea parte de los programas y los datos de un proceso, en el

almacenamiento real

PROCESADOR

MEMORIA VIRTUAL

DAT

MEMORIA

SECUNDARIA

MEMORIA REAL

CORRESPONDENCIA DE BLOQUES.

Los mecanismos de traduccin dinmica de direcciones, deben mantener las estructuras de datos

necesarias, para efectuar la traduccin de direcciones virtuales en direcciones reales, de manera que se

muestren las localidades de la memoria virtual, que estn en el almacenamiento real en un momento

determinado y el lugar donde se encuentran.

Si la correspondencia entre ambos espacios de direcciones, se estableciera por palabras o bytes,

la informacin de correspondencias, requerira tanto espacio de almacenamiento real, como el que

necesitaran los propios procesos o quizs ms, por lo tanto es necesario, agrupar la informacin en

bloques, para reducir la cantidad de informacin de correspondencias y adems se pueda obtener el

beneficio deseado, con la implantacin del concepto de memoria virtual.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

TEORIA DE LOS SISTEMAS OPERATIVOS

El mtodo a seguir consiste, en que el sistema tiene que agrupar en bloques de informacin y

registrar en una estructura de datos determinada, el lugar en donde se han situado los diversos

bloques de memoria virtual, por lo tanto, cuanto mayor sea el tamao del bloque, menor ser la

fraccin del almacenamiento real dedicada a guardar la informacin de correspondencias.

La decisin de hacer bloques ms grandes reduce el espacio necesario, para guardar las

estructuras de datos, que utiliza el mecanismo de correspondencias, sin embargo, los bloques grandes

tardan ms en ser transferidos, de la memoria virtual a la memoria real y adems consumen ms espacio

en la memoria real, limitando el nmero de procesos que pueden compartir la memoria real.

Tambin ser preciso decidir si los bloques deben ser del mismo o de distinto tamao. S los

bloques son del mismo tamao, se llaman pginas y la organizacin de la memoria virtual utiliza el

esquema de paginacin. S los bloques pueden ser de tamaos diferentes, se llaman segmentos y la

organizacin de la memoria virtual utiliza el esquema de segmentacin.

Tal y como se ha expresado anteriormente, algunos sistemas, establecen una combinacin de

ambas tcnicas, utilizando segmentos, que son entidades de tamao variable, divididos en pginas de

tamao fijo.

Las direcciones de un sistema de correspondencia de bloques de informacin, son

bidimensionales y para referirse a un elemento de informacin cualquiera, el programa especifica el

bloque de informacin, en el que se encuentra el elemento y su desplazamiento a partir del inicio del

bloque, por lo tanto, una direccin virtual (V), se denota con un par ordenado (b,d), donde b es el

nmero del bloque y d es el desplazamiento dentro del bloque.

La traduccin de una direccin virtual V = (b,d) a una direccin de almacenamiento real R, se

efecta de la forma que expresa la siguiente figura:

REGISTRO ORIGEN

DE LA TABLA

DE BLOQUES

DIRECCIN VIRTUAL

BLOQUE

DESPLAZAMIENTO

b

b

a+b

TABLA BLOQUES

d

b

LONG.

BASE

Base

DIRECCIN REAL

BASE + DESP.

Cada proceso tiene su propia tabla de correspondencias de bloques y la tabla contiene una

entrada por cada bloque del proceso. Las entradas siguen un orden secuencial desde 0 a n y en cada

entrada figuran fundamentalmente, dos informaciones: la direccin base donde comienza el bloque y su

longitud.

Realmente, todo lo que se ha expresado anteriormente, es valido tanto para bloques de tamao

fijo o variable, por lo tanto, a continuacin se tratar de especificar las diferencias existentes entre un

sistema u otro.

Si los bloques son de tamao fijo e iguales unos a otros, estos toman el nombre de pginas y se

estar estableciendo un sistema de paginacin por el contrario, si los bloques son de tamao variable,

estos toman el nombre de segmentos y se estar estableciendo un sistema de segmentacin.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Como se ha dicho anteriormente, en algunos sistemas se realiza una combinacin de los dos

mtodos, definiendo los bloques de tamao variable, es decir segmentos, que posteriormente se dividen

en partes fijas e iguales, es decir pginas. En estos sistemas se deber establecer la condicin, de que el

tamao de los segmentos debe ser mltiplo del tamao de la pgina.

PAGINACIN.

Tal y como se ha expresado anteriormente, una direccin virtual en un sistema de paginacin es

un par ordenado (p,d), en el cual p es el numero de pgina del almacenamiento virtual, en el que reside

el elemento al que se hace referencia y d es el desplazamiento dentro de la pgina.

Un proceso puede ejecutarse, si su pgina activa se encuentra en el almacenamiento real, por lo

tanto, las pginas situadas en la memoria virtual correspondientes al proceso, tienen que transferirse a la

memoria real, colocndose en bloques que se denominan marcos de pgina, que tienen el mismo tamao

que las pginas entrantes.

Los marcos comienzan en direcciones del almacenamiento real, que son mltiplos enteros del

tamao fijo de la pgina y una pgina entrante puede colocarse en cualquier marco de pgina disponible.

Un proceso en ejecucin hace referencia a una direccin del almacenamiento virtual V = (p,d) y

la traduccin dinmica de direcciones en la paginacin se realiza de la siguiente forma:

REGISTRO ORIGEN

DE LA TABLA

DE PGINAS

DIRECCIN VIRTUAL (V)

N. PGINA DESPLAZAMIENTO

TABLA PGINAS

a+p

d

DIRECCIN REAL (R)

p* Tp

R = p* Tp + d

El mecanismo de traduccin de direcciones, busca la pgina p en la tabla de correspondencia de

pginas y en cada entrada de la tabla de pginas debe existir un bit de residencia, que indique si la pgina

est en el almacenamiento real (r = 1), en cuyo caso p' indicar el nmero de marco de pgina en que

se encuentra la pgina buscada o bien indicar que la pgina no est en el almacenamiento real (r = 0),

en cuyo caso s indica la direccin de la memoria virtual en que se encuentra la pgina buscada.

BIT DE

RESIDENCIA

DIR DE MEM. VIRTUAL

SI LA PGINA NO ESTA

EN EL ALM. REAL

BITS DE

PROTECCIN

R W E A B

N. DEL MARCO DE PGINA

SI LA PGINA EST EN E L

ALM. REAL

r = 0 La pgina no est en el almacenamiento real.

r = 1 La pgina si est en el almacenamiento real.

Si la pgina no se encuentra en el almacenamiento principal, se produce una interrupcin, por

fallo de pgina, lo cual hace que el sistema operativo asuma el control y cargue la pgina desde la

direccin v de la memoria virtual al almacenamiento principal.

Hay que destacar, que p' no es una direccin real en el almacenamiento principal, p' es el nmero

del marco correspondiente a la pgina p en el almacenamiento principal, por lo tanto, la direccin real

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

TEORIA DE LOS SISTEMAS OPERATIVOS

debe ser el producto de p' por el tamao fijo de la pgina ms el desplazamiento, suponiendo que los

marcos de pgina, estn numerados consecutivamente, a partir de cero.

Es preciso recordar, que el tamao de la pgina al igual que el tamao del marco, esta definido

por el hardware y generalmente es una potencia de 2, que varia segn la arquitectura de la maquina. La

seleccin de una potencia de 2 como tamao de la pgina, facilita la traduccin de una direccin virtual

a un numero de pgina y un desplazamiento en la pgina.

Si el tamao de pgina es 2 n unidades de direccionamiento, entonces, los n bits de orden

inferior de la direccin virtual, representan el desplazamiento en la pgina y los bits restantes de orden

superior, indican el numero de pgina.

Como se ha indicado anteriormente, no todas las pginas se encuentran en la memoria real en un

instante determinado, por lo tanto, la tabla de pginas debe indicar si la pgina a la que se hace

referencia, se encuentra el almacenamiento principal, o por el contrario si no es as, donde se encuentra

en la memoria virtual.

Cada sistema operativo, tiene sus propios mtodos para almacenar las tablas de pginas, la

mayora de ellos asigna una tabla de pginas para cada proceso y en el bloque de control de proceso, se

almacena la direccin de la tabla de pginas.

Para conseguir que la traduccin de direcciones se efectu de la forma ms rpida posible,

existen varias tcnicas para establecer la correspondencia entre una direccin virtual y una direccin

real. A continuacin analizaremos estas posibles tcnicas:

Correspondencia directa.

Correspondencia asociativa.

Correspondencia combinada Asociativa/Directa.

TRADUCCIN DE DIRECCIONES POR CORRESPONDENCIA DIRECTA.

Un proceso en ejecucin hace referencia a una direccin virtual V = (p,d). Antes de que el

proceso comience su ejecucin, el sistema carga en el almacenamiento principal la tabla de

correspondencia de pginas, segn el esquema que figura a continuacin:

REGISTRO ORIGEN

DE LA TABLA

DE PGINAS

DIRECCIN VIRTUAL (V)

N. PGINA

DESPLAZAMIENTO

TABLA PGINAS

a

DIRECCIN REAL (R)

R = p* Tp + d

En la direccin de la tabla de correspondencia de pginas, se tomar como ndice el nmero de

pgina p, para determinar el elemento de la tabla de pginas, es decir, la entrada de la pgina p, que

indica el marco de pgina p' correspondiente a la pgina virtual p, por lo tanto, p' multiplicado por el

tamao de la pgina, se concatenar con el desplazamiento d, para formar la direccin real R = p*Tp + d

.

Este es un ejemplo de correspondencia directa, ya que la tabla de correspondencia de pginas

contiene una entrada para cada pgina del almacenamiento virtual del proceso.

Si el proceso tiene

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

n pginas en su memoria virtual, entonces, la tabla de pginas con correspondencia directa del proceso

contiene entradas sucesivas para las pginas 0,1,2,3,...., n-1.

La correspondencia directa es muy similar al acceso a un elemento de un vector mediante

ndices, es decir, cualquier entrada de la tabla puede localizarse directamente con un solo acceso.

Tanto la direccin virtual que se traduce, como la direccin base de la tabla de correspondencia

de pginas, se conservan en los registros de alta velocidad de la unidad de control del procesador, de

manera que, las operaciones en las que participan, puedan realizarse con rapidez dentro de un solo ciclo

de ejecucin de instrucciones.

No obstante, la tabla de pginas, con correspondencia directa, que puede ser muy grande, se

conserva normalmente en el almacenamiento primario. En consecuencia, la referencia a la tabla requiere

un ciclo completo de almacenamiento primario.

Como el tiempo de un ciclo de almacenamiento primario, representa la mayor parte de un ciclo

de ejecucin de instrucciones y se necesita un ciclo de almacenamiento primario adicional, para la

correspondencia de pginas, el empleo de traduccin de direcciones de pginas mediante

correspondencia directa, puede hacer que el sistema ejecute los programas en el doble del tiempo, que

se necesitara si no se utilizase el concepto de memoria virtual, es decir, se ejecutaran los procesos a la

mitad de la velocidad, lo cual es completamente inadmisible.

Por tanto, para lograr una traduccin ms rpida, las tecnologas de los sistemas actuales,

pueden colaborar en ello y colocar la tabla completa de correspondencia directa de pginas, en una

memoria asociativa de muy alta velocidad. Esto se ha podido conseguir, gracias a que los costos de

estas memorias, han disminuido notablemente, debido a los avances en la tecnologa de memorias.

TRADUCCIN DE DIRECCIONES POR CORRESPONDENCIA ASOCIATIVA.

Una forma de acelerar la traduccin dinmica de direcciones, es colocar toda la tabla de pginas,

dentro de un almacenamiento asociativo, accesible por contenido y no por direccin, el cual tiene ciclos,

de un orden de magnitud mucho ms rpidos, que los del almacenamiento primario.

La figura que se muestra a continuacin, muestra como se realiza la traduccin dinmica de

direcciones con una correspondencia asociativa pura.

N. PGINA

DESPLAZAMIENTO

DIR VIRTUAL (V)

V = (p,d)

TABLA DE PGINAS

N. MARCO DESPLAZAMIENTO

DIR REAL (R)

DIR REAL

R = p* Tp + d

Un programa en ejecucin hace referencia a una direccin virtual V = (p,d). Cada entrada en la

memoria asociativa se revisa en forma simultnea, para encontrar la pgina p, que una vez localizada,

devuelve p' como el marco de pgina que corresponde a p. El nmero del marco p' se multiplica por el

tamao de la pgina y se concatena con d, para formar la direccin real R= p*Tp + d.

En la figura se puede observar que las flechas dirigidas a la tabla de pginas situada en la

memoria asociativa, entran directamente en cada entrada. Esto indica que se revisa al mismo tiempo

cada entrada de la tabla de pginas, para buscar el valor de p.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

TEORIA DE LOS SISTEMAS OPERATIVOS

Para realizar la bsqueda as, es preciso incorporar al sistema un hardware especfico y esta

es la razn de que la memoria asociativa, tenga un costo mucho mayor, similar al que se necesita,

para la utilizacin de las memorias cach, por lo tanto, normalmente no se utiliza la correspondencia

asociativa pura.

TRADUCCIN DE DIRECCIONES CON CORRESPONDENCIA COMBINADA.

Actualmente la memoria la asociativa es mucho ms cara, que el almacenamiento real de acceso

directo, por lo tanto, los diseadores de los sistemas operativos, se han visto obligados a recurrir a un

mecanismo conciliador de correspondencia de pginas.

Este mecanismo consiste en utilizar una memoria asociativa, capaz de contener solo un pequeo

porcentaje de la tabla de correspondencia de pginas de un proceso.

Este reducido buffer de almacenamiento de bsqueda rpida, toma el nombre de TLB, Buffer

traduccin bsqueda anticipada (Translation Look-aside Buffer), este buffer mantiene solamente, las

correspondencias a las que se ha hecho referencia ms recientemente, pensando que estas sern las que

ms probabilidades tienen de ser solicitadas en un futuro prximo.

La traduccin dinmica de direcciones se realiza partiendo de una direccin virtual V = (p,d).

DIR. ORIGEN DE

TABLA PGINAS

N PGINA DESPLAZAMIENTO

DIR VIRTUAL

a

p

p

V = (p,d)

MAPA DE CORRESP.

ASOCIATIVA PARCIAL

p

p

TABLA PGINAS

N MARCO

DESPLAZAMIENTO

DIR. REAL

R = p*Tp + d

El mecanismo de traduccin intenta localizar la correspondencia a la pgina p en la memoria

asociativa, si lo encuentra, le devuelve p' como marco correspondiente a la pgina virtual p, que

posteriormente multiplicado por el tamao de la pgina, se concatena con el desplazamiento d, para

formar la direccin real R. Si no lo encuentra en la memoria asociativa, se buscar en el almacenamiento

principal de forma directa, tal y como se ha explicado anteriormente,

Una vez localizado el marco p' correspondiente a la pgina virtual p, adems de ser utilizado,

para formar la direccin real R, se actualizar el almacenamiento asociativo, para incluir esta

informacin, reemplazando a la entrada que ms tiempo lleva sin utilizarse.

El tamao del almacenamiento asociativo, no necesita ser muy grande, ya que se ha verificado

mediante la simulacin, que sistemas que utilizan esta tcnica, pueden resultar muy efectivos,

conteniendo solamente 8 o 16 registros de almacenamiento asociativo, alcanzando de esta manera, un

rendimiento prximo al 80%.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Como ya se expuso anteriormente, el porcentaje de ocasiones en que se encuentra un nmero de

pgina en los registros asociativos, se denomina tasa de aciertos.

Una tasa de aciertos del 80% significa, que en los registros asociativos, hemos encontrado el

nmero de pgina deseado el 80% de las ocasiones.

Si se supone que para buscar una pgina determinada en los registros asociativos, se emplea un

tiempo de 20 nanosegundos y se emplea un tiempo de 100 nanosegundos, para el acceso a memoria, el

tiempo de acceso total ser de 120 nanosegundos, cuando el nmero de pgina se encuentre en los

registros asociativos.

Si no se encuentra el nmero de pgina en los registros asociativos, se consumir un tiempo de

nanosegundos, para determinar que el nmero de pgina solicitado, no se encuentra en los registros

asociativos, a continuacin se deber acudir a la memoria principal, para obtener la tabla de pginas y el

nmero de marco, por el procedimiento directo que consumira un tiempo de 100 nanosegundos para

obtener la direccin de la tabla y posteriormente otros 100 nanosegundos, para obtener la pgina

deseada de la memoria, por lo tanto el tiempo de acceso total sumaria 230 nanosegundos.

20

Para determinar el tiempo de acceso efectivo a memoria, se debe ponderar cada caso por su

probabilidad:

Tiempo de acceso efectivo = 0,80 * 120 + 0,20 * 220 = 96 + 44 = 140 nanosegundos.

La utilizacin o no este mecanismo combinado, es una decisin de diseo basada en factores

econmicos y en las tecnologas de hardware existentes.

COMPARTICIN EN UN SISTEMA DE PAGINACIN.

En los sistemas multiprogramados, en especial los de tiempo compartido, es normal que muchos

usuarios ejecuten los mismos programas, si se asignaran copias individuales de estos programas para

cada usuario, se desperdiciara mucho almacenamiento primario, la solucin es compartir las pginas

que puedan compartirse.

La comparticin debe controlarse, para evitar que un proceso modifique los datos que esta

utilizando otro proceso, por lo tanto, en la mayor parte de los sistemas actuales, que realizan

compartimiento, los programas se dividen en reas separadas de procedimientos y datos.

Para que estos procedimientos sean compartidos tienen que ser reentrantes, que significa que no

pueden modificarse a s mismos. Los datos no modificables, como pueden ser las estructuras de datos

fijas, tambin pueden compartirse.

Todos estos conceptos hacen evidente, la necesidad de identificar si cada pgina se puede

compartir o no, clasificadas de esta forma las pginas de los procesos, se realiza el compartimiento.

SEGMENTACIN.

En los sistemas de almacenamiento virtual con segmentacin, una direccin virtual es un par

ordenado V = (s,d), donde s es el numero de segmento en el almacenamiento virtual, en donde se

encuentra el elemento al que se hace referencia y d es el desplazamiento dentro del segmento s en donde

se encuentra dicho elemento.

Un proceso solo se puede ejecutar, si su segmento activo se encuentra en la memoria principal y

los segmentos se transfieren desde la memoria virtual a la memoria real como unidades completas.

Un segmento entrante puede colocarse, en cualquier rea disponible de la memoria principal,

cuyo tamao sea suficiente para contenerlo y las estrategias de colocacin para la segmentacin, son

idnticas a las empleadas en la multiprogramacin con particiones variables, es decir, empleando las

tcnicas de primer ajuste, mejor ajuste y peor ajuste.

La traduccin dinmica de direcciones en la segmentacin de la siguiente forma:

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

TEORIA DE LOS SISTEMAS OPERATIVOS

REGISTRO ORIGEN

DE LA TABLA

DE SEGMENTOS

N. SEGMENTO DESPLAZAMIENTO

s

s

a

TABLA SEGMENTOS

d < LONG

d

s

LONG

BASE

DIR. VIRTUAL (V)

DIRECCIN REAL (R)

b+d

R = b + d

Si un proceso en ejecucin hace referencia a una direccin de almacenamiento virtual V = (s,d),

el mecanismo de correspondencia de segmentos utilizado por el sistema operativo, busca el segmento s

en la tabla de correspondencia de segmentos y determina que el segmento s se encuentra en el

almacenamiento real a partir de la direccin base b, por lo tanto, la direccin de almacenamiento real,

correspondiente a la direccin de almacenamiento virtual V = (s,d), ser la suma de b y d, previamente

ser preciso comprobar que el desplazamiento d es menor que la longitud.

CONTROL DE ACCESO EN LOS SISTEMAS CON SEGMENTACIN.

Una de las cualidades de los sistemas con segmentacin es el control del acceso que puede

realizarse, que se consigue asignando a cada proceso ciertos derechos de acceso a cada segmento,

denegando por completo el acceso a algunos segmentos, es decir, normalmente no es conveniente

otorgar a cada proceso un acceso ilimitado a todos los segmentos del sistema.

La proteccin del almacenamiento con claves, en una asignacin de almacenamiento no

contigua, en un sistema multiprogramado, se realiza mediante las claves de usuario, es decir, mientras la

clave de proteccin del procesador sea 2, correspondiente al usuario B, el programa del usuario B, solo

podr hacer referencia a los bloques del almacenamiento que tengan la proteccin 2.

Estas claves estn bajo el estricto control del sistema operativo y solo pueden manipularse

mediante instrucciones privilegiadas. Los tipos de control de acceso ms utilizados por los sistemas

actuales son los siguientes:

Si un proceso tiene acceso para lectura a un segmento, podr obtener cualquier informacin

contenida en el segmento y en algunos casos, podr realizar una copia completa del segmento.

Si el proceso tiene acceso para actualizar un segmento, puede modificar cualquier parte del

contenido del segmento y colocar informacin adicional. Si lo desea el proceso puede destruir la

informacin del segmento, aunque en algunos sistemas este derecho puede estar separado.

Un proceso con acceso para ejecucin a un segmento, puede ejecutar ese segmento como

programa. El acceso de ejecucin se suele denegar para segmentos de datos.

Un proceso con acceso para adicin a un segmento, puede agregar informacin adicional

solamente al final del segmento, pero no puede modificar la informacin existente.

TIPO ACCESO

ABREV.

EXPLICACIN

LECTURA

EL SEGMENTO SE PUEDE LEER

ACTUALIZACIN

EL SEGMENTO SE PUEDE ACTUALIZAR

EJECUCIN

EL SEGMENTO SE PUEDE EJECUTAR

ADICIN

EN EL SEGMENTO SE PUEDE AGREGAR

INFORMACIN AL FINAL.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

10

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Un sistema con estos cuatro tipos de control de acceso, se pueden crear 16 modos de control de

acceso diferentes, es decir, 2 4 . Con tres tipos de control se podran realizar los siguientes:

MODO

LECTURA

ESCRITURA

EJECUCIN

OBSERVACIONES

MODO 0

NO SE PERMITE EL ACCESO

MODO 1

SOLO EJECUCIN

MODO 2

NO TIENE SENTIDO

MODO 3

NO TIENE SENTIDO

MODO 4

SOLO LECTURA

MODO 5

LECTURA / EJECUCIN

MODO 6

LECTURA / ESCRITURA

MODO 7

ACCESO ILIMITADO

Este sencillo mecanismo de control de acceso descrito, constituye la base de la proteccin de

segmentos en muchos sistemas reales.

Del mismo modo que en los sistemas de paginacin, existen distintas estrategias, para realizar la

traduccin de direcciones con segmentacin, por lo tanto, pueden utilizarse los mismos mtodos

expuestos anteriormente:

Correspondencia directa.

Correspondencia asociativa.

Correspondencia combinada.

Estos mtodos pueden realizarse con memorias asociativas de tamao suficiente, para contener

toda la tabla de correspondencia de segmentos o con almacenamientos asociativos parciales de tamao

suficiente, para contener entradas para los segmentos a los que se hace referencia mas recientemente.

Por el momento, se va a tratar la traduccin de direcciones con segmentacin, empleando la

correspondencia directa, con toda la tabla de correspondencias de segmentos dentro de una memoria

cach de alta velocidad.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

11

TEORIA DE LOS SISTEMAS OPERATIVOS

Vamos a tratar de detallar ms, una entrada representativa de la tabla de segmentos.

BIT DE

RESIDENCIA

DIR LA MEM. VIRTUAL

SI EL SEGMENTO NO

EN EL ALM. PRINCIPAL

LONGITUD

SEGMENTO

LONG

BITS DE

PROTECCIN

R W E A B

DIR BASE DEL ALM. REAL

SI EL SEGMENTO EST EN

EL ALM. PRINCIPAL

r = 0 Si el segmento no est en el almacenamiento primario.

r = 1 Si el segmento est en el almacenamiento primario.

Un proceso en ejecucin, hace referencia a una direccin virtual V = (s,d). El nmero de

segmento s, debe utilizarse como ndice en la tabla de correspondencia, que comienza en la direccin a,

situada en el registro origen de la tabla de segmentos, para formar la direccin de memoria real se utiliza

el valor s como ndice en la tabla de correspondencia para determinar la entrada del segmento s de la

tabla de correspondencias. Si esta tabla contiene la direccin de memoria real b, en la cual, comienza el

segmento. El desplazamiento d, se suma a b, para formar la direccin real, R = b + d, correspondiente

a la direccin virtual V = (s,d).

En la figura se muestra con detalle, una entrada representativa de una tabla de correspondencias

de segmentos. Un bit de residencia r, indica si el segmento se encuentra o no en la memoria principal.

Si el segmento se encuentra en el almacenamiento principal, b es la direccin en la que comienza

el segmento. Si este no se encuentra en el almacenamiento principal, entonces, v es la direccin de la

memoria virtual, en donde debe leerse el segmento, antes de que el proceso pueda continuar su

ejecucin.

Ser preciso, verificar en todas las referencias al segmento, que el desplazamiento d es menor

que la longitud del segmento, para asegurar que se encuentra dentro de l.

Si el segmento no se encuentra en el almacenamiento principal, se produce una interrupcin, por

fallo de segmento, lo cual hace que el sistema operativo asuma el control y cargue el segmento desde la

direccin a de la memoria virtual a la memoria real.

COMPARTIMIENTO EN UN SISTEMA CON SEGMENTACIN.

Una de las ventajas que tiene la segmentacin sobre la paginacin es que la segmentacin es un

concepto lgico, no fsico.

En su forma general, los segmentos no estn restringidos de una manera arbitraria a un cierto

tamao, ya que estos pueden ser, dentro de unos limites razonables, tan grandes o tan pequeos como

sea necesario.

Un segmento correspondiente a una tabla tiene el tamao de la tabla y un segmento

correspondiente a una estructura de datos dinmica, puede crecer o decrecer segn lo haga la propia

estructura de datos.

Un segmento correspondiente a un cdigo de procedimientos generado por un compilador, ser

tan grande como sea necesario para contener el cdigo.

La comparticin de segmentos es bastante sencilla, en comparacin con la comparticin de una

pgina, en un sistema de paginacin.

Si un proceso en un sistema de paginacin ocupa tres pginas y media de longitud, entonces, en

lugar de tener entradas simples, para indicar el vector compartido, habr que tener entradas individuales,

para cada una de las pginas donde reside el proceso, por lo tanto, la gestin de una pgina parcial,

puede ser difcil.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

12

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

La situacin empeora con una estructura de datos dinmica, cuando una estructura as, crece y

ocupa una nueva pgina, las indicaciones de la comparticin en la tabla de correspondencia, debern

ajustarse en el momento de la ejecucin.

En un sistema con segmentacin, cuando el segmento se declara como compartido, las

estructuras de datos pueden crecer o decrecer, sin afectar a la informacin de la tabla de segmentos, que

indica el espacio donde residen los segmentos compartidos.

Para que dos procesos puedan compartir un segmento, basta que tengan entradas en sus tablas

de segmentos, que apunten al mismo segmento del almacenamiento principal.

SISTEMAS CON SEGMENTACIN / PAGINACIN COMBINADAS.

Los sistemas de paginacin y segmentacin, ofrecen ventajas significativas, como

organizaciones del almacenamiento virtual y se han construido sistemas que combinan la paginacin

con la segmentacin, ofreciendo las ventajas de ambas tcnicas de organizacin del almacenamiento

virtual.

Las caractersticas que se combinan en estos sistemas son:

Los segmentos tendrn un tamao que debe ser mltiplo del tamao de las pginas.

No es necesario que todas las pginas de un segmento estn en el almacenamiento primario

simultneamente.

Las pginas que son contiguas en el almacenamiento virtual, no tienen necesariamente que

ser contiguas en el almacenamiento real.

Las direcciones son tridimensionales por lo tanto una direccin de almacenamiento virtual

estar formada por los segmentos componentes v = (s, p, d) donde:

s

Nmero del segmento.

p

Nmero de pgina dentro del segmento.

d

Desplazamiento donde se encuentra el elemento de informacin deseado.

TRADUCCIN DINMICA DE DIRECCIONES EN SISTEMAS CON SEGMENTACIN/PAGINACIN.

Para la traduccin dinmica de direcciones virtuales a direcciones reales, en un sistema con

segmentacin paginada, se utiliza normalmente, la correspondencia combinada asociativa/directa tal y

como se muestra en la figura, que se expresa a continuacin:

Las pginas a las que se ha hecho referencia ms recientemente, tienen entradas en un

almacenamiento asociativo de tamao reducido.

Se realiza una bsqueda asociativa para tratar de localizar (s,p) en el almacenamiento asociativo,

si se encuentra (s,p), entonces el marco de pgina del almacenamiento primario p' en el cual reside la

pgina p del segmento s, se concatena con el desplazamiento d, para formar la direccin real R,

correspondiente a la direccin virtual: V = (s,p,d) con lo cual finaliza la traduccin de la direccin.

Normalmente, la mayor parte de las solicitudes de traduccin de direcciones, se satisfacen,

mediante la bsqueda en el almacenamiento asociativo, sin embargo, cuando esto no es posible se

establece una correspondencia directa de la siguiente forma.

En la direccin de comienzo a de la tabla de correspondencia directa de segmentos, en el

almacenamiento principal, se utiliza como ndice el nmero del segmento s, para determinar la

entrada del segmento s en la tabla de correspondencia, que indica la direccin base b de la tabla de

pginas, para el segmento s, en el almacenamiento principal

En la direccin b se toma como ndice el nmero de pgina p, que proporciona la entrada en la

tabla de pginas, para la pgina p del segmento s.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

13

TEORIA DE LOS SISTEMAS OPERATIVOS

Esta tabla indica que p es el nmero de marco de pgina que corresponde a la pgina virtual p,

que se concatena con el desplazamiento d, para formar la direccin real R, correspondiente a la

direccin virtual V = (s,p,d).

Un programa en ejecucin hace referencia a una direccin virtual V = (s,p,d).

DIR. ORIGEN DE

TAB. SEGMENTOS

DIRECCIN VIRTUAL

N. SEGMENTO

N. PAGINA

DESPLAZAMIENTO

d

TLB

s p

T. DE SEGMENTOS

DE UN PROCESO

T. DE PAGINAS PARA

EL SEGMENTO S

LPT

BPT

DIRECCIN REAL

R = p * Tp + d

En este proceso de traduccin se da por hecho, que cada elemento de informacin se encuentra

donde se supone que debe estar, pero hay muchos pasos en donde puede fallar el proceso.

La bsqueda en la tabla de correspondencia de segmentos puede indicar que el segmento s no se

encuentra en el almacenamiento principal, ocasionando una interrupcin por fallo de segmento y que el

sistema operativo tiene que resolver esa interrupcin, localizando el segmento en el almacenamiento

virtual, creando una tabla de pginas para el segmento y cargando la tabla de pginas apropiada en el

almacenamiento principal, reemplazando posiblemente a una tabla de pginas de este u otro proceso.

Si el segmento se encuentra en el almacenamiento primario, la referencia a la tabla de

correspondencia de pginas puede indicar que la pgina deseada no se encuentra en el almacenamiento

principal, lo cual generara una interrupcin por fallo de pgina y el sistema operativo tiene que resolver

esa interrupcin localizando la pgina en el almacenamiento virtual y cargndola en el almacenamiento

real, reemplazando posiblemente a otra pgina.

Al igual que en la segmentacin pura, una direccin de almacenamiento virtual puede rebasar el

final del segmento generando as una excepcin por desbordamiento de segmento. Por otra parte los

bits de proteccin tambin pueden marcar, que no est permitida la operacin que se pretende realizar,

generndose as una interrupcin por proteccin del segmento.

Todos estos problemas que se

pueden producir nos indican que el almacenamiento asociativo es crtico para la operacin eficiente de

este mecanismo de traduccin dinmica.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

14

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Si se utilizara un mecanismo de correspondencia directa pura, manteniendo la tabla de

correspondencia completa dentro del almacenamiento primario, el promedio de referencias al

almacenamiento virtual, requerira un ciclo de almacenamiento, para obtener acceso a la tabla de

correspondencia de segmentos, un segundo ciclo para hacer referencia a la tabla de correspondencia de

pginas y un tercer ciclo para hacer referencia al elemento deseado en el almacenamiento real.

De esta manera cada referencia a un elemento implicara tres ciclos de almacenamiento y el

sistema funcionara a un tercio de su velocidad normal, con lo que consumira dos tercios de su tiempo

en la traduccin de direcciones.

Resulta interesante que muchos sistemas logren operar al 90% o ms de velocidad mxima de

sus procesadores de control, con solo 8 o 16 registros asociativos.

En la figura que se expresa a continuacin, se presenta una estructura detallada de las tablas

requeridas por un sistema con paginacin/segmentacin.

TABLAS DE PGINAS

TABLAS DE SEGMENTOS

UNA POR CADA PROCESO

UNA POR SEGMENTO

.

.

M. PRINCIPAL

.

TABLAS DE PROCESOS

DEL SISTEMA OPERATIVO

b

.

.

.

.

.

.

.

.

.

.

.

En el nivel ms alto, esta una tabla de procesos que contiene una entrada por cada proceso

conocido por el sistema. La entrada en dicha tabla para un proceso dado, apunta a la tabla de

correspondencia de segmentos del proceso.

Cada entrada en la tabla de correspondencia de segmentos de un proceso, apunta a la tabla de

correspondencia de pginas del segmento asociado y cada entrada de esa tabla, apunta al marco de

pgina donde reside esa pgina o bien la direccin en el almacenamiento secundario donde puede

encontrarse la pgina.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

15

TEORIA DE LOS SISTEMAS OPERATIVOS

En un sistema con un nmero muy grande de procesos, segmentos y pginas, esta estructura

de tablas puede consumir una parte importante del almacenamiento primario. La cuestin aqu es que

la traduccin de direcciones, se realiza con ms rapidez en el momento de la ejecucin, si todas las

tablas estn en el almacenamiento principal. Ahora bien, si existen ms tablas en el almacenamiento

principal, el sistema tiene capacidad para menos procesos y de esta manera baja la productividad.

Los diseadores de sistemas operativos, deben evaluar dicha cuestin, para lograr el delicado

equilibrio necesario, para que el sistema funcione eficientemente y proporcione un servicio seguro a

cada uno de sus usuarios.

SISTEMAS DE PAGINACIN SEGMENTADA.

Cuando el tamao de palabra de una maquina aumenta y el nmero de bits utilizados para definir

el nmero de pgina es alto, la cantidad de pginas que podemos tener crece de forma alarmante y con

ello el tamao de la tabla de pginas, haciendo que las bsquedas se hagan muy lentas y el mtodo de la

paginacin pierda toda su eficacia.

Una posible solucin consiste en segmentar la tabla de pginas, que debe ser muy grande, con lo

que ahorramos tener que recorrer toda la tabla. Dicha solucin es utilizada por los grandes sistemas

operativos de la familia IBM.

El diagrama que se expresa a continuacin, indica como se realiza la conversin de una

direccin lgica a una direccin fsica, en este sistema.

DIRECCIN

ORIGEN DE

T. SEGEMENTOS

STBR

DIRECCIN VIRTUAL

SEGM. DE LA T. PAG

LTP

BTP

ERROR

p< LTP

T. PGINAS

p m

m * TP + d

DIRECCIN REAL

En la direccin origen de la tabla de segmentos STBR, se toma como ndice el nmero de

segmento s, y se accede a la entrada correspondiente de la tabla de segmentos, donde se encuentra la

longitud de la tabla de pginas y la base de dicha tabla.

La primera LTP, la utiliza para compararla con la direccin binaria p y comprobar si se comete

algn error, por ser la direccin p demasiado grande. La segunda se aade a la direccin p, para

acceder al elemento correspondiente de la tabla de pginas, obteniendo as, el valor del marco de pgina

necesario, para obtener la direccin real de la memoria.

Este mtodo consiste, en segmentar la tabla de pginas, cuando el nmero de pginas es muy

grande y los segmentos en que se divide la tabla de pginas pueden ser de tamao variable.

COMPARTIMIENTO EN UN SISTEMA CON PAGINACIN/SEGMENTACIN.

En los sistemas con paginacin/segmentacin, son muy importantes las ventajas de compartir

segmentos. El compartimiento se logra, mediante entradas en las tablas de correspondencia de

segmentos de diferentes procesos, que apuntan a la misma tabla de correspondencia de pginas.

El compartimiento tanto en sistemas de paginacin, como en aquellos con segmentacin o

paginacin/segmentacin, requiere un cuidadoso manejo por parte del sistema operativo.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

16

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Es preciso considerar lo que sucedera, si una pgina entrante reemplazara, una pgina

compartida por varios procesos.

T. DE SEGMENTOS

PROCESO A

T. DE PGINAS

SEGMENTOS

PROCESO A

T. DE PROCESOS

*

COMPARTIDOS

PROCESO B

*

*

PROCESO B

ADMINISTRACIN DE LA MEMORIA VIRTUAL.

Anteriormente hemos analizado los distintos esquemas que se pueden utilizar para la gestin de

memoria en los sistemas operativos.

De todos estos esquemas algunos son los ms apropiados para la gestin de memoria en los

sistemas de almacenamiento real, otros se consideran ms apropiados para la gestin de memoria en los

sistemas de almacenamiento virtual y alguno se puede utilizar en ambos sistemas.

Todos estos esquemas tienen un objetivo comn, que consiste en mantener simultneamente

varios procesos en memoria, para permitir la multiprogramacin; no obstante, no todos ellos requieren

que el proceso completo se encuentre en la memoria, antes de poder ejecutarlo.

Las tcnicas que se pueden utilizar, para la administracin de la memoria virtual, permiten la

ejecucin de procesos, que no estn totalmente cargados en la memoria real, siendo esta la principal

ventaja de la utilizacin de la memoria virtual, que consiste en que los programas pueden ser mayores

que el espacio de memoria real asignado para ellos, liberando a los programadores de la preocupacin

por las limitaciones de la memoria real.

No obstante, por todas las consideraciones expuestas con anterioridad, se puede llegar a la

conclusin, de que el concepto de memoria virtual no es fcil de implantar y si no se disea de una

manera eficiente, puede reducir considerablemente el rendimiento del sistema.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

17

TEORIA DE LOS SISTEMAS OPERATIVOS

Una vez analizados los distintos problemas que se pueden presentar con la utilizacin de una

estrategia u otra, para la gestin de la memoria virtual:

Paginacin.

Segmentacin.

Segmentacin paginada.

Se trata ahora, de analizar aquellos aspectos, que son especficos de la administracin de la

memoria virtual, que pueden exigir la incorporacin de tcnicas actuales, para conseguir el rendimiento

ms adecuado en el sistema.

PAGINACIN POR DEMANDA.

La paginacin por demanda tiene por objeto, introducir en la memoria real las pginas que son

necesarias, para la ejecucin de los procesos.

Si se examina un programa cualquiera, se puede llegar a la conclusin de que en la mayora de

los casos, no es preciso mantener el programa completo en la memoria, para que este pueda ser

ejecutado.

Las conclusiones que se obtienen del examen anteriormente citado son las siguientes:

Los programas en general, contienen un conjunto de instrucciones para la gestin de errores

poco frecuentes, que se ejecutarn en muy contadas ocasiones.

Existirn diferentes estructuras de datos, a las que normalmente se le asigna ms memoria de

la que realmente necesitan.

Ciertas opciones y caractersticas de un programa, se han incluido para el tratamiento de

situaciones que no se presentan normalmente.

Incluso en aquellos casos en que se necesitara todo el programa, es probable, que no se requiera

todo al mismo tiempo.

La capacidad de ejecutar un programa que se encuentra parcialmente en memoria puede tener

las siguientes ventajas:

Un programa ya no estar restringido por la cantidad de memoria fsica disponible, por lo

tanto, los usuarios podrn escribir los programas, para un espacio virtual muy grande,

simplificando la programacin.

Como cada programa de usuario ocupar menos memoria fsica, podrn ejecutarse ms

programas simultneamente, aumentando la utilizacin del procesador y la productividad del

sistema, sin incrementar el tiempo de respuesta o el tiempo de retorno.

Se requerir menos tiempo para las operaciones de E/S, ya que para cargar o intercambiar

cada uno de los procesos del usuario, no se necesita hacerlo del proceso completo, por lo

que se aumentar la velocidad de ejecucin.

Por todas estas consideraciones, un programa en ejecucin, que no se encuentre totalmente en la

memoria, beneficia tanto al usuario como al sistema.

Generalmente la tcnica, que se utiliza para la administracin de la memoria virtual, es la

paginacin por demanda, pero tambin puede implantarse en un sistema de segmentacin, ya que

algunos sistemas ofrecen un esquema de segmentacin paginada, donde los segmentos se dividen en

pginas.

De esta manera, la perspectiva del usuario es la segmentacin, pero el sistema operativo puede

implantar esta perspectiva con la paginacin por demanda.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

18

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

La segmentacin por demanda tambin puede utilizarse, para la administracin de la memoria

virtual, pero los algoritmos de sustitucin de segmentos, son mucho ms complejos, que los de

sustitucin de pginas, dado que los segmentos tienen tamaos variables.

Un sistema de paginacin por demanda, es muy similar a un sistema de paginacin, en el que ha

sido preciso incluir los intercambios de pginas, es decir, los procesos residen normalmente en la

memoria virtual y cuando se quiere ejecutar un proceso, se van introduciendo en la memoria principal

las pginas que son necesarias, por lo tanto, el intercambio no se produce por procesos completos, sino

por pginas y no se incorporar a la memoria una pgina, a menos que se necesite.

Segn este concepto, el proceso se considera como una secuencia de pginas, en vez de un gran

espacio contiguo de direcciones. En este caso, el trmino intercambio no es totalmente correcto, ya que

un intercambio, manipula procesos completos, mientras que ahora, lo que se necesita es un paginador,

que intercambie las pginas individuales de un proceso, por ello se debe utilizar, el trmino paginar en

lugar de intercambiar, en la paginacin por demanda.

La paginacin por demanda incorpora a la memoria solamente las pginas necesarias, evitando

as, colocar en memoria pginas que nunca se utilizarn, reduciendo as el tiempo de intercambio y la

cantidad de memoria fsica necesaria.

Este esquema de administracin de memoria requiere apoyo del hardware, que se ha definido

para la paginacin y en cada entrada de la tabla de pginas, existir un bit de residencia, que indicar si

la pgina esta en la memoria real (1) o por el contrario la pgina est en la memoria virtual (0).

Si introducimos solamente las pginas que realmente se necesitan, el proceso se ejecutar de la

misma forma, que si hubiramos incorporado todas las pginas, ya que mientras el proceso se ejecuta y

accede a pginas residentes en memoria, la ejecucin prosigue normalmente.

A continuacin se expresa el modelo de comportamiento utilizado en la paginacin por

demanda, muy similar al modelo que se ha descrito anteriormente para la paginacin.

PAG 0

PAG 1

TABLA DE

CORRESPONDENCIA

PAG 2

*

*

*

PAG

MEMORIA VIRTUAL

MEMORIA SECUNDARIA

MEMORIA REAL

Si se trata de utilizar una pgina que no este incorporada a la memoria, se producir una

interrupcin por falta de pgina, es decir, el hardware de paginacin, al traducir la direccin mediante la

tabla de pginas, observar que el bit de residencia es 0, generando la interrupcin para que el sistema

operativo, haga la transferencia de esa pgina a la memoria real desde el almacenamiento secundario.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

19

TEORIA DE LOS SISTEMAS OPERATIVOS

S:O:

SELECCIONAR MARCO LIBRE EN LA LISTA DE DISPONIBLES

BUSCAR EN LA MEMORIA SECUNDARIA

MOVER M

1 REFERENCIA

6 REINICIAR

INSTRUCCIN

2 INTERRUPCIN

0

M LIBRE

5 RESTABLECER

TABLA PGINAS

4 CARGAR LA

PGINA QUE FALTA

El proceso que se realiza es el siguiente:

1.

2.

3.

4.

5.

Consultar la tabla de pginas, para determinar si la pgina est en memoria real.

Si la pgina no est en la memoria real, se produce una interrupcin por fallo de pgina.

Localizar un marco que est libre en la lista de marcos libres, para la carga de la pgina.

Planificar la operacin para leer la pgina deseada, en el marco recin asignado.

Realizada la carga de la pgina en el marco elegido, modificar el contenido de la tabla de

pginas.

6. Reiniciar a continuacin, la instruccin interrumpida.

Es importante observar, que como en el momento de la interrupcin, se guarda el estado del

proceso interrumpido, por lo tanto, se puede reanudar el proceso en el mismo punto y estado, excepto

que ahora la pgina deseada ya se encuentra en memoria.

En un caso extremo, podemos comenzar la ejecucin de un proceso sin pginas en memoria, de

esta forma, con la primera instruccin, el proceso presentara un fallo de pgina, despus de traer a

memoria esta pgina, el proceso continuara su ejecucin, provocando fallos de pgina, cuando sea

necesario, hasta que todas las pginas que necesita se encuentren en memoria, al llegar a este punto, se

podra ejecutar sin ms fallos de pgina y a este proceso, se le denomina Paginacin por demanda pura y

consiste en no traer una pgina a memoria hasta que se requiera.

En teora, algunos programas pueden acceder a una nueva pgina de memoria con cada

instruccin que ejecutan, esta situacin provocara un rendimiento inaceptable, sin embargo, los

anlisis de procesos en ejecucin han mostrado que esta situacin es muy poco probable, debido

fundamentalmente al principio de cercana ya que los programas suelen poseer una localidad de

referencias, que estn relativamente prximas, brindando un rendimiento aceptable en la paginacin

por demanda.

El hardware para apoyar la paginacin por demanda, es el mismo que se utiliza para la

paginacin y los intercambios y est compuesto por:

Una memoria virtual, donde estn situadas las pginas para llevar a cabo el proceso de

traduccin de direcciones virtuales a direcciones reales.

Una tabla de pginas, con capacidad para determinar s la pgina esta en la memoria real o

no y un valor especial para los bits de proteccin.

Una memoria principal, que contiene las pginas del proceso que se necesitan para la

ejecucin, es decir, las pginas activas.

Una memoria secundaria, que contiene las pginas, que no estn en la memoria principal y

normalmente, es un disco de alta velocidad que se denomina dispositivo de intercambios.

Adems de esta ayuda del hardware, se requiere un considerable apoyo del software, como se

ver ms adelante.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

20

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Un aspecto critico de esta tcnica, es la capacidad para reiniciar cualquier instruccin, despus

de un fallo de pgina. En la mayora de los casos, es fcil cumplir con este requisito, ya que un fallo de

pgina, puede ocurrir en cualquier referencia a memoria.

Si el fallo de pgina ocurre al buscar la instruccin, se puede reiniciar efectuando de nuevo la

bsqueda, pero si el fallo de pgina ocurre al buscar un operando, ser necesario buscar de nuevo la

instruccin, decodificarla y luego buscar el operando.

En el peor de los casos, si consideramos una instruccin de tres direcciones, como por ejemplo,

colocando el resultado en C. Los pasos para ejecutar esta instruccin sern:

ADD A y B,

1.

2.

3.

4.

5.

Buscar y decodificar la instruccin ADD.

Buscar A.

Buscar B.

Sumar A y B.

Guardar el resultado en C

Si se presenta el fallo de pgina al tratar de almacenar C, porque C est en una pgina, que no se

encuentra actualmente en memoria, tendremos que obtener la pgina deseada, traerla a memoria,

modificar la tabla de pginas y reiniciar la instruccin, que implicara buscar de nuevo la instruccin,

decodificarla, buscar una vez ms los dos operandos y volver a sumar. El trabajo que se repite es inferior

a una instruccin completa y solo seria necesario si ocurre un fallo de pgina en ese momento.

La principal dificultad surge cuando la instruccin puede modificar varias localidades distintas.

Por ejemplo, la instruccin MVC (Mover Carcter), que puede mover hasta 256 bytes de una

localidad a otra, que pueden coincidir parcialmente, si alguno de los bloques fuente o destino sobrepasa

un limite de pgina, puede ocurrir un fallo de pgina, despus de haber efectuado parte de la

transferencia y adems si los bloques fuente y destino se superponen, es probable que se modifique el

bloque fuente y por lo tanto impedir que se pueda reiniciar la instruccin.

A

Este problema se puede resolver de dos maneras, dependiendo del modelo:

Una solucin sera disponer de un microcdigo adecuado, para calcular y tratar de acceder a

ambos extremos de los dos bloques, con objeto de comprobar, que si va a ocurrir un fallo de

pgina suceda en esta etapa antes de modificar algo, de esta manera se podr realizar la

transferencia, sabiendo que no va a ocurrir ningn fallo de pgina.

La otra solucin podra ser utilizar registros temporales, para contener los valores de las

localidades sobrescritas, si se presenta un fallo de pgina, todos los valores que haba antes

de que ocurriese la interrupcin regresan a la memoria. Esta accin restablece la memoria a

su estado anterior a la ejecucin de la instruccin, por lo que podemos repetir la instruccin.

Estos no son los nicos problemas que surgen al aadir la paginacin a una arquitectura

existente, para permitir la paginacin por demanda, pero si ilustran algunas de las dificultades.

En un sistema informtico, la paginacin se inserta entre la UCP y la memoria y debe ser

completamente transparente para el proceso del usuario, por ello, con frecuencia el usuario supone que

la paginacin se puede aadir a cualquier sistema.

RENDIMIENTO DE LA PAGINACIN POR DEMANDA.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

TEORIA DE LOS SISTEMAS OPERATIVOS

21

La paginacin por demanda puede tener un efecto considerable, en el rendimiento de un sistema

informtico. Para ver la razn, se puede calcular el tiempo de acceso efectivo para la memoria paginada

por demanda.

El tiempo de acceso a memoria (am), para la mayora de los sistemas informticos actuales, esta

entre 10 y 200 nanosegundos, mientras no tengamos fallos de pgina, el tiempo de acceso efectivo es

igual al tiempo de acceso a memoria.

Sin embargo, si ocurre un fallo de pgina, primero debemos leer del disco la pgina indicada y

luego acceder a la palabra deseada.

Sea p la probabilidad de que ocurra un fallo de pgina, siendo 0 < p < 1, podemos esperar que p

este muy cercano a cero, es decir, que habr pocos fallos de pgina.

El tiempo de acceso efectivo = (1-p) * am + p * TFP, siendo TFP el tiempo de fallo pgina.

Para calcular el tiempo de acceso efectivo, necesitamos saber cuanto tiempo se requiere para

servir un fallo de pgina.

Un fallo de pgina desencadena la siguiente secuencia:

1. Interrupcin para el sistema operativo.

2. Determinar si la interrupcin es un fallo de pgina.

3. Verificar si la referencia a la pgina ha sido legal y determinar la ubicacin de la pgina en el

disco.

4. Guardar los registros de usuario y el estado del procesador.

5. Durante la espera, asignar la UCP a otro usuario.

6. Leer del disco a un marco libre.

Esperar en la cola del dispositivo.

Esperar el tiempo de posicionamiento y latencia.

Comenzar la transferencia de la pgina al marco libre.

7. Interrupcin del disco, para comunicar la finalizacin de la operacin de E/S.

8. El sistema operativo determina, si la interrupcin proviene del disco.

9. Guardar los registros y el estado del procesador del usuario que lo est utilizando.

10. Actualizar la tabla de pginas y las dems tablas, para indicar que la pgina deseada se

encuentra en memoria.

11. Esperar que la UCP se le asigne nuevamente a este proceso.

12. Restablecer los registros de usuario, estado del procesador y nueva tabla de pginas y

reanudar la instruccin interrumpida

Es posible que no siempre sean necesarios todos los pasos, pero en cualquier caso, nos

enfrentamos a tres componentes principales del tiempo de servicio del fallo de pgina:

Servir la interrupcin de fallo de pgina.

Leer la pgina.

Reanudar el proceso.

La primera y tercera tareas pueden reducirse con una codificacin cuidadosa a varios cientos de

instrucciones y pueden suponer una media de 100 microsegundos cada una, sin embargo, el tiempo de

cambio de pgina estar prximo a los 25 milisegundos.

Un disco de cabeza mvil tpico tiene un tiempo medio de posicionamiento de 15 milisegundos,

un tiempo medio de latencia de 8 milisegundos y un tiempo medio de transferencia de un milisegundo,

por lo tanto, el tiempo total de paginacin estar muy prximo a los 25 milisegundos.

Si una cola de procesos que esperan al dispositivo, es decir, otros procesos que han provocado

fallos de pgina, se debe aadir el tiempo de espera en la cola, mientras que el dispositivo de paginacin

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

22

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

est ocupado por otros procesos, antes de atender nuestra solicitud, lo cual incrementa ms aun nuestro

tiempo de intercambio.

De esta manera, si tomamos un tiempo promedio de servicio de fallo de pgina de 25

milisegundos y un tiempo de acceso a memoria de 100 nanosegundos, entonces el tiempo de acceso

efectivo expresado en nanosegundos sera:

Tiempo de acceso efectivo = (1-p) * 100 + p * 25 msg.= (1-p) * 100 + p * 25.000.000 nanoseg. =

= 100 + 24.999.900 * p

Se comprueba, que el tiempo de acceso efectivo es directamente proporcional a la tasa de fallos

de pgina, por lo tanto, si se considera que un acceso de cada mil provoca un fallo de pgina, el tiempo

de acceso efectivo es aproximadamente de 25.000 microsegundos, es decir, 25 milisegundos.

25.000.000/1.000 = 25.000 por tanto, la relacin 25.000/100 nos indicara que, el computador

250 veces ms lento debido a la paginacin por demanda y eso no sera admisible.

sera

Si un acceso de cada 25.000 provoca un fallo de pgina, el tiempo de acceso efectivo es de 1.000

nanosegundos, es decir, un microsegundo.

25.000.000/25.000 = 1.000 por tanto, la relacin 1.000/100 nos indicara, que el computador sera en

este caso, 10 veces ms lento debido a la paginacin por demanda y esto si que podra ser admisible.

Por lo tanto, si queremos una degradacin menor al 10% se necesitara:

110 > 100 + 25.000.000

10 > 25.000.000 * p

*p

Por tanto, la probabilidad sera:

p < 10 / 25.000.000 = 4 * 10

p < 0,0000004

Esto quiere decir, que para mantener un nivel razonable, la lentitud adicional provocada por la

paginacin por demanda, solo puede permitir, que menos de un acceso a memoria de cada 2.500.000,

tenga un fallo de pgina.

Es muy importante, mantener muy baja la tasa de fallos de pgina, en un sistema de paginacin

por demanda, ya que sino es as, aumenta el tiempo de acceso efectivo, frenando considerablemente la

ejecucin de los procesos.

La asignacin de solo un conjunto de marcos de pgina, a un proceso determinado, requiere la

incorporacin de ciertas polticas de diseo en el gestor de memoria virtual.

En trminos de su orden relativo de aparicin cuando se gestiona un proceso se pueden

establecer estas polticas:

Asignacin, cantidad de memoria real que se asigna a cada

proceso activo.

Bsqueda y lectura, que tiene por objeto determinar, que

elementos introducir en la memoria y cuando introducirlos desde la memoria secundaria a la

memoria principal.

Sustitucin, cuando un elemento nuevo tiene que ser

introducido en la memoria y no hay memoria libre, que elemento intercambiar, para hacer sitio

al nuevo elemento.

Colocacin, donde se debe situar un elemento nuevo.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

23

TEORIA DE LOS SISTEMAS OPERATIVOS

SUSTITUCIN DE PGINAS.

En la presentacin que se ha realizado hasta el momento, la tasa de fallos de pgina no

representa un gran problema, ya que como mximo se produce un fallo por cada pgina, cuando se

hace referencia a ella por primera vez, sin embargo, esta representacin no es muy exacta, ya que si

un proceso de 10 pginas solo emplea la mitad de ellas, entonces la paginacin por demanda, ahorra

la E/S necesaria para cargar cinco pginas que nunca se usarn.

Se puede aumentar el nivel de multiprogramacin ejecutando el doble de procesos, ya que si

tuvisemos 50 marcos, podramos ejecutar diez procesos, en lugar de los cinco, que se ejecutaran, si

cada uno necesitara 10 marcos, aunque cinco de ellos no se usaran nunca.

Residencia N. Marco

0

M. VIRTUAL

A

4

T. DE PGINAS

M. VIRTUAL

R

M. REAL

A

M

MEM. SECUNDARIA

T. DE PGINAS

Si se aumenta el nivel de multiprogramacin, sin duda, se est produciendo una sobreasignacin

de la memoria, ya que si se ejecutan ocho procesos, cada uno con diez pginas, pero que solo utilizan

cinco pginas, se obtiene una mayor utilizacin de la UCP y por lo tanto, una mayor productividad con

diez marcos de sobra.

Sin embargo puede ocurrir que en un momento determinado, cada uno de estos procesos

intente utilizar sus diez pginas, entonces, seran necesarios 80 marcos, cuando solo tenemos 50.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

24

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Aunque esta solucin es muy poco probable, es posible que se produzca una sobreasignacin y es

necesario tratarla.

S se supone, que est ejecutndose un proceso de usuario y ocurre un fallo de pgina, se

produce una interrupcin y el control pasa al sistema operativo, el cual consulta sus tablas internas y

determina s se trata de un fallo de pgina o de un acceso ilegal a la memoria.

El sistema operativo determina en que lugar del disco se encuentra la pgina deseada,

posteriormente se comprueba que no existen marcos libres. Al llegar a este punto, el sistema operativo

podra abortar el proceso de usuario, sin embargo, la paginacin por demanda, es una tcnica, que el

sistema operativo proporciona, para mejorar la utilizacin y la productividad del sistema informtico,

por lo tanto, se pueden producir distintas estrategias para solucionar el problema.

Una primera estrategia consiste en descargar un proceso y liberar todos sus marcos, reduciendo

el nivel de multiprogramacin, esto puede ser una buena idea y la consideraremos con mayor detalle

posteriormente.

Otra estrategia quiz ms interesante podra ser el reemplazo de pginas, que consiste en lo que

se va a exponer a continuacin.

Si no hay ningn marco libre, se busca uno que no se est utilizando en ese momento y lo

liberamos. Se puede liberar un marco escribiendo en el disco todo su contenido y modificando la tabla

de pginas y todas las dems tablas, para indicar que la pgina ya no se encuentra en memoria.

El marco liberado puede usarse ahora para contener la pgina por la cual fall el proceso, de

esta manera, se modifica la rutina de servicio del fallo de pgina, para incluir el reemplazo de pgina.

1. Encontrar la ubicacin en disco de la pgina deseada.

2. Buscar un marco libre:

Si hay un marco libre, utilizarlo.

De lo contrario, utilizar un algoritmo de reemplazo de pgina, para seleccionar la

vctima.

Escribir la pgina vctima en disco y modificar la tabla de pginas.

3. Copiar la pgina deseada en el nuevo marco libre y modificar la tabla de pginas.

4. Reanudar el proceso de usuario.

Es preciso observar que si no quedan marcos libres, se requieren dos transferencias, una de

entrada y otra de salida. Esta situacin duplica el tiempo de servicio de un fallo de pgina y en

consecuencia aumentar el tiempo de acceso efectivo.

Este tiempo de proceso adicional, se puede reducir utilizando un bit de modificacin, as cada

pgina o marco puede tener asociado un bit de modificacin en el hardware, que pone el bit de

modificacin en 1 para una pgina, cuando en ella se realiza alguna modificacin.

Cuando se selecciona una pgina para reemplazo, examinamos su bit de modificacin y si esta

activo, sabemos que la pgina ha sido modificada, por lo tanto, debemos escribirla en el disco

nuevamente, en el caso de que el bit de modificacin no este activo no ser necesario escribirla sobre el

disco. Del mismo modo, tampoco ser necesario copiar la pgina en el disco, si los bits de proteccin

indican que la pgina es de solo lectura.

Este esquema puede reducir considerablemente el tiempo para servir un fallo de pgina, ya que

reduce a la mitad el tiempo de E/S, si la pgina no se ha modificado.

El reemplazo de pginas es esencial para la paginacin por demanda, pues completa la

separacin entre la memoria lgica y la memoria fsica.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

25

TEORIA DE LOS SISTEMAS OPERATIVOS

Con la paginacin por demanda, el espacio de direcciones lgicas ya no esta restringido por la

memoria fsica y si tenemos un proceso de 20 pginas, podemos ejecutarlo en 10 marcos, empleando un

algoritmo de reemplazo, para encontrar un marco libre cuando sea necesario.

Para implantar la paginacin por demanda debemos resolver dos grandes problemas:

Desarrollar un algoritmo de asignacin de marcos.

Desarrollar algoritmos para el reemplazo de pginas.

El diseo de algoritmos adecuados para resolver estos problemas es una tarea importante, ya

que la E/S de disco es muy costosa, por lo tanto, una pequea mejora en los mtodos de paginacin por

demanda, produce amplias ganancias en el rendimiento del sistema.

ALGORITMOS DE REEMPLAZO DE PGINAS.

Existen diferentes algoritmos para el reemplazo de pginas y cada sistema operativo, cuenta con

su propio esquema de reemplazo de pginas.

Para la evaluacin de los distintos algoritmos, utilizaremos una determinada serie de referencias

a memoria y sobre ella calcular l nmero de fallos de pgina.

Esta serie de referencias se puede generar:

Utilizando un generador de nmeros aleatorios.

Rastreando el sistema y anotando la direccin de cada referencia a memoria.

Para determinar el nmero de fallos de pgina, para una serie de referencias y un algoritmo de

reemplazo de pginas determinado, necesitamos conocer tambin el nmero de marcos de pgina

disponibles.

En teora, si el nmero de marcos disponibles aumenta, se debe reducir el nmero de fallos de

pgina, tal y como se expresa en la figura.

Nmero de

Fallos Pgina

Nmero de Marcos

Para evaluar los algoritmos de reemplazo de pginas, utilizaremos la siguiente serie de

referencias:

7, 0, 1, 2, 0, 3, 0, 4, 2, 3, 0, 3, 2, 1, 2, 0, 1, 7, 0, 1.

Al no disponer por el momento de los adecuados algoritmos de asignacin de memoria, se

utilizar para la evaluacin tres marcos de pgina.

ALGORITMO FIFO. (First-In First-out).

El algoritmo ms sencillo es el algoritmo Primero en entrar Primero en salir. Segn este

algoritmo, cuando se necesita sustituir una pgina, se elegir aquella que lleve ms tiempo en memoria.

Para controlar el tiempo de permanencia en memoria de las pginas, se utiliza una cola de llegada a

memoria de las mismas.

APUNTES DE SISTEMAS OPERATIVOS

ANGEL GLEZ. DEL ALBA

26

GESTIN Y ADMINISTRACIN DE LA MEMORIA VIRTUAL

Aplicando este algoritmo a la serie de referencias anterior:

7 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 7 0 1

7 7 7

0 0

1

x x x

2

0

1

x

2

3

1

x

2

3

0

x

4

3

0

x

4

2

0

x

4

2

3

x

0

2

3

x

0

1

3

x

0

1

2

x

7

1

2

x

7

0

2

x

7

0

1

x

Este algoritmo provoca 15 fallos de pgina.

Un criterio de seleccin tan simple es fcil de programar y adems producir poca sobrecarga en

el sistema. Su eficacia es relativa, ya que puede ocurrir que la pgina que lleva ms tiempo en memoria

sea la de mayor utilizacin y en este el algoritmo sustituir la pgina menos adecuada.

Por ejemplo, en un sistema de tiempo compartido, en el que varios usuarios estn utilizando el

mismo programa, compartiendo sus pginas. Normalmente sern estas pginas las que ms tiempo

lleven en la memoria y aunque su utilizacin es muy alta, el criterio FIFO las reemplazar provocando

inmediatamente una serie de fallos de pgina.

Por lo tanto, el algoritmo FIFO, no ser el ms adecuado para los sistemas de tiempo

compartido, pero puede ser til en otros tipos de sistemas operativos.

Si el algoritmo FIFO se aplica a la serie de referencias siguiente: 1, 2, 3, 4, 1, 2, 5, 1, 2, 3, 4, 5

16 __

N DE FALLOS

14 __

12 __

DE PGINA

10 __

9 __

6 __

5 __

4 __

2 __

N DE MARCOS DE PGINA

1 2 3 4 1 2 5 1 2 3 4 5

1 1 1

2 2

3

x x x

4

2

3

x

4

1

3

x

4

1

2

x

5

1

2

x

5

3

2

x

APUNTES DE SISTEMAS OPERATIVOS

5

3

4

x

Total 9 Fallos

ANGEL GLEZ. DEL ALBA

27

TEORIA DE LOS SISTEMAS OPERATIVOS

Si incrementamos en uno los marcos disponibles, veremos que la tasa de fallas es mayor.

1 2 3 4 1 2 5 1 2 3 4 5

1 1 1 1

2 2 2

3 3

4

x x x x

5

2

3

4

x

5

1

3

4

x

5

1

2

4

x

5

1

2

3

x

4

1

2

3

x

4

5

2

3

x

Total 10 fallos

Parece lgico pensar que el nmero de fallos de pgina, debera disminuir al ir aumentando el

nmero de marcos disponibles, sin embargo, si observamos la figura, al pasar de 3 a 4 marcos el nmero

de fallos de pgina aumenta, pasando de 9 a 10 fallos de pgina.

Este resultado va en contra de la teora anteriormente citada y se denomina Anomala de Belady,

la cual indica que para algunos algoritmos de reemplazo de pginas, la tasa de fallos de pgina, puede

aumentar al incrementarse el nmero de marcos asignados. En las investigaciones realizadas sobre los

distintos algoritmos se observ esta anomala.

ALGORTMO PTIMO.

Como consecuencia del descubrimiento de la anomala de Belady, se busc un algoritmo de

reemplazo de pginas ptimo, con la menor tasa de fallos de pgina, de todos los algoritmos y que

nunca presentar la anomala de Belady.

El algoritmo ptimo, al que se le ha dado el nombre OPT, garantiza la menor tasa de fallos de

pgina posible, para un numero fijo de marcos y consiste en reemplazar la pgina que ms tiempo

tardar en utilizarse.

Supongamos que disponemos de 3 marcos de memoria real y le vamos a aplicar el algoritmo

ptimo, segn la serie anteriormente citada.

7 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 7 0 1

7 7 7

0 0

1

x x x

2

0

1

x

2

0

3

x

2

4

3

x

2

0

3

x

2

0

1

x

7

0

1

x

Se producen 9 fallos de pgina y este ser el tratamiento ptimo para esta serie.

Si se compara con el algoritmo FIFO, que present 15 fallos de pgina, vemos que si

descontamos los tres primeros fallos de pgina, que son comunes en todos los algoritmos, es el doble

mejor, que el algoritmo FIFO, ya que el nmero de fallos de pgina disminuye a la mitad.

Ningn algoritmo de reemplazo, puede procesar esta serie de referencias, con menos de 9 fallos

de pgina, si utilizamos 3 marcos de memoria real, por desgracia, es difcil implantar el algoritmo de