Professional Documents

Culture Documents

CX 4301574577

Uploaded by

Gowtham SpOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CX 4301574577

Uploaded by

Gowtham SpCopyright:

Available Formats

Abhishek Agal et al Int.

Journal of Engineering Research and Applications

ISSN : 2248-9622, Vol. 4, Issue 3( Version 1), March 2014, pp.574-577

RESEARCH ARTICLE

www.ijera.com

OPEN ACCESS

6T SRAM Cell: Design And Analysis

Abhishek Agal*, Pardeep*, Bal Krishan**

* (Electronics Engineering Department, YMCA University of science & technology, Faridabad)

**(A.P., Electronics Engineering Department, YMCA University of science & technology, Faridabad)

ABSTRACT

SRAM has become a major component in many VLSI Chips due to their large storage density and small access

time. SRAM has become the topic of substantial research due to the rapid development for low power, low

voltage memory design during recent years due to increase demand for notebooks, laptops, IC memory cards

and hand held communication devices. SRAMs are widely used for mobile applications as both on chip and offchip memories, because of their ease of use and low standby leakage.

The main objective of this paper is evaluating performance in terms of Power consumption, delay and SNM of

existing 6T CMOS SRAM cell in 45nm and 180nm technology.

Keywords 6T SRAM cell, Power dissipation, Read Delay, SNM, Write Delay.

I. INTRODUCTION

6T static random-access memory is a type of

semiconductor memory that uses bistable latching

circuitry to store each bit. The term static

differentiates it from dynamic RAM which must be

periodically refreshed. SRAM exhibits data

remembrance, but is still volatile in conventional

sense, that data is eventually lost when memory is not

powered.

II. 6T SRAM CELL OPERATION

1.

Standby Mode (the circuit is idle)

In standby mode word line is not asserted

(word line=0), so pass transistors N3 and N4 which

connect 6t cell from bit lines are turned off. It means

that cell cannot be accessed. The two cross coupled

inverters formed by N1-N2 will continue to feed back

each other as long as they are connected to the

supply, and data will hold in the latch.

Read Mode (the data has been requested)

In read mode word line is asserted (word

line=1), Word line enables both the access transistor

which will connect cell from the bit lines. Now

values stored in nodes (node a and b) are transferred

to the bit lines. Assume that 1 is stored at node a so

bit line bar will discharge through the driver

transistor (N1) and the bit line will be pull up through

the Load transistors (P1) toward VDD, a logical 1.

Design of SRAM cell requires read stability (do not

disturb data when reading).

Typically, each of the inverters is designed so that

PMOS and NMOS are matched, thus inverter

threshold is kept at VDD/2. If we wish to write 0 at

node a, N3 operates in saturation. Initially, its source

voltage is 1. Drain terminal of N2 is initially at 1

which is pulled down by N3 because access transistor

N3 is stronger than N1. Now N2 turns on and P1

turns off, thus new value has been written which

forces bit line lowered to 0V and bit bar to VDD.

SRAM to operate in write mode must have writeability which is minimum bit line voltage required to

flip the state of the cell.

2.

3.

Write Mode (updating the contents)

Assume that the cell is originally storing a 1

and we wish to write a 0. To do this, the bit line is

lowered to 0V and bit bar is raised to VDD, and cell

is selected by raising the word line to VDD.

www.ijera.com

FIGURE 1 Schematic of 6t SRAM cell

III. PERFORMANCE PARAMETERS OF

SRAM

SNM: maximum dc voltage that the cell

tolerates before it changes state in read mode. The

size of the maximum square that can be inscribed in

butterfly curve gives the SNM of the SRAM cell.

Instead of measuring the read stability and write

ability separately a method known as N-curve

574 | P a g e

Abhishek Agal et al Int. Journal of Engineering Research and Applications

ISSN : 2248-9622, Vol. 4, Issue 3( Version 1), March 2014, pp.574-577

www.ijera.com

method by which both parameters can be arrived at

simultaneously is used. Hold SNM is the maximum

dc noise that the cell tolerates before it changes state

in the hold mode.

Write delay: It is the delay between the

applications of the word line WL signal and the time

at which the data is actually written.

Read delay: Read delay is the delay

involved in allowing the bit lines to discharge by

about 10% of the peak value or the delay between the

application of the WL signal and the response time of

the sense amplifier.

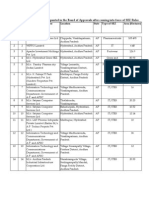

IV. RESULTS AND ANALYSIS

1. 180nm Technology

FIGURE 3 Butterfly curve for hold operation at

180nm technology

FIGURE 4 Butterfly curve for read operation at

180nm technology

FIGURE 2 Transient analysis at 180nm technology

1.

2.

3.

4.

5.

6.

Average power consumed = 1.317488e-004

watts.

Read delay = 4.7168e-010 sec.

Write delay= 9.6081e-010 sec.

Hold SNM=0.5 volt.

Read SNM=0.1 volt.

Write SNM=0.7 volt.

www.ijera.com

FIGURE 5 Butterfly curve for write operation at

180nm technology

575 | P a g e

Abhishek Agal et al Int. Journal of Engineering Research and Applications

ISSN : 2248-9622, Vol. 4, Issue 3( Version 1), March 2014, pp.574-577

www.ijera.com

2. 45nmTchnology:

FIGURE 8 Butterfly curve for read operation at

45nm technology

FIGURE 6 Transient analysis at 45nm technology

1.

2.

3.

4.

5.

6.

Average power consumed = 8.492199e-010

watts.

Read Delay = 4.7222e-010 sec.

Write Delay= 2.1395e-009 sec.

Hold SNM=0.15 volt.

Read SNM=0.05 volt.

Write SNM=0.2 volt.

FIGURE 9 Butterfly curve for write operation at

45nm technology

V. CONCLUSION

Simulation and analyzation of performance

of 6T SRAM cells at 180nm and 45nm technology

for parameters like power consumption, delay and

SNM is as desired. Simulation results shows clearly

how read, write operation is performed.

VI. ACKNOWLEDGEMENTS

FIGURE 7 Butterfly curve for hold operation at

45nm technology

www.ijera.com

For power constrained projects like space

exploration and satellites the SRAM cell which

consumes minimum power should be used while for

very fast processing devices the SRAM cell which

has minimum time delay should be used. The SRAM

cell which has maximum SNM can be used in the

device which works in noisy environment. The

design of SRAM cell can be optimized by tradeoff

between various performance parameters. New

design is not introduced within the project. In future

we will propose new SRAM cell design or schematic,

which decreases read/write delay, consumes less

power.

576 | P a g e

Abhishek Agal et al Int. Journal of Engineering Research and Applications

ISSN : 2248-9622, Vol. 4, Issue 3( Version 1), March 2014, pp.574-577

www.ijera.com

REFERENCES

Journal Papers:

[1]

Ajay Kumar Dadoria, Arjun Singh Yadav,

C.M Roy, Comparative Analysis Of

Variable N-T Sram Cells International

Journal of Advanced Research in Computer

Science and Software Engineering, Volume

3, Issue 4, April 2013.

[2]

Seevinck, F. J. List, J. Lohstroh, StaticNoise Margin Analysis of MOS SRAM

Cells IEEE J. Solid-State Circuits, vol. SC22, pp. 748-754, Oct. 1987.

[3]

Sapna singh, Neha Arora, Meenkshi Suthar,

Neha Gupta, Performance evaluation of

different SRAM cell structures at different

technologies, International Journal of VLSI

design& communication systems (VLSICS)

vol.3, No.1, Februry 2012.

[4]

J. Rabaey, Digital integrated circuits, A

design perspective, prentice hall, upper

saddle river, NJ, 1996.

[5]

Andrei Pavlov, Manoj Sachdev, CMOS

SRAM Circuit Design and parametric test in

nano-scaled technologies, Process Aware

SRAM Design and Test, springer, 2008.

[6]

M. Adiseshaiah, D. sharath Babu Rao, V.

Venkateswara Reddy, Implementation and

Design of 6T SRAM with Read and write

Assist circuits, IJREAS, Volume2, Issue 5

(May 2012), 2249-3905.

[7]

Ravindra kumar, Dr. Gurjit Kaur, A Novel

Approach to design of 6T (8X8) SRAM cell

low power dissipation using MCML

technique on 45NM, International Journal

of Engineering Research and applications

(IJERA), vol.2, Issue 4, July- August 2012,

PP. 093-097

[8]

C.-T. Chuang, S. Mukhopadhyay, J.-J. Kim,

K. Kim, R. Rao, High-performance SRAM

in nanoscale CMOS: Design challenges and

techniques, in IEEE Int. Workshop.,

Memory Technology, Design and Testing,

Taipei, Taiwan, Dec. 3-5, 2007, pp. 4-12.

[9]

H. Yamauchi, A Discussion on SRAM

Circuit Design Trend in Deeper NanometerScale Technologies, IEEE Trans. Very

Large Scale Integr. Syst. vol.18, no.5,

pp.763-774, May 2010.

[10] Arash Azizi-Mazreah, Mohammad T.

Manzuri Shalmani, Hamid Barati and Ali

Barati, Delay and Energy consumption

Analysis of conventional SRAM, World

Academy of Science, Engineering and

Technology no. 37, 2008.

www.ijera.com

577 | P a g e

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Ultimate Guide On BloggingDocument37 pagesUltimate Guide On BloggingHau IuliaNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- How To Fix and Prevent FB14 Fault Drive Loader Version Hint 22 CDocument4 pagesHow To Fix and Prevent FB14 Fault Drive Loader Version Hint 22 CTomek Wołkowiecki100% (6)

- Andrew Burrows Diagram Equipment Code ListDocument149 pagesAndrew Burrows Diagram Equipment Code ListВиктор Сабов100% (1)

- Filing NOTEDDocument57 pagesFiling NOTEDoki mora100% (1)

- Complaint Form CMC FinalDocument4 pagesComplaint Form CMC FinalEugene ChuaNo ratings yet

- Fusion: Combining Distinct Entities into a New WholeDocument3 pagesFusion: Combining Distinct Entities into a New WholeGowtham SpNo ratings yet

- Spanish Language Influences On Written English: Betty Rizzo and Santiago VillafaneDocument10 pagesSpanish Language Influences On Written English: Betty Rizzo and Santiago VillafaneGowtham SpNo ratings yet

- Relative Atomic Mass - WikipediaDocument2 pagesRelative Atomic Mass - WikipediaGowtham SpNo ratings yet

- Very Large Scale IntegrationDocument3 pagesVery Large Scale IntegrationGowtham SpNo ratings yet

- Writing For The Web GuideDocument16 pagesWriting For The Web GuideJuliusNeilPialaNo ratings yet

- Semiconductor fundamentals and applications explainedDocument2 pagesSemiconductor fundamentals and applications explainedGowtham SpNo ratings yet

- 200 Prep Questions: Downloads/200 - PMP - Sample - Questions PDFDocument1 page200 Prep Questions: Downloads/200 - PMP - Sample - Questions PDFGowtham SpNo ratings yet

- Scientific Writing in APA StyleDocument38 pagesScientific Writing in APA StyleelentscheNo ratings yet

- Programming TipsDocument2 pagesProgramming TipsGowtham SpNo ratings yet

- Standard Atomic Weight - WikipediaDocument2 pagesStandard Atomic Weight - WikipediaGowtham SpNo ratings yet

- Chemical Element - WikipediaDocument2 pagesChemical Element - WikipediaGowtham SpNo ratings yet

- Diode - WikipediaDocument3 pagesDiode - WikipediaGowtham SpNo ratings yet

- Capacitor - WikipediaDocument2 pagesCapacitor - WikipediaGowtham SpNo ratings yet

- Lambda-CDM Model - WikipediaDocument2 pagesLambda-CDM Model - WikipediaGowtham SpNo ratings yet

- Big Bang - WikipediaDocument2 pagesBig Bang - WikipediaGowtham SpNo ratings yet

- Planck Time - WikipediaDocument2 pagesPlanck Time - WikipediaGowtham SpNo ratings yet

- Hubble Space Telescope - WikipediaDocument3 pagesHubble Space Telescope - WikipediaGowtham SpNo ratings yet

- Speed of Light - WikipediaDocument3 pagesSpeed of Light - WikipediaGowtham SpNo ratings yet

- SunDocument3 pagesSunGowtham SpNo ratings yet

- Publication Nemani Gowtham PDFDocument6 pagesPublication Nemani Gowtham PDFGowtham SpNo ratings yet

- UranusDocument4 pagesUranusGowtham SpNo ratings yet

- BaggerDocument2 pagesBaggerGowtham SpNo ratings yet

- Pluto - WikipediaDocument4 pagesPluto - WikipediaGowtham SpNo ratings yet

- CurrencyDocument3 pagesCurrencyGowtham SpNo ratings yet

- Comparative Study On Low-Power High-Performance Standard-Cell Flip-FlopsDocument9 pagesComparative Study On Low-Power High-Performance Standard-Cell Flip-FlopsGowtham SpNo ratings yet

- Universe - WikipediaDocument4 pagesUniverse - WikipediaGowtham SpNo ratings yet

- BaggerDocument2 pagesBaggerGowtham SpNo ratings yet

- Reserach Proposal-Radioisotope Thermoelectric Generator Application For LocomotivesDocument4 pagesReserach Proposal-Radioisotope Thermoelectric Generator Application For LocomotivesGowtham SpNo ratings yet

- Recent Trends in Low Power VLSI DesignDocument15 pagesRecent Trends in Low Power VLSI DesignGowtham SpNo ratings yet

- Device Lab Report 10 PDFDocument6 pagesDevice Lab Report 10 PDFScribble RiYaDNo ratings yet

- UK FireClass FC501 Data SheetDocument2 pagesUK FireClass FC501 Data SheetSanda Raluca-NicoletaNo ratings yet

- Secure and Fast Online File Sharing Script (V2.1.3) - Vcgsoft Freeware TeamDocument4 pagesSecure and Fast Online File Sharing Script (V2.1.3) - Vcgsoft Freeware TeamVickyMalhotraNo ratings yet

- 1769 In028j en P (PB4 PB2) PDFDocument16 pages1769 In028j en P (PB4 PB2) PDFfaisalNo ratings yet

- ZSU2 Quick Guide Telesoft, Grabador de Llamadas Telefonicas TelesoftDocument5 pagesZSU2 Quick Guide Telesoft, Grabador de Llamadas Telefonicas TelesoftGlennNo ratings yet

- Anson Ortigas FPS Sell-Out Report Week 2 JuneDocument30 pagesAnson Ortigas FPS Sell-Out Report Week 2 JuneRevssor PeraltaNo ratings yet

- Heraclitus On NatureDocument151 pagesHeraclitus On NatureGonçaloBargadoNo ratings yet

- New Product Developmen1Document5 pagesNew Product Developmen1srvjeetNo ratings yet

- 7UT613 63x Manual PIXIT A2 V046101 en PDFDocument130 pages7UT613 63x Manual PIXIT A2 V046101 en PDFMJNo ratings yet

- PTO's : Questionnaire For New Parts ListDocument1 pagePTO's : Questionnaire For New Parts ListAbhishek kumarNo ratings yet

- OCIO - DBHIDS Data Governance Framework Implementation Plan v1Document62 pagesOCIO - DBHIDS Data Governance Framework Implementation Plan v1Jonatan Loaiza VegaNo ratings yet

- CHAPTER 7 ControllingDocument3 pagesCHAPTER 7 ControllingsyahswiftNo ratings yet

- E AadharDocument1 pageE AadharPranita RathodNo ratings yet

- Introduction To Shell and Tube Heat Exchangers - Part01Document24 pagesIntroduction To Shell and Tube Heat Exchangers - Part01SergioRinconSolanoNo ratings yet

- BORUDocument1 pageBORUAshesh MistryNo ratings yet

- Civil Engineering BooksDocument9 pagesCivil Engineering BooksElvi Papaj0% (1)

- ADC V NotesDocument110 pagesADC V Noteskrishnakk100No ratings yet

- BASDocument178 pagesBASclayjr70No ratings yet

- Lab Manual 8 1Document6 pagesLab Manual 8 1sureshgurujiNo ratings yet

- Joint Venture ReportDocument15 pagesJoint Venture ReportRavi MalhotraNo ratings yet

- DFN Mitteilungen 84 PDFDocument54 pagesDFN Mitteilungen 84 PDFzasdfNo ratings yet

- Honda CBF150 parts catalogue introduces new colorsDocument19 pagesHonda CBF150 parts catalogue introduces new colorsalexander ortizNo ratings yet

- List of Formal Approval SEZDocument34 pagesList of Formal Approval SEZsampuran.das@gmail.comNo ratings yet

- ZOOMLION QY25V Truck Crane Technical SpecificationsDocument15 pagesZOOMLION QY25V Truck Crane Technical SpecificationsLi ZhangNo ratings yet

- Workplace Correspondence Final VersionDocument3 pagesWorkplace Correspondence Final Versionapi-709914177No ratings yet

- HYS0631 - C1L2P0 - Brochure Update Sept16 - Hyster J1.5-3.5GXDocument12 pagesHYS0631 - C1L2P0 - Brochure Update Sept16 - Hyster J1.5-3.5GXMickNo ratings yet