Professional Documents

Culture Documents

Aec Manual Vin

Uploaded by

Akash BhagatOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Aec Manual Vin

Uploaded by

Akash BhagatCopyright:

Available Formats

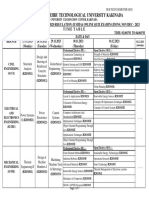

Analog Electronics Circuits Lab Manual

III Semester ECE

ANALOG

ELECTONICS LAB

MANUAL

SUBJECT CODE:

10ESL37

STAFF INCHARGE:

Prof. Akashkumar. Bhagat

Prof. Mahesh. Mahendrakar

Prof.Pooja. Shanbhag

Prof.Saritha. M

Prof. Rajadheep. Dhar

Prof. Vinay Sangolli

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

Prepared By: Prof. Vinay Sangolli

CONTENTS

SI.NO

EXPERIMENTS

RC-Coupled Amplifier

Darlington Emitter Follower

Voltage Series Feedback Amplifier

R.C. Phase Shift Oscillator

Hartley and Colpitts Oscillator

Crystal Oscillator

Diode Cliping Circuits

Diode Clamping Circuits

Class B Push-Pull Amplifier

10

Rectifier Circuits

11

Verification of Thevinins Theorem and

Maximum Power Transfer theorem

12

Series & Parallel Resonance Circuits

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

PAGE NO

Analog Electronics Circuits Lab Manual

III Semester ECE

EXPERIMENT NO 1

RC COUPLED AMPLIFIER

AIM: To design and wire a RC Coupled single stage BJT amplifier and determination of the gain

frequency response, input and output impedances.

COMPONENT REQUIRED:

Sno

1

2

3

4

5

6

Component

Transistor

Capacitor

Resistor

Signal Generator

CRO

Decade Resistance Box

Quantity

1

3

5

1

1

1

Connecting wires

Specification

BJT SL100

1F, 0.47F

10k (2), 1k, 84.3k - DRB

-

CIRCUIT DIAGRAM:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

INPUT IMPEDENCE:

OUTPUT IMPEDENCE

DESIGN:

Specifications:

Operating points (IC=1mA, VCE= 5V)

Stability=10

Voltage Gain Av=10

FL=500Hz

Device :

SL100 (Si npn transistor)

VBE= 0.7V

=100

1/hoe = 100k

To find RE :

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

IE=IC+ IC / = 1mA+1/100 mA= 1.01mA

RE = VE / IE =1V / 1.01 mA =990

Let RE = 1k ( standard)

To find RC :

Av = Rc / RE

10=Rc / 1 k

Rc= 10 k

To Find VCC

From the collector loop writing KVL we get VCC = ICRC + VCE + VE

Vcc= (1mA*10 k )+5V+(1mA*1 k )

= 16 V

To find Rb1 and Rb2:

S= Rb2 / RE

10= Rb2/1.01mA

Rb2=10 k

Writing the base loop KVL we get VB = VE + VBE = 1 + 0.7

VB = 1.7V

Now VB = (Rb2 / Rb1 +Rb2) *Vcc

1.7 = (10 k/ Rb1+ 10 k )*16

= 84.3 k

To Find Input Impedance:

Zin = Rb1 || Rb2 || hie

hie= * re

re= 26mV/ IE

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

Zin= 1.95 k

To Find Output Impedance:

Zo = Rc || (1/ hoe) = 10 k|| 100 k =10 k

To find CCi , CCo :

Xcci= 0.1*Zin

FL=500Hz

CCi =1.63F = 1F (Standard)

Xcco= 0.1*Zo

FL=500Hz

CCo =0.35F = 0.47F (Standard)

Xce= 0.1*RE

FL=500Hz

CCe =3.18 (DCB)

Voltage Gain Av= -hfe*Rc / hie

= -400

OBSERVATION:

Table 1 : DC Conditions Input and Output Impedence

Parameter

VCE

Vcc

Theoretical

Practical

Table 2 : Input and Output Impedence

Parameter

Zi

Zo

Theoretical

Practical

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Ic

Analog Electronics Circuits Lab Manual

Table 3: Frequency response: Vin =

F hz

Vo(p-p)

III Semester ECE

Volts

AV = Vo(p-p) / Vin(p-p).

AV in db = 20*log AV

100

200

300

500

1k

3k

5k

15k

20k

25k

30k

50k

100k

200k

300k

400k

500k

700k

900k

1M

Theory:

The common emitter RC coupled amplifier is one of the simplest and elementary transistor

amplifier that can be made. Dont expect much boom from this little circuit, the main purpose of

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

this circuit is pre-amplification i.e to make weak signals strong enough for further processing or

amplification. If designed properly, this amplifier can provide excellent signal characteristics.

Input Capacitor Cin is the input DC decoupling capacitor which blocks any DC component if

present in the input signal from reaching the Q1 base. If any external DC voltage reaches the

base of Q1, it will alter the biasing conditions and affects the performance of the amplifier.

The resistors R1 and R2 are the biasing resistors. This network provides the transistor Q1s base

with the necessary bias voltage to drive it into the active region. The region of operation where

the transistor is completely switched of is called cut-off region and the region of operation where

the transistor is completely switched ON (like a closed switch) is called saturation region. The

region in between cut-off and saturation is called active region. For a transistor amplifier to

function properly, it should operate in the active region. Let us consider this simple situation

where there is no biasing for the transistor. As we all know, a silicon transistor requires 0.7 volts

for switch ON and surely this 0.7 V will be taken from the input audio signal by the transistor. So

all parts of there input wave form with amplitude 0.7V will be absent in the output waveform.

In the other hand if the transistor is given with a heavy bias at the base ,it will enter into

saturation (fully ON) and behaves like a closed switch so that any further change in the base

current due to the input audio signal will not cause any change in the output. The voltage across

collector and emitter will be 0.2V at this condition (Vce sat = 0.2V). That is why proper biasing

is required for the proper operation of a transistor amplifier.

Procedure:

a.

To plot Frequency response :

1. Connections are made as per the given circuit diagram.

2. Switch on the D.C. power supply and check the D.C. conditions without any input

signal and record in table 1.

3. Select sine wave input and set the input signal frequency at 10kHz constant, and

observe the input wave and output wave on the CRO and adjust the input amplitude

such that the output is undistorted waveform. Calculate midband gain using AV =

Vo(p-p) / Vin(p-p).

4. Keeping the input amplitude constant, vary the frequency from 50hz to 1Mhz and

5. note down the corresponding output voltage(p-p) in the table 2.

6. Calculate gain in db and plot the frequency response curve and find the bandwidth.

b.

To find input impedance Zin:

1.Connect DRB in series with the input signal and set it to ZERO.

2. Set the signal frequency to 10kHz and measure the output voltage(p-p).

3. Vary the DRB from 0 to maximum such that the output signal voltage reduces to half

its value. This value of DRB at which the output signal reduces to half its value if the

input impedance Zin.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

c.

III Semester ECE

To find output impedance Zo:

1.Connect DRB in parallel with the output and set it to MAXIMUM.

2. Set the signal frequency to 10kHz and measure the output voltage(p-p).

3. Vary the DRB from maximum to minimum such that the output signal voltage reduces

to half its value. This value of DRB at which the output signal reduces to half its value if

the output impedance Zo.

EXPECTEDGRAPH:

Av in db

3db

B W

f1

Frequency

f2

Bandwidth = f2 - f1

RESULT:

EXPERIMENT NO 2

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

DARLINGTON EMITTER FOLLOWER

AIM: To design a Darlington Emitter Follower and determine the gain and input, output

impedance.

COMPONENTS REQUIRED:

SN

O

1

2

3

4

5

Components Name

Quantity

Transistor

Resistors

Capacitors

Connecting wires

Function Generator

2

3

1

1

SL100

50k , 33k , 1k

0.15F , 258F

-

6

7

8

9

Bread Board

Dc Ammeter

Dc Voltmeter

DRB

1

1

1

1

mA

-

CIRCUIT DIAGRAM:

DESIGN:

IC = 3mA , VCE = 8V , Zin = 20k , hie = 1.2 k

1. Assume ( for both transistors) = 100

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

Analog Electronics Circuits Lab Manual

III Semester ECE

VE

VE = 3V ,RE = I E but IE =IC

RE = 1 k

2. VCC= VCE +VE= 11V

3. VB= VE +VBE= 4.4 V but VB= VCC

R2

R1 + R2

= 1.5 R2

4. Zin = R1 R2 2 RE

Let = R1 R2 = R

Zin = R 2 RE

R = 20.04k

5. Input Coupling Capacitance

XCci = 0.1 Zin at lowest frequency of interest

fL = 500 Hz Cci = 0.15 F 0.1F

6. Output Impedance

Zo = [ {Rs RB+ hie }/ hfe ] RE

= 12.34

7. Output Coupling Capacitance Cco

XCo = 0.1 Zo at lowest frequency of interest

fL = 500 Hz Cco= 258F 100F parallel to 100F

OBSERVATIONS:

1. DC Conditions:

Vcc

Ic

VCE

Theoretical

Practical

2. Input and output Impedance :

Zin

Zo

Theoretical

Practical

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

3. Frequency Response: [For vi=--------]

Frequency

(Hz)

Vo

(volts)

Gain in dB

= 20 log (vo/vi)

THEORY :

A very popular connection of two BJTs for operation as one super beta transistor is the

Darlington connection. The main feature of Darlington connection is that the composite

transistor acts, as a single unit with a current gain is equal to product of individual current gains.

i.e. D = 1x2 if 1= 2 = Then D = 2

To make the two transistors Darlington pair, the emitter terminal of the first transistor is

connected to the base of the second transistor and the collector terminals of the two transistors

are connected together. The result is that emitter current of the first transistor is the base current

of the second transistor. The biasing analysis is similar to that for single transistor except that two

VBE drops are to be considered. In a circuit if the output voltage is approximately equal to the

input voltage, such a circuit is known as emitter follower. In the transistor emitter follower

circuit the output is taken from the emitter terminal. The voltage gain is approximately equal to

unity and output voltage is in phase with the input voltage. The emitter follower configuration is

frequently used for impedance matching and to increase the current gain. Sometimes the current

gain and input impedance of emitter followers are insufficient to meet the requirement. In order

to increase the overall values of circuit current gain (Ai) and input impedance, two transistors are

connected in series in emitter follower configuration to obtain Darlington connection.

PROCEDURE :

1. Connections are made as per the circuit diagram.

2. The supply voltages of 11V and the input peak to peak voltage kept at 0.1V at 1KHz

frequency from signal generator is applied to the circuit

3. The frequency of the input is varied from 50Hz to 2MHz and output voltage Vo is noted

down.

4. Gain is calculated in dB and a graph of frequency versus gain in dB is plotted on semilog

sheet.

5. DC Conditions and input impedance and output impedance are also noted down.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

EXPECTED GRAPH:

RESULT:

EXPERIMENT NO 3

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

VOLTAGE SERIES FEEDBACK AMPLIFIER

AIM: Design of a FET Voltage series feedback amplifier and determine the gain, frequency

response, input and output impedances with and without feedback.

COMPONENTS REQUIRED:

SN

O

1

2

Components Name

Quantity

FET

Resistors

1

3

3

4

5

6

Capacitors

Connecting wires

Bread Board

DC power supply

2

1

1

CIRCUIT DIAGRAM:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

BFW10

1.5k , 1k, 2M, 165K,

68K

0.01F , 0.47F

-

Analog Electronics Circuits Lab Manual

DESIGN:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

THEORY :

Amplifiers use current or voltage as input and output, so four types of amplifier are possible. The

four basic types of amplifiers are as follows:

Voltage amplifier This is the most common type of amplifier. An input voltage is amplified to a

larger output voltage. The amplifier's input impedance is high and theoutput impedance is low.

Current amplifier This amplifier changes an input current to a larger output current. The

amplifier's input impedance is low and the output impedance is high.

Transconductance amplifier This amplifier responds to a changing input voltage by delivering

related changing output current. Transresistance amplifier This amplifier responds to a

changing input current by delivering a related changing output voltage. Other names for the

device

are

transimpedance

amplifier

and current-to-voltage

converter.

Any of these four choices may be the open-loop amplifier used to construct the feedback

amplifier. The objective for the feedback amplifier also may be any one of the four types of

amplifier, not necessarily the same type as the open-loop amplifier. For example, an op amp

(voltage amplifier) can be arranged to make a current amplifier instead. The conversion from one

type to another is implemented using different feedback connections, usually referred to as series

or shunt (parallel) connections.

PROCUDURE :

Rig up the circuit as shown in the circuit diagram.

1. Check Q conditions i.e,. measure VDS and VGS.

2. Set Vi = 1V or 2V at 10 KHz on Audio signal Generator and measure gain AV without

feedback.

3. Disconnect short of Green and Black terminal of signal generator to avoid grounding

problem or isolate ground of signal generator.

4. Measure VO with feedback & find AVf the gain with feedback. Note AVf is less than AV

5. To plot freq response, note output voltage with and without feedback from 100Hz to

10MHz

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

EXPECTED GRAPH:

RESULT:

FET Voltage series feedback amplifier is designed and the frequency response, input and output

impedence, gain with and without feedback are determined .

EXPERIMENT NO 4

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

RC PHASE SHIFT OSCILLATOR

AIM: To design and study the working of an RC Phase Shift oscillator using BJT.

COMPONENT REQUIRED:

Sno

1

2

3

4

5

6

Component

Transistor

Capacitor

Resistor

Signal Generator

CRO

Decade Resistance Box

Quantity

1

4

4

1

1

1

Connecting wires

Specification

BJT BC107

0.01F (3), 0.47 F

22k , 1k, 6.8k, 470 - DRB, 3.9k

-

CIRCUIT DIAGRAM:

Calculations:

Theoretical Frequency Calculations

f = 1 / (2**R*C*sqrt(6+4K)) where K= Rc / R

let

R= 3.9k and C = 0.01F

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

Rc = 10 k

f = 1 / (2**3.9 k *0.01 F *sqrt(6+4(1/3.9)))

=1.539 khz (approx)

Observed Frequency

T =-----f=1/T

OBSERVATION:

Theoretical

Frequency ft (Hz)

Practical

Frequency fp(Hz)

Error = (ft - fp) / ft * 100

Theory:

RC phase shift oscillator or simply RC oscillator is a type of oscillator where a simple RC

network (resistor-capacitor) network is used for giving the required phase shift to the feedback

signal. In LC oscillators like Hartley oscillator and Colpitts oscillator an LC network (inductorcapacitor network) is used for providing the necessary positive feedback. The main feature of an

RC phase shift oscillator is the excellent frequency stability. The RC oscillator can output a pure

sine wave on a wide range of loads.

RC phase shift network is a simple resistor capacitor network that can be used to give a desired

phase shift to a signal. The circuit diagram of a simple single stage RC network is shown in the

figure below.

Therotically in a simple RC circuit, the output voltage will lead the input voltage by a phase

angle =90. Anyway in practical case the phase angle will be something below 90 just

because it is impossible to get a purely ideal capacitor. Phase shift of a practical RC network

depends on the value of the capacitor, resistor and the operating frequency. Let F be the operating

frequency, R be the resistance and C be the capacitance. Then the capacitive reactance Xc to the

frequency F can be given by the equation Xc = 1 / (2FC).The effective impedance of the circuit

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

can be given by the equation Z = ( R + Xc). The phase angle of the RC network can be

derived as = tan-1 (Xc/R). Just by making an RC network with phase shift equal to 60 and

cascading three of them together the desired phase shift of 180 can be attained. This 180 phase

shift by the RC network plus the 180 phase shift made by the transistor gives a total phase shift

of 360 between the input and output which is the necessary condition for maintaining sustained

oscillations.

Procedure:

1.

2.

3.

4.

Test the components.

Connections are made as per the given circuit diagram.

Adjust the dc source to proper value.

The dc input is given to the circuit and the output frequency is noted and compared

with the desired frequency

EXPECTED GRAPH:

RESULT:

EXPERIMENT NO 5

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

FET HARTLEY AND COLPITTS OSCILLATOR

AIM: To design Hartley and colpitts oscillator for given frequency using FET

COMPONENTS REQUIRED:

SN

O

1

2

3

4

5

Components Name

Quantity

FET

Resistors

Capacitors

Connecting wires

Signal Generator

1

5

4

1

BFW11

1.5k,1k(2), 82 k, 1M

0.1F(2), 47 F, 330pF

-

6

7

8

Bread Board

DC power supply

CRO

1

1

1

HARTLEY OSCILLATOR:

CIRCUIT DIAGRAM:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

Analog Electronics Circuits Lab Manual

DESIGN:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

COLPITTS OSCILLATOR:

CIRCUIT DIAGRAM:

DESIGN:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

THEORY:

Hartley oscillator:

The Hartley oscillator is an electronic oscillator circuit in which the oscillation frequency is

determined by a tuned circuit consisting of capacitors and inductors, that is, an LC oscillator. The

circuit was invented in 1915 by American engineer Ralph Hartley. The distinguishing feature of

the Hartley oscillator is that the tuned circuit consists of a single capacitor in parallel with two

inductors in series (or a single tapped inductor), and the feedback signal needed for oscillation is

taken from the center connection of the two inductors

The Hartley oscillator is distinguished by a tank circuit consisting of two seriesconnected coils (or, often, a tapped coil) in parallel with a capacitor, with an amplifier between

the relatively High impedance across the entire LC tank and the relatively low voltage/high

current point between the coils. The original 1915 version used a triode as the amplifying device

in Common plate (cathode follower) configuration, with three batteries, and separate adjustable

coils. The most simple of implementations shown here uses nothing but aJFET (in Commondrain configuration) and the LC tank circuit (here the single winding is tapped), plus a single

battery; it will work, but probably with high distortion and high current drain (that could be

improved by adding resistance between the source and the coil tap), and serves as an

uncomplicated illustration of the Hartley oscillator operation:

the output from the JFET's source (emitter, if a BJT had been used; cathode for a triode)

has the same phase as the signal at its gate (or base) - and roughly the same voltage as its

input (which is the voltage across the entire tank circuit), but the current is amplified, i.e. it is

acting as a current buffer or voltage-controlled voltage-source.

this low impedance output is then fed into the coil tapping, effectively into

an autotransformer that will step up the voltage, requiring a relatively high current

(compared with that available at the top of the coil).

With the capacitor-coil resonance, all frequencies other than the tuned frequency will

tend to be absorbed (the tank will appear as nearly zero ohms near DC due to the inductor's

low reactance at low frequencies, and low again at very high frequencies due to the

capacitor); they will also shift the phase of the feedback from the zero degrees needed for

oscillation at all but the tuned frequency.

Colpitts oscillator: The Colpitts circuit, like other LC oscillators, consists of a gain device (such

as a bipolar junction transistor, field effect transistor, operational amplifier, or vacuum tube) with

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

its output connected to its input in a feedback loop containing a parallel LC circuit (tuned circuit)

which functions as a bandpass filter to set the frequency of oscillation.

A Colpitts oscillator is the electrical dual of a Hartley oscillator, where the feedback signal is

taken from an "inductive" voltage divider consisting of two coils in series (or a tapped coil). Fig.

1 shows the common-base Colpitts circuit. L and the series combination of C1 and C2 form the

parallel resonant tank circuit which determines the frequency of the oscillator. The voltage

across C2 is applied to the base-emitter junction of the transistor, as feedback to create

oscillations. Fig. 2 shows the common-collector version. Here the voltage across C1 provides

feedback. The frequency of oscillation is approximately the resonant frequency of the LC circuit,

which is the series combination of the two capacitors in parallel with the inductor

PROCUDURE:

1. Make the connections as shown in circuit diagram.

2. Observe the sinusoidal output voltage.

3. Measure the frequency and compare with the theoretical values.

EXPECTED GRAPH:

RESULT: Diode clipping circuits for peak clipping and peak detection is verified.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

EXPERIMENT NO 6

CRYSTAL OSCILLATOR

AIM: To test the performance of BJT-Crystal Oscillator for frequency f0 >100kHz

COMPONENTS REQUIRED:

SN

O

1

2

3

4

5

Components Name

Quantity

Transistor

Resistors

Capacitors

Connecting wires

Crystal

1

3

2

1

SL100

10k(2) , 1k

1F , 0.47F

-

6

7

8

9

Bread Board

DCB

DC power supply

DRB

1

3

1

1

CIRCUIT DIAGRAM:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

Analog Electronics Circuits Lab Manual

III Semester ECE

CALCULATIONS:

T = ---------

f=

1

T

= --------------

THEORY :

One of the most important features of any oscillator is its frequency stability, or in other words

its ability to provide a constant frequency output under varying load conditions. Some of the

factors that affect the frequency stability of an oscillator generally include: variations in

temperature, variations in the load as well as changes to its DC power supply voltage to name a

few. Frequency stability of the output signal can be improved by the proper selection of the

components used for the resonant feedback circuit including the amplifier but there is a limit to

the stability that can be obtained from normal LC and RC tank circuits. To obtain a very high

level of oscillator stability a Quartz Crystal is generally used as the frequency determining device

to produce another types of oscillator circuit known generally as a Quartz Crystal Oscillator,

(XO). The quartz crystal used in a Quartz Crystal Oscillator is a very small, thin piece or wafer

of cut quartz with the two parallel surfaces metallised to make the required electrical

connections. The physical size and thickness of a piece of quartz crystal is tightly controlled

since it affects the final or fundamental frequency of oscillations. The fundamental frequency is

called the crystals characteristic frequency.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

Quartz Crystal Equivalent Model

The equivalent circuit for the quartz crystal shows an RLC series circuit, which represents the

mechanical vibrations of the crystal, in parallel with a capacitance, Cp which represents the

electrical connections to the crystal. Quartz crystal oscillators operate at parallel resonance,

and the equivalent impedance of the crystal has a series resonance where Cs resonates with

inductance, L and a parallel resonance where L resonates with the series combination

of Cs and Cp as shown.

PROCEDURE:

1.

2.

3.

4.

Connections are made as per the circuit diagram.

The dc voltage of 16V is applied to the circuit.

Observe the output waveform and note the frequency of the waveform.

The frequency of output waveform is compared with the frequency of crystal( both

should match).

EXPECTED GRAPH:

RESULT:

Frequency Theoretical: 2MHz

Practical:-----------------

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

EXPERIMENT NO 7

DIODE CLIPPING CIRCUITS

AIM: To study the diode clipping circuits for peak clipping and peak detection

COMPONENTS REQUIRED:

SN

O

1

2

3

4

Components Name

Quantity

Specification

Diode

Resistors

Connecting wires

Signal Generator

1

1

1

IN4007

10k

-

5

6

7

Bread Board

DC power supply

CRO

1

1

1

CIRCUIT DIAGRAM:

1. Negative Series Clipper with Positive Reference Voltage.Tabular Column

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

Vin

Vref

Vo

Vin Vref

Vo

2. Negative Series Clipper with Negative Reference Voltage.

3. Positive Series Clipper with Positive Reference Voltage.

Vin

4. Positive Series Clipper with Negative Reference Voltage.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Vref

Vo

Analog Electronics Circuits Lab Manual

III Semester ECE

Vin

Vref

Vo

Vin

Vref

Vo

Vin

Vref

Vo

5. Negative Parallel Clipper with Positive Reference Voltage.

6. Negative Parallel Clipper with Negative Reference Voltage.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

7. Positive Parallel Clipper with Positive Reference Voltage.

Vin

Vref

Vo

Vin

Vref

Vo

8. Positive Parallel Clipper with Negative Reference Voltage

9. Clipping at Two Independent levels.

Vin

10. Clipping at Two Independent levels ( Slicer).

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Vref1 Vref2 Vo

Analog Electronics Circuits Lab Manual

III Semester ECE

Vin

Vref1

Vref2

Vo

THEORY:

The Diode Clipper, also known as a Diode Limiter, is a wave shaping circuit that takes an input

waveform and clips or cuts off its top half, bottom half or both halves together to produce an

output waveform that resembles a flattened version of the input. For example, the half-wave

rectifier is a clipper circuit, since all voltages below zero are eliminated.

But Diode Clipping Circuits can be used a variety of applications to modify an input

waveform using signal and Schottky diodes or to provide over-voltage protection using Zener

Diodes to ensure that the output voltage never exceeds a certain level protecting the circuit from

high voltage spikes. Then diode clipping circuits can be used in voltage limiting applications.

PROCUDURE :

1. Connections are made as per the circuit diagram.

2. The input voltages of 8V peak to peak at 2kHz is applied from the signal generator to the

circuit.

3. For the given input, Vref is varied and the clipped waveform i.e output waveform can be

observed on the CRO screen and amplitude of Vo is noted down in the tabular column.

4. Keep the CRO in the dual mode, connect the input Vin to Channel 1 of CRO and output

waveform is connected to Channel 2 of CRO, now keep CRO in X-Y mode and observe

the transfer characteristics.

EXPECTED GRAPH:

Vin

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

1. Negative Series Clipper with Positive Reference Voltage.

2. Negative Series Clipper with Negative Reference Voltage.

3. Positive Series Clipper with Positive Reference Voltage.

4. Positive Series Clipper with Negative Reference Voltage.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

5. Negative Parallel Clipper with Positive Reference Voltage.

6. Negative Parallel Clipper with Negative Reference Voltage.

7. Positive Parallel Clipper with Positive Reference Voltage.

8. Positive Parallel Clipper with Negative Reference Voltage

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

9. Clipping at Two Independent levels.

10. Clipping at Two Independent levels ( Slicer).

RESULT: Diode clipping circuits for peak clipping and peak detection is verified.

EXPERIMENT NO 8

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

CLAMPER CIRCUITS

AIM: To study the diode clamping circuits for positive and negative clamping.

COMPONENTS REQUIRED:

SN

O

1

2

3

4

5

Components Name

Quantity

Specification

Diode

Resistors

Capacitor

Connecting wires

Signal Generator

1

1

1

1

IN4007

100k

0.1F

-

6

7

8

Bread Board

DC power supply

CRO

1

1

1

CIRCUIT DIAGRAM:

1. Negative Clamper with Positive Reference Voltage.

Tabular Column

Vin

0. 1F

I N4007

Vin

8vp- p

2KHz

Vref

Vo

R1

100k

CRO

2

0

Vre f

2. Negative Clamper with Negative Reference Voltage.

C

Vin

0. 1F

I N4007

Vin

8vp- p

2KHz

R1

100k

CRO

Vref

0

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Vref

Vo

Analog Electronics Circuits Lab Manual

III Semester ECE

3. Positive Clamper with Positive Reference Voltage.

C

Vin

Vref

Vo

Vin

Vref

Vo

0. 1F

D

I N4007

Vin

8vp- p

2KHz

R

100k

CRO

Vref

0

4. Positive Clamper with Negative Reference Voltage.

C

1

0. 1F

I N4007

Vin

8vp- p

2KHz

R1

100k

CRO

Vr ef

0

THEORY:

A clamping circuit is used to place either the positive or negative peak of a signal at a desired

level. The dc component is simply added or subtracted to/from the input signal. The clamper is

also referred to as an IC restorer and ac signal level shifter.

In some cases, like a TV receiver, when the signal passes through the capacitive coupling

network, it loses its dc component. This is when the clamper circuit is used so as to re-establish

the the dc component into the signal input. Though the dc component that is lost in transmission

is not the same as that introduced through a clamping circuit, the necessity to establish the

extremity of the positive or negative signal excursion at some reference level is important. A

clamp circuit adds the positive or negative dc component to the input signal so as to push it either

on the positive side or on the negative side. The circuit will be called a positive clamper , when

the signal is pushed upward by the circuit. The circuit will be called a negative clamper, when

the signal is pushed downward by the circuit.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

The important points regarding clamping circuits are:

(i) The shape of the waveform will be the same, but its level is shifted either upward or

downward,

(ii) There will be no change in the peak-to-peak or rms value of the waveform due to the

clamping circuit. Thus, the input waveform and output waveform will have the same peak-topeak value that is, 2Vmax. This is shown in the figure above. It must also be noted that same

readings will be obtained in the ac voltmeter for the input voltage and the clamped output

voltage.

(iii) There will be a change in the peak and average values of the waveform. In the figure shown

above, the input waveform has a peak value of V max and average value over a complete cycle is

zero. The clamped output varies from 2 Vmax and 0 (or 0 and -2Vmax). Thus ths peak value of the

clamped output is 2Vmax and average value is Vmax.

(iv) The values of the resistor R and capacitor C affect the waveform.

(v) The values for the resistor R and capacitor C should be determined from the time constant

equation of the circuit, t = RC. The values must be large enough to make sure that the voltage

across the capacitor C does not change significantly during the time interval the diode is nonconducting. In a good clamper circuit, the circuit time constant t = RC should be at least ten

times the time period of the input signal voltage.

PROCEDURE:

1. Connections are made as per the circuit diagram.

2. The input voltages of 8V peak to peak at 2kHz is applied from the signal generator to the

circuit.

3. For the given input, Vref is varied and the clamped waveform i.e output waveform can be

observed on the CRO screen and clamped level is noted down in the tabular column.

4. Keep the CRO in the dual mode, connect the input Vin to Channel 1 of CRO and output

waveform is connected to Channel 2 of CRO

EXPECTED GRAPH

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

1. Positive Clamper with Negative Reference Voltage.

2. Positive Clamper with Positive Reference Voltage.

3. Negative Clamper with Ngaive Reference Voltage.

4. Negative Clamper with Positive Reference Voltage.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

RESULT: Diode clamping circuits for positive and negative clamping are verified.

EXPERIMENT NO 9

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

CLASS B PUSH PULL POWER AMPLIFIER

AIM: Testing of a transformer less class B push pull power amplifier and determination of its

conversion efficiency

COMPONENTS REQUIRED:

SN

O

1

2

3

4

5

Components Name

Quantity

Transistor

Resistors

Capacitors

Connecting wires

Function Generator

2

1

1

1

SL100,CK100

1k

1F

-

6

7

Bread Board

Dc Ammeter

1

1

mA

CIRCUIT DIAGRAM:

CALUCULATIONS:

Collector current IC = ----DC Current Idc = 2Ic

= ------Output Voltage Vo(p-p) =

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

Analog Electronics Circuits Lab Manual

III Semester ECE

RL =

Vcc = 8V

Pi(dc) =Vcc Idc

= -------Po(ac) =

Vo ( p p)

8 RL

= ---------- =

Po( ac)

Pi (dc)

100

= ------------THEORY:

One of the main disadvantages of the Class B amplifier circuit above is that it uses balanced

center-tapped transformers in its design, making it expensive to construct. However, there is

another type of Class B amplifier called a Complementary-Symmetry Class B Amplifier that

does not use transformers in its design therefore, it is transformerless using instead

complementary or matching pairs of power transistors. As transformers are not needed this

makes the amplifier circuit much smaller for the same amount of output, also there are no stray

magnetic effects or transformer distortion to effect the quality of the output signal. The main

disadvantage of class B type push-pull amplifiers is that they suffer from an effect known

commonly as Crossover Distortion. A simple way to eliminate crossover distortion in a Class B

amplifier is to add two small voltage sources to the circuit to bias both the transistors at a point

slightly above their cut-off point. This then would give us what is commonly called an Class AB

Amplifier circuit. However, it is impractical to add additional voltage sources to the amplifier

circuit so PN-junctions are used to provide the additional bias in the form of silicon diodes.

PROCUDURE:

1. Connections are made as per the circuit diagram.

2. The supply voltages are kept at 8V and the input peak to peak voltage kept at 15V in

CRO.

3. The resulting Idc is noted from ammeter.

4. The output Vo(p-p) is raised to match input and resulting power are calculated and also

efficiency.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

EXPECTED GRAPH:

RESULT:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

EXPERIMENT NO 10

RECTIFIERS

AIM: To test the half wave, full wave rectifiers with and without filter and determining the ripple

factor, regulation and efficiency.

COMPONENTS REQUIRED:

SN

O

1

2

3

3

4

5

6

7

Components Name

Resistors

Connecting wires

Capacitor

Bread Board

Dc Ammeter

Diode

Transformer

Multimeter

Quantity

1

1

1

1

1

1

1

CIRCUIT DIAGRAM:

1.A) Half Wave Rectifier Without Filter

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

10k

100

mA

IN4007

-

Analog Electronics Circuits Lab Manual

III Semester ECE

1.B) Half Wave Rectifier with filter

TABULATION COLOUMN:

Vsrms

(in volts)

Idc

VdcFL

Isrms

Vrrms

(in mA)

(in V)

(in mA)

(in volts)

Without

filter

With filter

CIRCUIT DIAGRAM:

2.A )FULL WAVE RECTIFIER WITHOUT FILTER:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Ripple

Factor

Efficienc

y

Voltage

Regulatio

n

Analog Electronics Circuits Lab Manual

III Semester ECE

2.B )FULL WAVE RECTIFIER WITH FILTER:

TABULA

TION COLOUMN:

Vsrms

(in volts)

Idc

VdcFL

Isrms

Vrrms

(in mA)

(in V)

(in mA)

(in volts)

Ripple

Factor

Withoutfilt

er

With filter

CIRCUIT DIAGRAM:

3.A) FULL WAVE BRIDGE RECTIFIER WITHOUT FILTER:

3.B) FULL WAVE BRIDGE RECTIFIER WITH FILTER:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Efficienc

y

Voltage

Regulatio

n

Analog Electronics Circuits Lab Manual

III Semester ECE

TABULATION COLOUMN:

Vsrms

(in volts)

Idc

VdcFL

Isrms

Vrrms

(in mA)

(in V)

(in mA)

(in volts)

Ripple

Factor

Efficienc

y

Voltage

Regulation

Without

filter

With filter

THEORY:

A rectifier is an electrical device that converts alternating current (AC), which

periodically reverses direction, to direct current (DC), which flows in only one direction. The

process is known as rectification. In half wave rectification of a single-phase supply, either the

positive or negative half of the AC wave is passed, while the other half is blocked. Because only

one half of the input waveform reaches the output, mean voltage is lower. Half-wave rectification

requires a single diode in a single-phase supply, or three in a three-phase supply. Rectifiers yield

a unidirectional but pulsating direct current; half-wave rectifiers produce far more ripple than

full-wave rectifiers, and much more filtering is needed to eliminate harmonics of the AC

frequency from the output.

In a Full Wave Rectifier circuit two diodes are now used, one for each half of the cycle.

A multiple winding transformer is used whose secondary winding is split equally into two halves

with a common centre tapped connection, (C). This configuration results in each diode

conducting in turn when its anode terminal is positive with respect to the transformer centre

point C producing an output during both half-cycles twice that for the half wave rectifier so it is

100% efficient

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

The full wave rectifier circuit consists of two power diodes connected to a single load

resistance (RL) with each diode taking it in turn to supply current to the load. When point A of

the transformer is positive with respect to point C, diode D1 conducts in the forward direction as

indicated by the arrows.When point B is positive (in the negative half of the cycle) with respect

to point C, diode D2 conducts in the forward direction and the current flowing through

resistor R is in the same direction for both half-cycles. As the output voltage across the

resistor R is the phasor sum of the two waveforms combined, this type of full wave rectifier

circuit is also known as a bi-phase circuit. As the spaces between each half-wave developed by

each diode is now being filled in by the other diode the average DC output voltage across the

load resistor is now double that of the single half-wave rectifier circuit and is

about 0.637Vmax of the peak voltage, assuming no losses.

Another type of circuit that produces the same output waveform as the full wave rectifier

circuit above, is that of the Full Wave Bridge Rectifier. This type of single phase rectifier uses

four individual rectifying diodes connected in a closed loop bridge configuration to produce

the desired output. The main advantage of this bridge circuit is that it does not require a special

centre tapped transformer, thereby reducing its size and cost. The single secondary winding is

connected to one side of the diode bridge network and the load to the other side of the circuit.

PROCEDURE :

1) Connections are made as per the circuit diagram.

2) All the values of Vsrms, Isrms, Vrrms, VdcFL, VdcNL are measured and noted down in the tabular

column.

3) The Efficiency, Voltage regulation and ripple factor are calculated.

4) The same readings has to be noted down with filter.

EXPECTED GRAPH:

1. Half wave rectifier without filter

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

2. Half wave rectifier with filter

3. Full wave bridge rectifier without filter

4. Full wave bridge rectifier with filter

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

RESULT: Ripple factor, Regulation and efficiency of half wave rectifier, full wave center tap

rectifier and full wave bridge rectifier are verified.

EXPERIMENT NO 11

VERIFICATION OF THEVENINS AND MAXIMUM POWER TRANSFER

THEOREM FOR DC CIRCUITS

AIM:

a) Verification of Thevenins theorem by comparing the value of load current ( I L ) with

given network and with Thevenins network.

b) Verify the maximum power transfer theorem for the given network.

COMPONENTS REQUIRED:

SN

O

1

2

3

4

5

6

Components Name

Resistors

Connecting wires

Bread Board

Dc Ammeter

Power Supply

DRB

Quantity

5

1

1

1

1

CIRCUIT DIAGRAM:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

10k (4), 4.7K,

mA

-

Analog Electronics Circuits Lab Manual

III Semester ECE

THEVININS EQUIVALENT CIRCUIT:

RESISTANT EQUIVALENT CIRCUIT:

THEORATICAL CALCULATIONS:

OBSERVATION:

VTH

(V)

RTH

(K)

IL

(mA)

Theoretical

Practical

PROCEDURE TO FIND VTH :

1. Open circuit the load branch.

2. Keep all the active sources as they are in the network.

3. Find the open circuit voltage across the open circuited load branch.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

PROCEDURE TO FIND RTH

1. Open circuit the load branch.

2. Reduce all the sources to zero.

3. Find the equivalent resistance taking into the open circuited load branch.

b)Maximum Power Transfer Theorem.

CIRCUIT DIAGRAM:

OBSERVATIONS:

Load Resistance

RL ()

Current

IL (mA)

Power

P= IL 2 RL (W)

THEORY:

Thevenins Theorem states that Any linear circuit containing several voltages and resistances

can be replaced by just a Single Voltage in series with a Single Resistor. In other words, it is

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

possible to simplify any Linear circuit, no matter how complex, to an equivalent circuit with

just a single voltage source in series with a resistance connected to a load as shown below.

Thevenins Theorem is especially useful in the Circuit Analysis of power or battery systems and

other interconnected circuits were it will have an effect on the adjoining part of the circuit.

The Maximum Power Transfer Theorem is another useful Circuit Analysis method to

ensure that the maximum amount of power will be dissipated in the load resistance when the

value of the load resistance is exactly equal to the resistance of the power source. The

relationship between the load impedance and the internal impedance of the energy source will

give the power in the load. the impedance of the load will vary from an open-circuit state to a

short-circuit state resulting in the power being absorbed by the load becoming dependent on the

impedance of the actual power source. Then for the load resistance to absorb the maximum

power possible it has to be Matched to the impedance of the power source and this forms the

basis of Maximum Power Transfer.

PROCEDURE:

1.

2.

3.

4.

5.

Test the components.

Connections are made as per the circuit diagram.

Load resistance is varied in steps and corresponding load current values are noted down.

Power delivered to the load is calculated and note it down in the tabular column.

A graph of load resistance versus Power is plotted and verified.

EXPECTED GRAPH:

RESULT: Thevenins theorem and maximum power transfer theorem are verified.

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

EXPERIMENT NO 12

RESONANCE

AIM: To design a series and parallel RLC circuit and obtain its characteristics

COMPONENTS REQUIRED:

SN

O

1

Components Name

Quantity

Signal Generator

2

3

4

5

6

Patch Cords/ Connecting Wires

Dc Ammeter

Decade Resistance Box

Decade Inductance Box

Decade Capacitance Box

1

1

1

1

mA

-

CIRCUIT DIAGRAM:

Series Resonance

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Specification

Analog Electronics Circuits Lab Manual

Parallel Resonance

DESIGN:

For Series Resonance

Let Resonant frequency f0 = 1kHz

Assume the value of the Capacitance C

Resonant frequency f0 for series RLC is given by

1

f0 =

2 LC

f20 =

1

4 2 LC

L =

1

4 f 20 C

2

L = ...................

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

Analog Electronics Circuits Lab Manual

III Semester ECE

For Parallel Resonance

Let Resonant frequency f0 = 1kHz

Assume the value of Inductance L

Resonant frequency f0 is given by

f0 =

1

1 R2

2 LC L2

Substitute the value of L and f0 in the above equation and find the value of C

C = ...................

OSERVATIONS:

For Series and Parallel Resonance

vi=-------Frequency

(Hz)

Current

(mA)

THEORY :

In a series RLC circuit there becomes a frequency point were the inductive reactance of the

inductor becomes equal in value to the capacitive reactance of the capacitor. In other

words,XL = XC. The point at which this occurs is called the Resonant Frequency point, ( r ) of

the circuit, and as we are analysing a series RLC circuit this resonance frequency produces

a Series Resonance. Series Resonance circuits are one of the most important circuits used

electrical and electronic circuits. They can be found in various forms such as in AC mains filters,

noise filters and also in radio and television tuning circuits producing a very selective tuning

circuit for the receiving of the different frequency channels.

In many ways a parallel resonance circuit is exactly the same as the series resonance

circuit. Both are 3-element networks that contain two reactive components making them a

second-order circuit, both are influenced by variations in the supply frequency and both have a

frequency point where their two reactive components cancel each other out influencing the

characteristics of the circuit. Both circuits have a resonant frequency point. The difference this

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

III Semester ECE

time however, is that a parallel resonance circuit is influenced by the currents flowing through

each parallel branch within the parallel LC tank circuit. A tank circuit is a parallel combination

of L and C that is used in filter networks to either select or reject AC frequencies. A parallel

circuit containing a resistance, R, an inductance, L and a capacitance, C will produce aparallel

resonance (also called anti-resonance) circuit when the resultant current through the parallel

combination is in phase with the supply voltage. At resonance there will be a large circulating

current between the inductor and the capacitor due to the energy of the oscillations, then parallel

circuits produce current resonance.

A parallel resonant circuit stores the circuit energy in the magnetic field of the inductor

and the electric field of the capacitor. This energy is constantly being transferred back and forth

between the inductor and the capacitor which results in zero current and energy being drawn

from the supply. This is because the corresponding instantaneous values of IL and IC will always

be equal and opposite and therefore the current drawn from the supply is the vector addition of

these two currents and the current flowing in IR.

In the solution of AC parallel resonance circuits we know that the supply voltage is common for

all branches, so this can be taken as our reference vector. Each parallel branch must be treated

separately as with series circuits so that the total supply current taken by the parallel circuit is the

vector addition of the individual branch currents.

PROCEDURE:

1. Connections are made as per the circuit diagram.

2. The input voltages of 8V peak to peak at 1kHz is applied from the signal generator to the

circuit.

3. Set the designed R,L & C values decade boxes.

4. The frequency is varied at regular intervals of time & the corresponding current is noted

down.

5. From the above reading a graph of frequency versus current is plotted .

EXPECTED GRAPH:

SERIES RESONANT CIRCUIT

PARALLEL RESONANT CIRCUIT

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

Analog Electronics Circuits Lab Manual

RESULT:

DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS

JAIN COLLEGE OF ENGINEERING, BELGAUM

III Semester ECE

You might also like

- Tech Mahindra Aptitude Question PaperDocument22 pagesTech Mahindra Aptitude Question PaperAkash BhagatNo ratings yet

- UPPCS Prelims Re - Exam 2015 General Studies (Paper - I) PDFDocument23 pagesUPPCS Prelims Re - Exam 2015 General Studies (Paper - I) PDFAkash BhagatNo ratings yet

- UPPCS Prelims Exam 2015 General Studies (Paper - I) Question PaperDocument23 pagesUPPCS Prelims Exam 2015 General Studies (Paper - I) Question PaperAkash BhagatNo ratings yet

- DTH 1Document25 pagesDTH 1Akash BhagatNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Monitor Acer LCD AL1516WDocument41 pagesMonitor Acer LCD AL1516WRonan Nolasco0% (1)

- Catalog of Apexls LED Display (Skylar)Document15 pagesCatalog of Apexls LED Display (Skylar)Oktobyanto TrNo ratings yet

- Illustrated Assembly Manual k7000Document12 pagesIllustrated Assembly Manual k7000Ismael LopezNo ratings yet

- Coaxial Cable (Noise Immunity) HuhuDocument10 pagesCoaxial Cable (Noise Immunity) HuhuMohd Izzat Abd GhaniNo ratings yet

- Webcams:: How Does A Webcam Work?Document4 pagesWebcams:: How Does A Webcam Work?Kiran Kumar Athirala0% (1)

- Voltage Protection Relay: FeaturesDocument2 pagesVoltage Protection Relay: FeaturesvenkatNo ratings yet

- Watlow981 982 ManualDocument141 pagesWatlow981 982 ManualIsidro Igigi HernándezNo ratings yet

- Hal1820 2piDocument2 pagesHal1820 2piDaniela AndradeNo ratings yet

- MantraDocument5 pagesMantraFarooq AhmadNo ratings yet

- Mos Field Effect Transistor: Data SheetDocument8 pagesMos Field Effect Transistor: Data SheetAdam SchwemleinNo ratings yet

- Am BroadcastingDocument69 pagesAm BroadcastingJanica Rheanne JapsayNo ratings yet

- Thesis-2008-Printed Monopole Antenna For UltraDocument271 pagesThesis-2008-Printed Monopole Antenna For UltraDr-Pritam Singh BakariyaNo ratings yet

- ESim Lab ManualDocument61 pagesESim Lab ManualDhana PrasadNo ratings yet

- Distributed Control System AssignmentDocument11 pagesDistributed Control System AssignmentGhulam Mustaqeem100% (1)

- LG Plasma Training ManualDocument101 pagesLG Plasma Training Manualvince_thomas7654100% (1)

- EE271 ProjectDocument29 pagesEE271 ProjectQuang MạnhNo ratings yet

- Mechatronics Lab Manual - (01!10!2020)Document24 pagesMechatronics Lab Manual - (01!10!2020)Shreyas HuilgolNo ratings yet

- 30F124 IgbtDocument14 pages30F124 IgbtRiza BaduaNo ratings yet

- Perfect Thym ING: Tape Speed Dry/Wet Mix Select Sound by 1-8 ButtonsDocument3 pagesPerfect Thym ING: Tape Speed Dry/Wet Mix Select Sound by 1-8 ButtonsLievore DavidNo ratings yet

- UPS inspection checklistDocument3 pagesUPS inspection checklistMeraj EEE0% (1)

- EAW KF750 Processor Settings - Rev1Document2 pagesEAW KF750 Processor Settings - Rev1Shawn DuncanNo ratings yet

- Positive Voltage Regulators: FeaturesDocument40 pagesPositive Voltage Regulators: FeaturesFaqih Arsy HikmatyarNo ratings yet

- Serial Communication Protocols and I2C BusDocument25 pagesSerial Communication Protocols and I2C Busghoster0000No ratings yet

- Nowforever Manual E-100Document121 pagesNowforever Manual E-100Pudi PudaNo ratings yet

- PresentationDocument24 pagesPresentationRanjith KumarNo ratings yet

- ETE423 EEE423 - Lecture 3 - Cross Bar SwitchDocument30 pagesETE423 EEE423 - Lecture 3 - Cross Bar SwitchShadman Rahman 1815396660No ratings yet

- 380AX Engineering Design-Microwave LLD (For Zain)Document38 pages380AX Engineering Design-Microwave LLD (For Zain)Hamid RazaNo ratings yet

- DC-DC Part 6 DoubleDocument18 pagesDC-DC Part 6 DoubleDefne AktemizNo ratings yet

- Testing of DC MachinesDocument5 pagesTesting of DC Machines2K20EE102 GauravNo ratings yet

- 31 R20 IIMid Nov-December 2023Document7 pages31 R20 IIMid Nov-December 2023palivelasrinu12No ratings yet