Professional Documents

Culture Documents

MAT12

Uploaded by

tabassam7801Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MAT12

Uploaded by

tabassam7801Copyright:

Available Formats

Audio, Dual-Matched

NPN Transistor

MAT12

Data Sheet

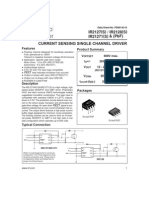

PIN CONFIGURATION

Very low voltage noise: 1 nV/Hz maximum at 100 Hz

Excellent current gain match: 0.5% typical

Low offset voltage (VOS): 200 V maximum

Outstanding offset voltage drift: 0.03 V/C typical

High gain bandwidth product: 200 MHz

C1 1

B1 2

C2

5

E1 3

B2

E2

NOTE

1. SUBSTRATE IS CONNECTED

TO CASE ON TO-78 PACKAGE.

2. SUBSTRATE IS NORMALLY

CONNECTED TO THE MOST

NEGATIVE CIRCUIT POTENTIAL,

BUT CAN BE FLOATED.

09044-001

FEATURES

Figure 1. 6-Lead TO-78

GENERAL DESCRIPTION

The MAT12 is a dual, NPN-matched transistor pair that is

specifically designed to meet the requirements of ultralow

noise audio systems.

With its extremely low input base spreading resistance (rbb'

is typically 28 ) and high current gain (hFE typically exceeds

600 at IC = 1 mA), the MAT12 can achieve outstanding signalto-noise ratios. The high current gain results in superior

performance compared to systems incorporating commercially

available monolithic amplifiers.

Excellent matching of the current gain (hFE) to about 0.5%

and low VOS of less than 10 V typical make the MAT12 ideal

for symmetrically balanced designs, which reduce high-order

amplifier harmonic distortion.

degradation of beta and matching characteristics due to reverse

biasing of the base emitter junction.

The MAT12 is also an ideal choice for accurate and reliable

current biasing and mirroring circuits. Furthermore, because

the accuracy of a current mirror degrades exponentially with

mismatches of VBE between transistor pairs, the low VOS of

the MAT12 does not need offset trimming in most circuit

applications.

The MAT12 is a good replacement for the MAT02, and its

performance and characteristics are guaranteed over the

extended temperature range of 40C to +85C.

Stability of the matching parameters is guaranteed by protection

diodes across the base emitter junction. These diodes prevent

Rev. A

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 20102014 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

MAT12* Product Page Quick Links

Last Content Update: 11/01/2016

Comparable Parts

Design Resources

View a parametric search of comparable parts

Documentation

Data Sheet

MAT12: Audio, Dual-Matched NPN Transistor Data Sheet

MAT12 Material Declaration

PCN-PDN Information

Quality And Reliability

Symbols and Footprints

Discussions

Tools and Simulations

View all MAT12 EngineerZone Discussions

MAT12 SPICE Macro-model

Sample and Buy

Visit the product page to see pricing options

Technical Support

Submit a technical question or find your regional support

number

* This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to

the content on this page does not constitute a change to the revision number of the product data sheet. This content may be

frequently modified.

MAT12

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Thermal Resistance .......................................................................4

Pin Configuration ............................................................................. 1

ESD Caution...................................................................................4

General Description ......................................................................... 1

Typical Performance Characteristics ..............................................5

Revision History ............................................................................... 2

Applications Information .................................................................8

Specifications..................................................................................... 3

Fast Logarithmic Amplifier..........................................................8

Electrical Characteristics ............................................................. 3

Outline Dimensions ....................................................................... 10

Absolute Maximum Ratings............................................................ 4

Ordering Guide .......................................................................... 10

REVISION HISTORY

1/14Rev. 0 to Rev. A

Change to Gain Bandwidth Product Parameter ........................... 3

7/10Revision 0: Initial Version

Rev. A | Page 2 of 12

Data Sheet

MAT12

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VCB = 15 V, IO = 10 A, TA = 25C, unless otherwise specified.

Table 1.

Parameter

DC AND AC CHARACTERISTICS

Current Gain 1

Current Gain Match 2

Noise Voltage Density 3

Symbol

Test Conditions/Comments

Min

Typ

hFE

IC = 1 mA

40C TA +85C

IC = 10 A

40C TA +85C

10 A IC 1 mA

IC = 1 mA, VCB = 0 V

fO = 10 Hz

fO = 100 Hz

fO = 1 kHz

fO = 10 kHz

IC = 1 mA

VCB = 0 V, IC = 1 mA

40C TA +85C

0 V VCB VMAX 4,1 A IC 1 mA 5

1 A IC 1 mA5, VCB = 0 V

40C TA +85C

40C TA +85C, VOS trimmed to 0 V

300

300

200

200

605

hFE

eN

Low Frequency Noise (0.1 Hz to 10 Hz)

Offset Voltage

eN p-p

VOS

Offset Voltage Change vs. VCB

Offset Voltage Change vs. IC

Offset Voltage Drift

VOS/VCB

VOS/IC

VOS/T

Breakdown Voltage, Collector to Emitter

Gain Bandwidth Product

Collector-to-Base Leakage Current

BVCEO

fT

ICBO

Collector-to-Collector Leakage Current 6, 7

ICC

Collector-to-Emitter Leakage Current6, 7

ICES

Input Bias Current

IB

Input Offset Current

IOS

Input Offset Current Drift6

Collector Saturation Voltage

Output Capacitance

Bulk Resistance6

Collector-to-Collector Capacitance

IOS/T

VCE (SAT)

COB

RBE

CCC

Max

Unit

0.5

1.6

0.9

0.85

0.85

0.4

10

2

1

1

1

nV/Hz

nV/Hz

nV/Hz

nV/Hz

V p-p

V

V

V

V

V/C

V/C

V

MHz

pA

nA

pA

nA

pA

nA

nA

nA

nA

nA

pA/C

V

pF

pF

550

10

5

0.08

0.03

200

220

50

70

1

0.3

40

IC = 10 mA, VCE = 10 V

VCB = VMAX

40C TA +85C

VCC = VMAX

40C TA +85C

VCE = VMAX, VBE = 0 V

40C TA +85C

IC = 10 A

40C TA +85C

IC = 10 A

40C TA +85C

IC = 10 A, 40C TA +85C

IC = 1 mA, IB = 100 A

VCB = 15 V, IE = 0 A

10 A IC 10 mA

VCC = 0 V

Current gain is guaranteed with collector-to-base voltage (VCB) swept from 0 V to VMAX at the indicated collector currents.

Current gain match (hFE) is defined as follows: hFE = (100(IB)(hFE min)/IC).

3

Noise voltage density is guaranteed, but not 100% tested.

4

This is the maximum change in VOS as VCB is swept from 0 V to 40 V.

5

Measured at IC = 10 A and guaranteed by design over the specified range of IC.

6

Guaranteed by design.

7

ICC and ICES are verified by the measurement of ICBO.

1

2

Rev. A | Page 3 of 12

200

25

3

35

4

35

4

40

0.05

23

0.3

35

500

500

500

50

50

6.2

13

150

0.2

1.6

MAT12

Data Sheet

ABSOLUTE MAXIMUM RATINGS

THERMAL RESISTANCE

Table 2.

Parameter

Breakdown Voltage of

Collector-to-Base Voltage (BVCBO)

Breakdown Voltage of

Collector-to-Emitter Voltage (BVCEO)

Breakdown Voltage of

Collector-to-Collector Voltage (BVCC)

Breakdown Voltage of

Emitter-to-Emitter Voltage (BVEE)

Collector Current (IC)

Emitter Current (IE)

Storage Temperature Range

Operating Temperature Range

Junction Temperature Range

Lead Temperature (Soldering, 60 sec)

JA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Rating

40 V

Table 3. Thermal Resistance

40 V

Package Type

6-Lead TO-78

40 V

40 V

ESD CAUTION

20 mA

20 mA

65C to +150C

40C to +85C

65C to +150C

300C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. A | Page 4 of 12

JA

150

JC

45

Unit

C/W

Data Sheet

MAT12

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25C, VCE = 5 V, unless otherwise specified.

900

CH1 4.92V p-p

800

TA = +125C

CURRENT GAIN (hFE)

700

TA = +25C

600

500

400

TA = 55C

300

M4.00s

A CH1

15.8V

100

0.001

0.01

0.1

COLLECTOR CURRENT (mA)

Figure 2. Low Frequency Noise (0.1 Hz to 10 Hz), IC = 1 mA, Gain = 10,000,000

09044-005

CH1 2.00V

09044-002

200

Figure 5. Current Gain vs. Collector Current (VCB = 0 V)

900

1k

1mA

700

100

CURRENT GAIN (hFE)

NOISE VOLTAGE DENSITY (nV/ Hz)

800

IC = 1A TEST

10

IC = 10A TEST

IC = 1mA TEST

600

500

400

300

1A

200

10

100

1k

10k

100k

FREQUENCY (Hz)

0

100

09044-003

0.1

0.1

50

50

100

150

TEMPERATURE (C)

09044-006

100

Figure 6. Current Gain vs. Temperature (Excludes ICBO)

Figure 3. Noise Voltage Density vs. Frequency

0.70

100

BASE EMITTER VOLTAGE, VBE (V)

0.65

60

RS = 100k

40

RS = 10k

0.01

0.55

VCE = 5V

0.50

0.45

0.40

0.35

RS = 1k

0

0.001

0.60

0.1

COLLECTOR CURRENT, IC (mA)

Figure 4. Total Noise vs. Collector Current, f = 1 kHz

0.30

0.001

0.01

0.1

COLLECTOR CURRENT, IC (mA)

Figure 7. Base Emitter Voltage vs. Collector Current

Rev. A | Page 5 of 12

10

09044-007

20

09044-004

TOTAL NOISE (nV/ Hz)

80

Data Sheet

100

1000

10

100

CURRENT, ICBO (nA)

1

VCE = 5V

0.1

10

0.1

0.01

0.01

0.1

10

COLLECTOR CURRENT, IC (mA)

0.01

25

09044-008

0.001

0.001

125

100

75

50

TEMPERATURE (C)

09044-010

INPUT RESISTANCE, hIE (M)

MAT12

Figure 11. Collector-to-Base Leakage Current vs. Temperature

Figure 8. Small Signal Input Resistance vs. Collector Current

40

1m

CAPACITANCE, C CB (pF)

CONDUCTANCE, h OE (mho)

35

0.1m

0.01m

VCE = 5V

1

30

25

20

15

10

0.1

0.01

0.1

10

100

09044-009

0.01

0.001

1000

COLLECTOR CURRENT, IC (mA)

10

20

30

40

50

REVERSE BIAS VOLTAGE (V)

09044-011

Figure 12. Collector-to-Base Capacitance vs. Reverse Bias Voltage

Figure 9. Small Signal Output Conductance vs. Collector Current

40

100

CAPACITANCE, C CC (pF)

TA = +125C

10

TA = +25C

1

0.1

30

25

20

15

10

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

SATURATION VOLTAGE, VSAT (V)

0.9

0

0

10

20

30

40

COLLECTOR-TO-SUBSTRATE VOLTAGE (V)

Figure 13. Collector-to-Collector Capacitance vs.

Collector-to-Substrate Voltage

Figure 10. Collector Current vs. Saturation Voltage

Rev. A | Page 6 of 12

50

09044-012

5

0.01

09044-018

COLLECTOR CURRENT, IC (mA)

35

TA = 55C

Data Sheet

MAT12

1000

4.0

COLLECTOR-TO-COLLECTOR

CAPACITANCE, C CC (pF)

COLLECTOR-TO-COLLECTOR

LEAKAGE CURRENT, ICC (nA)

3.5

100

10

0.1

3.0

2.5

2.0

1.5

1.0

50

75

100

125

TEMPERATURE (C)

Figure 14. Collector-to-Collector Leakage Current vs. Temperature

09044-013

0.01

25

10

20

30

REVERSE BIAS VOLTAGE (V)

40

50

09044-014

0.5

Figure 15. Collector-to-Collector Capacitance vs. Reverse Bias Voltage

Rev. A | Page 7 of 12

MAT12

Data Sheet

APPLICATIONS INFORMATION

To compensate for the temperature dependence of the kT/q term, a

resistor with a positive 0.35%/C temperature coefficient is selected

for R2. The output is inverted with respect to the input and is

nominally 1 V/decade using the component values indicated.

FAST LOGARITHMIC AMPLIFIER

The circuit of Figure 16 is a modification of a standard logarithmic amplifier configuration. Running the MAT12 at 2.5 mA per

side (full scale) allows for a fast response with a wide dynamic

range. The circuit has a seven decade current range and a five

decade voltage range, and it is capable of 2.5 s settling time to

1% with a 1 V to 10 V step. The output follows the equation:

R3 + R2 kT VREF

ln

R2

q

VIN

+15V

VIN

(0V TO 10V)

RS

4k

8

AD8512

VO

3

4

15V

330pF

R3

7.5k

MAT12

330pF

VREF

10V

R1

4k

6

1/2

AD8512

4k

R2

500

R2 = 0.35%/C

09044-015

VO =

Figure 16. Fast Logarithmic Amplifier

Rev. A | Page 8 of 12

Data Sheet

MAT12

Because IC1 is made equal to 10 IC2, and assuming TA = 25C,

Equation 2 becomes

LOG CONFORMANCE TESTING

The log conformance of the MAT12 is tested using the circuit

shown in Figure 18. The circuit employs a dual transdiode

logarithmic converter operating at a fixed ratio of collector

currents that are swept over a 10:1 range. The output of each

transdiode converter is the VBE of the transistor plus an error

term, which is the product of the collector current and rBE, the

bulk emitter resistance. The difference of the VBE is amplified at

a gain of 100 by the AMP02 instrumentation amplifier. The

differential emitter base voltage (VBE) consists of a temperaturedependent dc level plus an ac error voltage, which is the deviation

from true log conformity as the collector currents vary.

VBE = 59 mV + 0.9 IC1 rBE (rBE ~ 0)

As viewed on an oscilloscope, the change in VBE for a 10:1

change in IC is shown in Figure 17.

61.5

LOGGING ERROR, VBE (mV)

61.0

The output of the transdiode logarithmic converter comes from

the following idealized intrinsic transistor equation (for silicon)

kT I C

ln

q

IS

(1)

58.5

With the oscilloscope ac-coupled, the temperature dependent

term becomes a dc offset and the trace represents the deviation

from true log conformity. The bulk resistance can be calculated

from the voltage deviation, VO, and the change in collector

current (9 mA):

rBE =

(2)

IC1

9 mA 100

(3)

This procedure solves for rBE for Side A. Switching R1 and R2

provides the rBE for Side B. Differential rBE is found by making

R1 = R2.

SIDE A DUT

Q1

V

+ BE +15V

1/2

AD8512

100pF

VCC

VO

500

1N914

+15V

15V

100pF

AV = 100

AMP02

VOUT = 100VBE

15V

1k

IC2

1/2

AD8512

500

15V

1N914

+

+15V

VBE

Q2

SIDE B DUT

09044-017

1k

100

10

Figure 17. Emitter Base, Log Conformity

A ramp function that sweeps from 1 V to 10 V is converted by

the op amps to a collector current ramp through each transistor.

VCC

COLLECTOR CURRENT (mA)

An error term must be added to Equation 1 to allow for the

bulk resistance (rBE) of the transistor. Error due to the op amp

input current is limited by use of the AD8512 dual op amp. The

resulting AMP02 input is:

I

kT

= ln C1 + I C1rBE1 I C2 rBE2

q

I C2

59.5

59.0

where:

k is Boltzmanns constant (1.38062 1023 J/K).

q is the unit electron charge (1.60219 1019C).

T is the absolute temperature, K (= C + 273.2).

IS is the extrapolated current for VBE 0 (VBE tending to zero).

IC is the collector current.

VBE =

60.0

09044-016

V BE =

60.5

Figure 18. Log Conformance Circuit

Rev. A | Page 9 of 12

MAT12

Data Sheet

OUTLINE DIMENSIONS

0.185 (4.70)

0.165 (4.19)

REFERENCE PLANE

0.750 (19.05)

0.500 (12.70)

0.250 (6.35) MIN

0.100 (2.54) BSC

0.050 (1.27) MAX

0.160 (4.06)

0.110 (2.79)

0.335 (8.51)

0.305 (7.75)

0.370 (9.40)

0.335 (8.51)

0.040 (1.02) MAX

0.045 (1.14)

0.010 (0.25)

0.200

(5.08)

BSC

0.045 (1.14)

0.027 (0.69)

2

0.019 (0.48)

0.016 (0.41)

0.100

(2.54)

BSC

0.021 (0.53)

0.016 (0.41)

1

0.034 (0.86)

0.027 (0.69)

45

BSC

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

022306-A

BASE & SEATING PLANE

Figure 19. 6-Pin Metal Header Package [TO-78]

(H-06)

Dimensions shown in inches and (millimeters)

ORDERING GUIDE

Model 1

MAT12AHZ

1

Temperature Range

40C to +85C

Package Description

6-Pin Metal Header Package [TO-78]

Z = RoHS Compliant Part.

Rev. A | Page 10 of 12

Package Option

H-06

Data Sheet

MAT12

NOTES

Rev. A | Page 11 of 12

MAT12

Data Sheet

NOTES

20102014 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09044-0-1/14(A)

Rev. A | Page 12 of 12

You might also like

- Ach4518 471 TD01Document4 pagesAch4518 471 TD01tabassam7801No ratings yet

- 2SD 2017 PDFDocument1 page2SD 2017 PDFtabassam7801No ratings yet

- Lithium Ion Secondary Battery Applications Portable Equipment Applications Notebook PC ApplicationsDocument11 pagesLithium Ion Secondary Battery Applications Portable Equipment Applications Notebook PC Applicationstabassam7801No ratings yet

- Hall BookDocument126 pagesHall BookbanguyenbkNo ratings yet

- Uc 1709Document15 pagesUc 1709tabassam7801No ratings yet

- Turn Ratio TestDocument8 pagesTurn Ratio TestImran Nawaz MehthalNo ratings yet

- Mic 4120Document10 pagesMic 4120tabassam7801No ratings yet

- LM 2575 TDocument5 pagesLM 2575 Ttabassam7801No ratings yet

- CCTV General PDFDocument97 pagesCCTV General PDFtabassam7801No ratings yet

- Ir 2112Document18 pagesIr 2112Valeriu DumitracheNo ratings yet

- Fy4aej 03Document9 pagesFy4aej 03tabassam7801No ratings yet

- Vow 3120Document11 pagesVow 3120tabassam7801No ratings yet

- IRF7103 (Dual)Document9 pagesIRF7103 (Dual)tabassam7801No ratings yet

- Encoder Detector IC for Optical EncodersDocument4 pagesEncoder Detector IC for Optical Encoderstabassam7801No ratings yet

- Automotive Mosfet 2010 BRDocument16 pagesAutomotive Mosfet 2010 BRtabassam7801No ratings yet

- Ir 2127Document16 pagesIr 2127kimonspNo ratings yet

- Auto MOSFET NamingDocument3 pagesAuto MOSFET Namingtabassam7801No ratings yet

- IRF7103 (Dual)Document9 pagesIRF7103 (Dual)tabassam7801No ratings yet

- 193 Universal BridgeDocument4 pages193 Universal Bridgetabassam7801No ratings yet

- Alpha, Beta & Gamma DecayDocument7 pagesAlpha, Beta & Gamma DecayFaisal ARNo ratings yet

- BLF278 Wideband RF Power MosfetDocument23 pagesBLF278 Wideband RF Power MosfetAmador Garcia IIINo ratings yet

- A guide to the letter ADocument4 pagesA guide to the letter Atabassam7801No ratings yet

- Ca 3083Document4 pagesCa 3083tabassam7801No ratings yet

- 74HC4050 CNV PDFDocument7 pages74HC4050 CNV PDFtare890No ratings yet

- A1271 (To 92)Document1 pageA1271 (To 92)Josué GarciaNo ratings yet

- AO4620Document7 pagesAO4620Victor ChangNo ratings yet

- 2SD 882Document10 pages2SD 882tabassam7801No ratings yet

- 2N5401Document4 pages2N5401tabassam7801No ratings yet

- Power Transistor: SPP11N60C3 SPI11N60C3, SPA11N60C3, SPA11N60C3 E8185 Cool MOS™Document16 pagesPower Transistor: SPP11N60C3 SPI11N60C3, SPA11N60C3, SPA11N60C3 E8185 Cool MOS™tabassam7801No ratings yet

- H1061Document1 pageH1061tabassam7801No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- OLED Specification SheetDocument27 pagesOLED Specification SheetBianca SandorNo ratings yet

- Lab 5 Series and Parallel CircuitsDocument3 pagesLab 5 Series and Parallel CircuitsJimmyPowellNo ratings yet

- Service Guide Rev E - Invivo Expression PDFDocument96 pagesService Guide Rev E - Invivo Expression PDFBalaji BalasubramanianNo ratings yet

- 2014 Winter Model Answer PaperDocument25 pages2014 Winter Model Answer Papernavneet100% (1)

- Service Manual TV Lg42px4rvh EnglishDocument37 pagesService Manual TV Lg42px4rvh EnglishRc Uno UnoNo ratings yet

- Loadsensing Technical Datasheet September 2019Document8 pagesLoadsensing Technical Datasheet September 2019davzuluetaNo ratings yet

- Transformer Class 12 ProjectDocument21 pagesTransformer Class 12 ProjectAbhishek Sen50% (2)

- LTE FDD Cluster DT - Analysis ReportDocument23 pagesLTE FDD Cluster DT - Analysis ReportAnonymous 0d9mC0OaxENo ratings yet

- Teaching Electrodynamic Levitation Theory: (3) - Teaching at University Level RequiresDocument9 pagesTeaching Electrodynamic Levitation Theory: (3) - Teaching at University Level RequiresArda YıldızNo ratings yet

- New Core Loss Measurement Methods: Mingkai Mu, Fred C. LeeDocument35 pagesNew Core Loss Measurement Methods: Mingkai Mu, Fred C. LeeMichaelEdwardWrightNo ratings yet

- 71 Busbar-Power PDFDocument6 pages71 Busbar-Power PDFVladNo ratings yet

- Cbse Electrostatics and Current ElectricityDocument6 pagesCbse Electrostatics and Current ElectricityHimanshu KatwalNo ratings yet

- Low-Power CODEC With Audio/Voice DSP: 1. General DescriptionDocument4 pagesLow-Power CODEC With Audio/Voice DSP: 1. General Descriptionwicka3No ratings yet

- Transformer Design AnalysisDocument6 pagesTransformer Design AnalysisAkash VermaNo ratings yet

- PR 436Document2 pagesPR 436hieu0% (1)

- Ansaldo Electric Drives 15/30 kW Technical SpecsDocument4 pagesAnsaldo Electric Drives 15/30 kW Technical SpecsMr.K ch50% (2)

- AC Circuits Knowledge Bank ExplainedDocument34 pagesAC Circuits Knowledge Bank ExplainedMalak SamirNo ratings yet

- Buchholz Relay in Transformers (Working Principle) - Electrical4UDocument5 pagesBuchholz Relay in Transformers (Working Principle) - Electrical4UHarsh PatelNo ratings yet

- EMC quiz questionsDocument1 pageEMC quiz questionsSree MurthyNo ratings yet

- 1000-400-933 - D-X8000 Light Source Service GuideDocument84 pages1000-400-933 - D-X8000 Light Source Service GuideHichem NaghmouchiNo ratings yet

- Lecture5 Chapter2 - Positive and Negative LogicDocument11 pagesLecture5 Chapter2 - Positive and Negative LogicAyesha HussainNo ratings yet

- Battery DesulfatorsDocument4 pagesBattery DesulfatorsAlex MaianoNo ratings yet

- 32N50C3 Mos PDFDocument11 pages32N50C3 Mos PDFHưng HQNo ratings yet

- Engineering Division: FF/HART ConfigurationDocument34 pagesEngineering Division: FF/HART ConfigurationJorge Pérez FrisanchoNo ratings yet

- Lightning Arrester Modeling Using Atp-Emtp: Trin Saengsuwan and Wichet ThipprasertDocument4 pagesLightning Arrester Modeling Using Atp-Emtp: Trin Saengsuwan and Wichet ThipprasertgumilarNo ratings yet

- ASUS ROG RAMPAGE VI EXTREME ENCORE MANUAL Compressed PDFDocument116 pagesASUS ROG RAMPAGE VI EXTREME ENCORE MANUAL Compressed PDFchenchozarangolloNo ratings yet

- GSM Based Home Automation System ApplicationDocument8 pagesGSM Based Home Automation System Applicationddarunk1989373No ratings yet

- Generator Governor Frequency Response Webinar April 2015Document31 pagesGenerator Governor Frequency Response Webinar April 2015Jeans GonzalezNo ratings yet

- Properties Of Nλ/2 LinesDocument12 pagesProperties Of Nλ/2 LinesJunar JohnNo ratings yet

- Monopole & Dipole Antennas LabDocument8 pagesMonopole & Dipole Antennas LabSharjeel AsifNo ratings yet