Professional Documents

Culture Documents

Eight-Channels, 192Khz, 24-Bits Digital Audio Processor For Full Digital Amplifier

Uploaded by

vanjalujicOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Eight-Channels, 192Khz, 24-Bits Digital Audio Processor For Full Digital Amplifier

Uploaded by

vanjalujicCopyright:

Available Formats

PS9850

Multi-channel Digital Audio Processor

Eight-channels, 192kHz, 24-bits

Digital Audio Processor for Full Digital Amplifier

Introduc- Fea-

tion_______________________ tures___________________________

The PS9850 is a highly integrated system-on-chip audio Audio Interface

solution for multi-channel AV systems such as upper 5.1 ü 8-Channel serial audio interface.

channels, 6.1 channels or 7.1 channels. This device is a ü Supports 16/18/20/24-bit input

high performance PWM modulator and a high resolution ü Supports 13kHz ~ 192kHz input Fs.

digital audio processor.

ü Supports up to 192kHz Fs for 8 Channels.

ü Data formats

This device uses AD modulation operating at a 384kHz 2

ü (I S, left-justified or right-justified)

switching rate, supports AM interference rejection function,

and has PWM sequences for pop-less. ü Microphone serial audio interface.

ü Sony Philips Digital Interface (SPDIF)

This device has an asynchronous sample rate converter

for a variety of input sample rates with an embedded jitter Audio Processor

correction function. For high performances and high reso- ü 192kHz sampling rate of audio processing

lutions, audio processors operate 30bit data paths and a ü 30x24 multipliers and 54-bit accumulator architec-

192kHz sample rate. ture

ü 8-Channel sample rate converter

This processor consists of equalizers, volume controls, a ü Fully programmable 69-band equalizers

bass management and automatic gain limiting functions. ü Preset Graphic Equalizers

Equalizers are fully programmable that have 69 band bi- ü (+12 to -12, 0.5dB/step)

quad filters with either a static or graphic mode and have ü Pop Noise Reduction when equalizer coefficient

usable preset graphic equalizer. Downloads

ü Bass management

This device is operated with a single power source, as it ü Four subsonic filter and LPF for subwoofer chan-

has regulators for its core. This device has a built-in PLL nel

without external loop filter. Therefore the external compo- ü Digital de-emphasis filter

nents are minimized. ü Pre/post full matrix channel mixing.

ü Pre/post mapping.

Applications______________________ ü Main volume control

ü DVD receiver ü (+18dB to -70dB, 0.5dB/step)

ü Hi-Fi AV Receiver ü Soft/trim volume control

ü Set-top box ü (+12dB to -12dB, 0.5dB/step)

ü Car AV Systems ü Four independent automatic gain limiter

ü Digital audio workstations ü Supports night mode

ü Clipping Free Processing

Features__________________________ ü (30-bit data processing)

General

ü 3.3V single power supply PCM to PWM modulator

ü Embedded regulator for 1.2V Power ü Pop noise reduction

ü 64pin TQFP package ü AM interference rejection

ü Built-in PLL without external loop filter ü 2-Channel PWM headphone output

ü Internal clock generation with X-tal ü 8-Channel PWM speaker output

2

ü I C or SPI serial control slave interface ü PWM on/off control per channel

ü AD modulation operation

ü 384kHz carrier frequency

Copyright ©1999-2009 Pulsus Technologies, Inc. Version: 0.93

Reserves the right to make changes to the information contained in this document without notice August 17, 2009

Contact PULSUS Technologies for recent information. CONFIDENTIAL Page: 2 / 3

PS9850

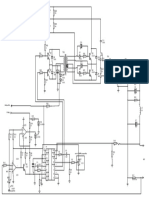

Block Diagram___________________________________________________________

MBCK Sync. generator

MLRCK HP_LEFT P/M

MSDIN0

Pre-mapper

Sample Rate

MSDIN1 Level Input HP_RIGHT_P/M

Convertor

cut

Post-mixer

Equalizer

MSDIN2 interface

MSDIN3 Receiver

Volume control

(I2S / PWM_CH1_P/M

Post-mapper

Bass mixer

Pre-mixer

SPDIF)

PWM_CH2_P/M

SBCK Sync. generator

SLRCK PWM_CH3_P/M

interpolator

SSDIN0 PWM

Convert

MIC

SSDIN1 or PWM_CH4_P/M

Input interface

SSDIN2 Bass

Transmitter

SSDIN3 managem PWM_CH5_P/M

ent

MIC_SDIN PWM_CH6_P/M

MIC_LRCK

MIC interface

MIC_BCK PWM_CH7_P/M

MIC_MCLK

POP

SPDIF NR PWM_CH8_P/M

EXT_MUTE

Internal Internal

Clock Reset

SPI_I2C

SO_SDA Host Internal Clock control

SCK_SCL Interface Controls

SI_AD0 (I2C, SPI)

Crystal

nCS_AD2

Oscillator PLL Power Supply Regulator

XIN

XOUT

VDD_CORE

VDD_IO

VDD_A

VDD_VIN1/2

VDD_VOUT1/2

nRESET

Copyright ©1999-2009 Pulsus Technologies, Inc. Version: 0.93

Reserves the right to make changes to the information contained in this document without notice August 17, 2009

Contact PULSUS Technologies for recent information. CONFIDENTIAL Page: 3 / 3

You might also like

- Allrounder 470-520 CDocument8 pagesAllrounder 470-520 CradhoinezerellyNo ratings yet

- NPM Motion Control Serial Communication CatalogDocument24 pagesNPM Motion Control Serial Communication CatalogElectromateNo ratings yet

- Nippon Pulse 2011 CatalogDocument98 pagesNippon Pulse 2011 CatalogElectromateNo ratings yet

- Control Valve and Steam Line PDFDocument19 pagesControl Valve and Steam Line PDFRofi MuhammadNo ratings yet

- National Semiconductor Lmd18245 Stepper ControllerDocument9 pagesNational Semiconductor Lmd18245 Stepper ControllerMaja i Aleksandar JovanovićNo ratings yet

- Dolby Pro-Logic Surround Matrix DecoderDocument12 pagesDolby Pro-Logic Surround Matrix DecoderChethan GowdaNo ratings yet

- NETVIEL Cable Specification For Direct Burial Cable - SinglemodeDocument6 pagesNETVIEL Cable Specification For Direct Burial Cable - SinglemodeMuhammad SyaifulhaqNo ratings yet

- SolidWorks Silabus PDFDocument2 pagesSolidWorks Silabus PDFYuswa YuswandhiNo ratings yet

- NAK80 MaterialDocument3 pagesNAK80 MaterialRicky Indra DjunawanNo ratings yet

- Basic Guidelines On Routeros Configuration and Debugging: Martins Strods Mikrotik, LatviaDocument56 pagesBasic Guidelines On Routeros Configuration and Debugging: Martins Strods Mikrotik, LatviabinarydataNo ratings yet

- Handy FlexDocument3 pagesHandy FlexwinNo ratings yet

- Floor Standing Indoor and Outdoor Air Conditioner UnitsDocument2 pagesFloor Standing Indoor and Outdoor Air Conditioner UnitsCombox Black100% (1)

- TL494 Psu PDFDocument1 pageTL494 Psu PDFDragan StojkovicNo ratings yet

- Polaroid P4000: Desktop Passport PrinterDocument2 pagesPolaroid P4000: Desktop Passport Printerandrak18No ratings yet

- 16 Instruksi Outseal ArduMeka 11032022 EBUDocument43 pages16 Instruksi Outseal ArduMeka 11032022 EBUEgia PinemNo ratings yet

- Central Lock DiagramDocument5 pagesCentral Lock DiagramAhmad MuhajirNo ratings yet

- Clarion Co. Service Manual CD PlayerDocument32 pagesClarion Co. Service Manual CD PlayerEsteban GarciaNo ratings yet

- Sandwich Panel - BONDOR INDONESIA PDFDocument27 pagesSandwich Panel - BONDOR INDONESIA PDFSaor PakpahanNo ratings yet

- Trooper 3000 Series Process IndicatorDocument2 pagesTrooper 3000 Series Process Indicatorwramadhani65No ratings yet

- Plat PlendesDocument5 pagesPlat PlendesTaufikkurrahman Upik TelerNo ratings yet

- Distribution Transformer Specs and DiagramsDocument1 pageDistribution Transformer Specs and DiagramsAgung TriyonoNo ratings yet

- Ul01ao Iso Red TB SRCDocument3 pagesUl01ao Iso Red TB SRCIndustrial IT Solution Pvt. ltdNo ratings yet

- Split Plummer Block Housings SNVDocument84 pagesSplit Plummer Block Housings SNVKharimul AzizNo ratings yet

- 01 - Optimax Inverter - EnglishDocument8 pages01 - Optimax Inverter - EnglishRaman GuptaNo ratings yet

- G160 Horizontal Engine High PerformanceDocument2 pagesG160 Horizontal Engine High Performancegustavo9810No ratings yet

- PT Stainless Steel Valve Manufacturer OverviewDocument33 pagesPT Stainless Steel Valve Manufacturer OverviewLuqman ElhanifNo ratings yet

- Manual Book UV AQUAFIDESDocument48 pagesManual Book UV AQUAFIDESMartha WidjayaNo ratings yet

- Schlosser-Pfeiffer Radialpresse EnglischDocument8 pagesSchlosser-Pfeiffer Radialpresse EnglischHESSGROUPNo ratings yet

- Installation Manual: MP1800X Series RouterDocument65 pagesInstallation Manual: MP1800X Series RouterBudi SantosoNo ratings yet

- NBE-204!04!002 R3 Schemetic UNIT AUX UpdateDocument31 pagesNBE-204!04!002 R3 Schemetic UNIT AUX UpdateSamsudin AhmadNo ratings yet

- RS-WD-HW-N01 485 Infrared Temperature Sensor User Manual: Document Version V1.0Document8 pagesRS-WD-HW-N01 485 Infrared Temperature Sensor User Manual: Document Version V1.0NILTON RAMOS ESTEBANNo ratings yet

- GLOFA PLC ModbusFunctionBlock (ENG)Document10 pagesGLOFA PLC ModbusFunctionBlock (ENG)ejhagunNo ratings yet

- Speaker TOADocument4 pagesSpeaker TOASenoPati KudusNo ratings yet

- Wiring Accessories CatalogueDocument88 pagesWiring Accessories CatalogueDhanushka RathnasooriyaNo ratings yet

- 04.GPD155-F All New Nmax 155 Connected Version Camshaft & ChainDocument1 page04.GPD155-F All New Nmax 155 Connected Version Camshaft & Chainandi yusufNo ratings yet

- fr150 Series User Manual en v1.2Document131 pagesfr150 Series User Manual en v1.2Hendrewel Ferreira NunesNo ratings yet

- How To Install Autocad 2010Document3 pagesHow To Install Autocad 2010Achmad RosikunNo ratings yet

- Kawasaki Ninja 250 SL Standard 158468Document1 pageKawasaki Ninja 250 SL Standard 158468EKO FITRIYANTONo ratings yet

- Diagram Listrik Honda Tiger 2000 Panel Setang KananDocument1 pageDiagram Listrik Honda Tiger 2000 Panel Setang KananDiToNo ratings yet

- FA-10-005 - Single Line Diagram-10-003Document1 pageFA-10-005 - Single Line Diagram-10-003avj278631No ratings yet

- Brosur KDK Fan PDFDocument39 pagesBrosur KDK Fan PDFanon_795575819No ratings yet

- J4 Alarm ListDocument174 pagesJ4 Alarm ListElvira Nisa SNo ratings yet

- BDI-2001B (Controlador de Dosagem)Document48 pagesBDI-2001B (Controlador de Dosagem)Cesar Lima100% (1)

- Gambar Kerja Restoran Po 1Document9 pagesGambar Kerja Restoran Po 1Bima Tri Sakti100% (1)

- Home Elevator SED200 SVB200Document5 pagesHome Elevator SED200 SVB200Trung Duy TrầnNo ratings yet

- Temet Wall Sleeve Sj-150 v00082-bDocument2 pagesTemet Wall Sleeve Sj-150 v00082-bGiuseppe Ferrari100% (1)

- Basslink T: Powered Subwoofer System Service ManualDocument23 pagesBasslink T: Powered Subwoofer System Service ManualJYRIJJNo ratings yet

- AS358MDocument15 pagesAS358Mantonio2065100% (1)

- ELEMAX® - Elemax SH7600EX ModelDocument1 pageELEMAX® - Elemax SH7600EX Modelاختر بلوچNo ratings yet

- DIAGRAM WIRING Honda Supra XDocument2 pagesDIAGRAM WIRING Honda Supra XKoko T.Elektro B1No ratings yet

- VMC ADocument1 pageVMC Aari_aristaNo ratings yet

- Gambar Teknis Hino 500 Ranger FG 235 JJ Fire Truck 5500 Water Foam Double Cabin SNI Standart PROTEKTA FIREFORT VATORDocument1 pageGambar Teknis Hino 500 Ranger FG 235 JJ Fire Truck 5500 Water Foam Double Cabin SNI Standart PROTEKTA FIREFORT VATORSyarifNo ratings yet

- RCEG-12 Assembly Drawings and SchematicsDocument121 pagesRCEG-12 Assembly Drawings and SchematicsEnrique Martinez RojasNo ratings yet

- ADVANCE STANDALONE Yamaha Z1 (EN) PDFDocument10 pagesADVANCE STANDALONE Yamaha Z1 (EN) PDFTechno TechNo ratings yet

- Easy Maintenance Air Conditioning System FeaturesDocument1 pageEasy Maintenance Air Conditioning System FeaturesKevin Lau100% (1)

- Cooling Only D-Series Split System Room Air ConditionersDocument59 pagesCooling Only D-Series Split System Room Air Conditionersvtin tinNo ratings yet

- ISO 9001 and ISO 14001 Certified Sigma EscalatorsDocument12 pagesISO 9001 and ISO 14001 Certified Sigma EscalatorsRachmat Syaiful MujabNo ratings yet

- Ic ps9850Document3 pagesIc ps9850ayu fadliNo ratings yet

- Lake LM44 DolbyDocument4 pagesLake LM44 Dolbyluz.negociosenlineaNo ratings yet

- STA308A: Multichannel Digital Audio Processor With DDX™Document46 pagesSTA308A: Multichannel Digital Audio Processor With DDX™Milka RamirezNo ratings yet

- PIC Basic CommandsDocument4 pagesPIC Basic Commandsvanjalujic100% (1)

- Upustvo Za FLASh 1212 VcdsDocument8 pagesUpustvo Za FLASh 1212 VcdsvanjalujicNo ratings yet

- BREHMER Polygraph 381/1eA3 Sewing Machine for SaleDocument3 pagesBREHMER Polygraph 381/1eA3 Sewing Machine for Salevanjalujic50% (2)

- Bizhub C450 Theory OperationDocument292 pagesBizhub C450 Theory OperationBurz OctavianNo ratings yet

- DS200 - Katalog Motora RolandDocument20 pagesDS200 - Katalog Motora RolandvanjalujicNo ratings yet

- Auto Manuals 1800 BooksDocument1 pageAuto Manuals 1800 BooksvanjalujicNo ratings yet

- Arduino Cheat SheetDocument1 pageArduino Cheat SheetMC. Rene Solis R.100% (9)

- EncoderDocument6 pagesEncodervanjalujic100% (1)

- Mercedes Benz Fault Code ManualDocument107 pagesMercedes Benz Fault Code ManualAnthony75% (53)

- Metrics For MechanicsDocument63 pagesMetrics For Mechanicseduardorojas007No ratings yet

- ProjektiDocument2 pagesProjektivanjalujicNo ratings yet

- Anti Lock BrakesDocument44 pagesAnti Lock BrakesyogendranathbommuNo ratings yet

- Arduino Tutorials enDocument100 pagesArduino Tutorials enManuelMarceloFerreiraLopes100% (1)

- PIC Basic CommandsDocument4 pagesPIC Basic Commandsvanjalujic100% (1)

- Automotive BasicsDocument146 pagesAutomotive BasicsSamuel Premkumar85% (20)

- Kord Operation ManualDocument55 pagesKord Operation Manualvanjalujic100% (3)

- Aftermarket Seat Heater Installation For Mercedes - C32Document2 pagesAftermarket Seat Heater Installation For Mercedes - C32vanjalujicNo ratings yet

- Coils IgnitionDocument24 pagesCoils IgnitionLuis Daniel Rodriguez VeraNo ratings yet

- Danfoss FC051 - BrošuraDocument8 pagesDanfoss FC051 - BrošuravanjalujicNo ratings yet

- Canon Ir 5075-5065-5055 0Document12 pagesCanon Ir 5075-5065-5055 0vanjalujicNo ratings yet

- Service Info Weller EC 2002Document14 pagesService Info Weller EC 2002Adrian AdiNo ratings yet

- Motor SeverDocument19 pagesMotor SevervanjalujicNo ratings yet

- 39 44Document6 pages39 44strociNo ratings yet

- Wolsvagen Sifre BojeDocument1 pageWolsvagen Sifre BojevanjalujicNo ratings yet

- 873003.Vw - How To Read Wiring Diagrams. (USA)Document83 pages873003.Vw - How To Read Wiring Diagrams. (USA)Fernando García100% (3)

- MProgDocument52 pagesMProgvanjalujicNo ratings yet

- Pneumatic Paper Cutting Machine CountingDocument23 pagesPneumatic Paper Cutting Machine CountingManish Shetty100% (2)

- Biologija I KemijaDocument18 pagesBiologija I KemijavanjalujicNo ratings yet

- Ideal 7228 95Document4 pagesIdeal 7228 95vanjalujic100% (4)

- 45 60055 Ee416 2017 5 2 1 Ee413 Laboratory Experiments GroupDocument80 pages45 60055 Ee416 2017 5 2 1 Ee413 Laboratory Experiments Groupraghad zuhair yousifNo ratings yet

- Calculating feeder size using diversity and demand factorsDocument3 pagesCalculating feeder size using diversity and demand factorsAnonymous SOQFPWBNo ratings yet

- Puranmal Lahoti Government Polytechnic College, Latur: Micro-Project ProposalDocument11 pagesPuranmal Lahoti Government Polytechnic College, Latur: Micro-Project ProposalAadil • ShaikhNo ratings yet

- Tran Smiss Io N Li NeDocument17 pagesTran Smiss Io N Li NesinghrichaNo ratings yet

- TS Connection 2203NE1 PDFDocument1,266 pagesTS Connection 2203NE1 PDFAtiqur Rahman AtiqNo ratings yet

- Load Schedule Calculation SheetDocument6 pagesLoad Schedule Calculation SheetlakshminarayananNo ratings yet

- Strategy for Undervoltage Load Shedding Using Dynamic Load ModelingDocument5 pagesStrategy for Undervoltage Load Shedding Using Dynamic Load ModelingSyaifuddinZuhriNo ratings yet

- PIC18F Naming ConventionDocument1 pagePIC18F Naming ConventionMudasser waqasNo ratings yet

- Ieee Conference Paper - 01Document9 pagesIeee Conference Paper - 01Asha PatilNo ratings yet

- Powerone p110002Document13 pagesPowerone p110002Jim BeanNo ratings yet

- Man BNWAS 2.0.1 EngDocument38 pagesMan BNWAS 2.0.1 Eng'Egemen KayaNo ratings yet

- RDS Technical SpecificationDocument163 pagesRDS Technical Specificationwhistle-blower100% (1)

- Safety SwitchesDocument56 pagesSafety SwitchesaglegarteNo ratings yet

- 700S PartslistDocument95 pages700S PartslistdiewiesNo ratings yet

- Ansys Ansoft MaxwellDocument2 pagesAnsys Ansoft MaxwellGustavo Myrria0% (1)

- Generator Capability CurveDocument20 pagesGenerator Capability CurvegnathblNo ratings yet

- 10kV and 15kV MEGOHMMETERS: User ManualDocument72 pages10kV and 15kV MEGOHMMETERS: User ManualMartin NNo ratings yet

- Arc FurnaceDocument2 pagesArc FurnaceZEAGUINo ratings yet

- P-95 DIGITAL PIANO - Service Manual PDFDocument24 pagesP-95 DIGITAL PIANO - Service Manual PDFJosé Alejandro100% (2)

- Clock GatingDocument10 pagesClock Gatingpavanmk2501No ratings yet

- Wall Mounted G4 Series High Performance and Powerful Air Ow: DC InverterDocument2 pagesWall Mounted G4 Series High Performance and Powerful Air Ow: DC InverterZacke EsmaNo ratings yet

- 5 Wideband FM Examples of BW Estimation and Why FMDocument8 pages5 Wideband FM Examples of BW Estimation and Why FMMohamed ShabanaNo ratings yet

- Formula Notes Network AnalysisDocument9 pagesFormula Notes Network AnalysisSubramanyam Kamatham100% (1)

- Eamm-A enDocument80 pagesEamm-A enIqtidar GulNo ratings yet

- Facade LightingDocument11 pagesFacade LightingsasikalaNo ratings yet

- Project Standards and Specifications Power System Design Rev01Document9 pagesProject Standards and Specifications Power System Design Rev01totongopNo ratings yet

- 3.1 Aim: Use PLC To Test The START STOP and TEST Logic For Two Inputs and One Output. 3.2 Apparatus: PLC Software, NO and NC Switches. 3.3theoryDocument3 pages3.1 Aim: Use PLC To Test The START STOP and TEST Logic For Two Inputs and One Output. 3.2 Apparatus: PLC Software, NO and NC Switches. 3.3theoryrashmi patilNo ratings yet

- Dsp-Unit 6.2 Window Based Fir FiltersDocument92 pagesDsp-Unit 6.2 Window Based Fir FiltersMaheswaraNo ratings yet

- Irjash-Paper Ravindra ParabDocument9 pagesIrjash-Paper Ravindra ParabRavindra ParabNo ratings yet