Professional Documents

Culture Documents

ADSDjan 2018

Uploaded by

Anonymous 0CTT03jlEOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ADSDjan 2018

Uploaded by

Anonymous 0CTT03jlECopyright:

Available Formats

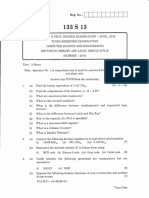

lllllllflllllllilllllllilllllllll Reg. No.

Question Paper Code z 47 03L

M. E.lN{.Tech. D EGREE EXAMINATION, JANUARY 20 1 8

First Semester

AP 5151 - AD'^*t#L?I1?ffi Hi"U* D ESIGN

(Common to M.E. VLSI Design)

(Regulations 2017)

: Three Hours wuJw.recentquestion paperrcom" Maximum : 100 Marks

Answer ALL q,r"*tiorrJ

pART-A (10x2=20Marks)

1. Distinguish synchronous and asynchronous sequential logic circ,:its.

2. List out the elements present in the ASM chart.

3. Defi.ne : Hazards

4. What.do you mean by race around condition ?

5. What do you mean by fault simulation ? Also its types.

6. Draw the circuit diagram for S-bit LFSR and its sequence.

7. Write down the features of FPGA.

B. List out the different types of Programming Logic Devices.

9. Write the Verilog code for half adder using gate level modelling.

10. Mention any four types of operators in Verilog HDL code'

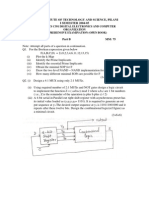

PART-B (5x13=65Marks)

11. a) I)esign a FSM for a single input and single output Mealy type FSM that produces

an output of 1 if an input sequence it detects either 110 or 101 pattern.

Overlapping sequences should be d"etected. (13)

(oR) wlvw.recentquestion paper,co;l

b) Design a serial adder Moore type FSM' (13)

47 031 I lllltilllililll[ffi ililtil llll

t2. a) Design a circuit that has an input w and output z, such that when the pulses

are applied to w, the output z is equal to 0 if the numbers of previously applied

pulses are even and.z is equai to 1 if the numbers of pulses are odd. (13)

(oR)

b) Design a counter which counts the number of pulses on an input line w. (13)

13. a) Find out the test pattern generation for the function F = A + B' C using ATPG

Algorithm. (13)

papet rGom

(oR) Vt!Tv,I..f ecentqueSrirjn

b) Generate the test vector and signature analysis for the circuit under test using

BIST algorithm. (13)

14. a) Explain about the structure of Xilinx 4000 CLB and IiO biocks with neat

diagram. (13)

(oR)

b) Considering the foliowing Boolean functions, design a combinational circuit

using a PAL. (13)

w(A, B, C, D) - Z(2,12, 13)

x(A, B, C, D) = I(7,8,9, 10, 11,1,2,13, 14, 15)

y(A, B, C, D) = I(0, 2,3,4,5,6,7,8, 10, 11, 15)

z(A, B, C, D) = I (1, 2, 8, 12, 73) .

1b. a) Design and. write the Verilog code for 4-bit Ripple carry adder using structural

ievel modelling. (13)

paper' com

(oR) wf'JW. recentquestion

b) Design and. write the Veriiog code for 16 to I Multiplexer using 4 to 1 multiplexer

circuit. (13)

PART _ C (15x1=15 Marks)

16. a) Design a modulo-6 counter, which counts in the sequences 0, t,2,3, 4,5,0, 1, ""

The counter counts the clock pulse if its enable input w, is equal to 1' Use D flip-

(15)

flops in your circuit.

(oR)

b) Design and write the Verilog cod.e for 8-bit ALU circuit which perfcrrms the basic

(15)

arithmetic and logical oper;tion.

You might also like

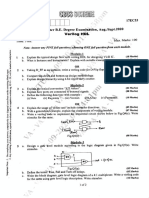

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- nov - dec 2018Document5 pagesnov - dec 2018Pandyselvi BalasubramanianNo ratings yet

- Bharath Niketan Engineering College: HoursDocument2 pagesBharath Niketan Engineering College: HourseeeNo ratings yet

- STLDDocument2 pagesSTLDANUPAMA PonnuNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Document19 pagesL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiNo ratings yet

- Vlsi Au QP2Document2 pagesVlsi Au QP2Jaikumar RajendranNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- 07af303 - Digital Integrated Circuits and Logical DesignDocument3 pages07af303 - Digital Integrated Circuits and Logical DesignChandru RamaswamyNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- 08AB303 - DIGITAL LOGIC CIRCUITSDocument3 pages08AB303 - DIGITAL LOGIC CIRCUITSChandru RamaswamyNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Samraj JebasinghNo ratings yet

- B.E./B.Tech. Degree Exams Question Paper for VLSI DesignDocument2 pagesB.E./B.Tech. Degree Exams Question Paper for VLSI DesignShri VarshaNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- 08AB303 DIGITAL LOGIC CIRCUITS_1Document3 pages08AB303 DIGITAL LOGIC CIRCUITS_1Chandru RamaswamyNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)rajkumarsac100% (1)

- 08AF302 - DIGITAL INTEGRATED CIRCUITS AND LOGIC DESIGNDocument4 pages08AF302 - DIGITAL INTEGRATED CIRCUITS AND LOGIC DESIGNChandru RamaswamyNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- 08AB303 DIGITAL LOGIC CIRCUITSDocument4 pages08AB303 DIGITAL LOGIC CIRCUITSChandru RamaswamyNo ratings yet

- Question Bank FDEDocument2 pagesQuestion Bank FDEroyal brotherNo ratings yet

- Nov Dec 2013Document6 pagesNov Dec 2013abdnazar2003No ratings yet

- Logic Design Jan 2010 ESDocument2 pagesLogic Design Jan 2010 ESPrasad C MNo ratings yet

- See Adld 2020Document2 pagesSee Adld 20201ms21ec132No ratings yet

- R3Fvle: & Etrr - )Document7 pagesR3Fvle: & Etrr - )sarveshNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- Ect203 Logic Circuit Design, December 2022Document2 pagesEct203 Logic Circuit Design, December 2022ShakiraNo ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- Eec-703 Vlsi Design 2012-13Document4 pagesEec-703 Vlsi Design 2012-13kd17209No ratings yet

- Electronics and Communication Engineering VI SemesterDocument2 pagesElectronics and Communication Engineering VI SemesterRamNo ratings yet

- EE8351 Iq 16 Marks PDFDocument7 pagesEE8351 Iq 16 Marks PDFdeepika senthilNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignVenkat ChadalavadaNo ratings yet

- Question Paper Code: X10348: Reg. NoDocument2 pagesQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNo ratings yet

- MCA (Revised) Term-End Examination - Une, 2409Document4 pagesMCA (Revised) Term-End Examination - Une, 2409ammanNo ratings yet

- Sathyabama: Register NumberDocument3 pagesSathyabama: Register NumberBoopalanElumalaiNo ratings yet

- End Semester Examination - April/May - 2017Document2 pagesEnd Semester Examination - April/May - 2017Shylu SamNo ratings yet

- Model Important Questions (1fffffffffffffffffffffffDocument2 pagesModel Important Questions (1fffffffffffffffffffffffinfinitywaysalwaysNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- Dica Question BankDocument4 pagesDica Question BankOmprakash KuswahaNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Ect206 Computer Architecture and Microcontrollers, June 2022Document2 pagesEct206 Computer Architecture and Microcontrollers, June 2022instapc0210No ratings yet

- Cse 205Document39 pagesCse 205sharminmin92No ratings yet

- Me2255 MJ 2011Document3 pagesMe2255 MJ 2011Anand DuraiswamyNo ratings yet

- DLC Model IDocument2 pagesDLC Model IEEE DEPTNo ratings yet

- MCS (S) Dec 2005Document46 pagesMCS (S) Dec 2005amritanshuuNo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Ect203 Logic Circuit Design, December 2021Document2 pagesEct203 Logic Circuit Design, December 2021instapc0210No ratings yet

- DR - NGP Institute of Technology Coimbatore - 48: Department of Cse & ItDocument3 pagesDR - NGP Institute of Technology Coimbatore - 48: Department of Cse & ItParandaman Sampathkumar SNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- VTU Question PapersDocument12 pagesVTU Question PapersQwertyNo ratings yet

- DSD Midsem PapersDocument14 pagesDSD Midsem PapersRanveerNo ratings yet

- Combinatorial Algorithms: For Computers and CalculatorsFrom EverandCombinatorial Algorithms: For Computers and CalculatorsRating: 4 out of 5 stars4/5 (2)

- Topics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationFrom EverandTopics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- From Microstructure Investigations to Multiscale Modeling: Bridging the GapFrom EverandFrom Microstructure Investigations to Multiscale Modeling: Bridging the GapDelphine BrancherieNo ratings yet

- 12th - Mid-Term-IPDocument5 pages12th - Mid-Term-IPPriyansh PatelNo ratings yet

- Orbit MCR Release Notes Rev AL - 9.2.2Document8 pagesOrbit MCR Release Notes Rev AL - 9.2.2David José Barrios ItriagoNo ratings yet

- HSUPA FDE ParameterDocument2 pagesHSUPA FDE ParameterAnonymous tQUMwABplTNo ratings yet

- Online Shopping WebsiteDocument33 pagesOnline Shopping WebsiteSatish Gaurav93% (14)

- Alcatel NMC Proxy Agent MibDocument7 pagesAlcatel NMC Proxy Agent MibMehdi NanterreNo ratings yet

- Lab Manual DSDocument52 pagesLab Manual DSGourav KhobreNo ratings yet

- ODI Uses Six Different Types of Knowledge ModulesDocument7 pagesODI Uses Six Different Types of Knowledge ModulesReddy seelam manoharNo ratings yet

- Zend Framework 2Document1,495 pagesZend Framework 2mititicu100% (1)

- SK720 ManualDocument43 pagesSK720 ManualrandyromNo ratings yet

- HTML Tags Complete ListDocument14 pagesHTML Tags Complete ListMoses GunnNo ratings yet

- (Junior Calculator System) : Software Requirement Specifications (SRS)Document34 pages(Junior Calculator System) : Software Requirement Specifications (SRS)John100% (3)

- User Guide For Mf5to6Document10 pagesUser Guide For Mf5to6Haili JiaNo ratings yet

- Ancel OBD Bluetooth User ManualDocument2 pagesAncel OBD Bluetooth User ManualFordiNo ratings yet

- Manual FlowStone Synthmaker en EspañolDocument272 pagesManual FlowStone Synthmaker en EspañolAmin0% (1)

- DWM Unit2Document65 pagesDWM Unit2Hansica MadurkarNo ratings yet

- Creating VOFM Custom Routine, Functionality Sam..Document24 pagesCreating VOFM Custom Routine, Functionality Sam..Sathish B SathishNo ratings yet

- Computer Systems Organization-Hardware-v3Document39 pagesComputer Systems Organization-Hardware-v3patrick rollodaNo ratings yet

- Tosca Questions AnswersDocument3 pagesTosca Questions AnswersboriskrekelNo ratings yet

- Gonzales-2015-An E-Learning Framework-Enhancing The Student Learning StyleDocument7 pagesGonzales-2015-An E-Learning Framework-Enhancing The Student Learning StyleDENNIS GONZALESNo ratings yet

- Boardsim UserefDocument1,985 pagesBoardsim UserefIoana FumorNo ratings yet

- Hardware Development Tools: 2009 Texas Instruments, All Rights ReservedDocument38 pagesHardware Development Tools: 2009 Texas Instruments, All Rights Reservedpra_zara2637No ratings yet

- Manual D2008fa G C PDFDocument38 pagesManual D2008fa G C PDFAk100% (1)

- (Q) How To Extract CPUID From Bricked A500 - Acer Iconia A500 - XDA ForumsDocument9 pages(Q) How To Extract CPUID From Bricked A500 - Acer Iconia A500 - XDA ForumsMihai MaziluNo ratings yet

- Moodle User Manual for UJ StudentsDocument14 pagesMoodle User Manual for UJ StudentsalexNo ratings yet

- Android Pull To Refresh Tutorial - TuteCentralDocument25 pagesAndroid Pull To Refresh Tutorial - TuteCentralAditya PabbarajuNo ratings yet

- Via Chipset Comparision - 20062003Document5 pagesVia Chipset Comparision - 20062003api-3760834No ratings yet

- DSP Project ProposalDocument6 pagesDSP Project ProposalMohsin IqbalNo ratings yet

- Module 1 Living in The IT EraDocument7 pagesModule 1 Living in The IT Erakvelez100% (2)

- Cspro Capi Getting StartedDocument16 pagesCspro Capi Getting StartedSADOUN SeNo ratings yet

- MIS Important-QuestionsDocument3 pagesMIS Important-QuestionsAmy AungNo ratings yet