Professional Documents

Culture Documents

Adv Comp Arch Dec2002

Uploaded by

api-3782519Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Adv Comp Arch Dec2002

Uploaded by

api-3782519Copyright:

Available Formats

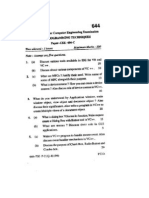

601

t B. E. (Computer Engg.) VIIth Semester Examination,

.

. December-2002

ADVANCE COMPUTER ARCHITECTURE Paper-

CSE-40 l-C

Time allowed: 3 hours Maximum Marks: 100

Note: Attempt any five questions . .•.

1. (a) What do you mean by micro-programming? Explain

vertical and horizontal micro-instructions. 10

(b) The logical address space in a computer consists of 128

segments. Each segment can have up to 32. pages of 4 k

words in each. Physical memory consists of 4 k blocks of

4 k words in each. Formulate the physical and logical

address formats. 10

2. (a) Compute the area in rbe with and without aspect mismatch

adjustment of a 32 KB direct mapped cache

. with 256 bit lines and 20-bit tag. 10

(b) Explain in brief the various phases in a processor

design project. 10

3. What do you mean by process management? Explain in brief

the following :

\:--,~';"'!"~'JI"'"!-(":",,,;,:.;,:"o;., .• :~.

( 2 ) (3)

4. (a) What do you mean by dynamic pipeline? Explain vari,)US (b) Assume a CBWA Cache with write (dirty line) buffer;

levels of dynamic pipei ine sophistication. find T . and T . , Tb .

m. miss c.mlSS usy

1 (c) Repeat the problem assuming both a dirty line buffer'

0

(b) WhLt is the effect of using buffers on the instructions and wrap-around load. 20

execution ? Discuss the design .)f a buffer. 10

7. (a) Describe different vector instructions a..nd operations

5. (a) Whnt is the basic design principie for Cache? Discuss with example. 1

various types of localities ... 10 0

(b) Develop the Gamma (y}-binomial-model of bypassed

(b) What do you mean by Cache-niapping ? Explain the set

vector memory behaviour. Deri ve the Yopt (no

a~sociative mapping scheme for cache with the help of a

contention). 10

. iiagram. 10

8. (a) Describe the Cache coherence problem. Discuss the

6. Assume ,: CBWA cache has a miss rate of 0.03 misses per

writing mechanism for Cache to make available the latest

reference with a dirty line ratio of 0.5 . This Cache is used copy of data in Cache. 10 (b) Discuss various mechanisms for

with a pro ::essor that makes a referenc ,:; every 40 ns. (mean), sharing memory

assume the Cache is configured with: among multiple processes. 10

Cache line size = 16B

Phys· cal word size = 4 B

the meme ry is configured as

T = 120 llS,T =l00ns,Tbu =40ns,m=2.

a c s

'

(a) Assu:ne the cache writes a dirty line before reading lines !

(unbuffered) and that an entire line must be

transferred to the processor before it resumes ...............................................' ...• ", .. "'.,,~'""" , ..••• """~;_.j~;.;4~$".;,;,

..

.• .• •. " _.', ..••.• '~ ~- ••••• ",'- "'> ~ .. ~ -~~ ~.,:.r:~' .,".'"-,...,, ~';"""";$."ii. ••.. ~ ••.• Jtilj-~ ••.•. '1>' ""'v'-"'- ~

lit . "'Ln-. ._.!.._~.~

"'-_. --- •. 1

You might also like

- MCA SyllabusDocument54 pagesMCA Syllabusapi-3782519100% (3)

- Discrete Struc Dec 2002Document2 pagesDiscrete Struc Dec 2002api-3782519No ratings yet

- Discrete Struc May 2004Document2 pagesDiscrete Struc May 2004api-3782519No ratings yet

- MCA SyllabusDocument3 pagesMCA Syllabusapi-3782519100% (4)

- BDocument120 pagesBapi-3782519100% (3)

- BBA SyllabusDocument81 pagesBBA Syllabusapi-3782519100% (11)

- BCA SyllabusDocument55 pagesBCA Syllabusapi-378251973% (11)

- Mtech3rdsem SyllabusDocument3 pagesMtech3rdsem Syllabusapi-3782519No ratings yet

- BCA SyllabusDocument3 pagesBCA Syllabusapi-3782519100% (2)

- M SC - SyllabusDocument2 pagesM SC - Syllabusapi-3782519No ratings yet

- Mca SyllabusDocument24 pagesMca Syllabusapi-3782519No ratings yet

- BE IST YEAR COMMON-syllabusDocument34 pagesBE IST YEAR COMMON-syllabusapi-3782519No ratings yet

- MBA SyllabusDocument4 pagesMBA Syllabusapi-3782519100% (1)

- Mtech1stsem SyllabusDocument4 pagesMtech1stsem Syllabusapi-3782519No ratings yet

- B.tech It SyllabusDocument102 pagesB.tech It Syllabusapi-3782519100% (2)

- B.tech Cse SyllabusDocument121 pagesB.tech Cse Syllabusapi-3782519100% (20)

- Sys Prog Dec 2002Document2 pagesSys Prog Dec 2002api-3782519100% (1)

- Software Engg 3Document3 pagesSoftware Engg 3api-3782519No ratings yet

- Visual Programming Techniques1Document2 pagesVisual Programming Techniques1api-3782519No ratings yet

- Visual Programming TechniquesDocument2 pagesVisual Programming Techniquesapi-3782519No ratings yet

- Software EnggDocument1 pageSoftware Enggapi-3782519No ratings yet

- Theory of ComputeationDocument2 pagesTheory of Computeationapi-3782519No ratings yet

- Theory of Automata and ComputationDocument2 pagesTheory of Automata and Computationapi-3782519No ratings yet

- APGDCA SyllabusDocument1 pageAPGDCA Syllabusapi-3782519No ratings yet

- Visual Prog Techniques1Document2 pagesVisual Prog Techniques1api-3782519No ratings yet

- TH of ComputationDocument2 pagesTH of Computationapi-3782519No ratings yet

- Software Engg2Document2 pagesSoftware Engg2api-3782519No ratings yet

- Software Engg1Document3 pagesSoftware Engg1api-3782519No ratings yet

- TH of Computation Dec 2002Document3 pagesTH of Computation Dec 2002api-3782519No ratings yet

- System ProgrammingDocument2 pagesSystem Programmingapi-3782519No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- AI Enabled Adaptive Learning Systems A Sys - 2021 - Computers and Education ArDocument12 pagesAI Enabled Adaptive Learning Systems A Sys - 2021 - Computers and Education AryaestaNo ratings yet

- Restaurant Management SystemDocument33 pagesRestaurant Management SystemSatwik Naradasi85% (176)

- Physics Masters Dissertation ExampleDocument8 pagesPhysics Masters Dissertation ExampleWebsitesToTypePapersSingapore100% (1)

- Mukularanyam English School: A Project Report ON Travel Agency Management SystemDocument71 pagesMukularanyam English School: A Project Report ON Travel Agency Management Systemindia cybercafeNo ratings yet

- 8051 and Advanced ProcessorDocument119 pages8051 and Advanced ProcessorAamir MehmoodNo ratings yet

- Snapshot Error During Hyper-V Backup JobDocument2 pagesSnapshot Error During Hyper-V Backup Jobnk0876No ratings yet

- FW Monitor Cheat SheetDocument2 pagesFW Monitor Cheat SheetnetzsheriffNo ratings yet

- Attunity Replicate 5.5 Release Notes - August 2017Document26 pagesAttunity Replicate 5.5 Release Notes - August 2017nidhib6666No ratings yet

- Auditd Configuration On Linux To Track Activity of UsersDocument3 pagesAuditd Configuration On Linux To Track Activity of UsersBabatunde AdebayoNo ratings yet

- Use Case - PowerDocument2 pagesUse Case - PowerMUHAMMADNo ratings yet

- SQL - The Ultimate Beginner - S Guide To Learn SQL Programming Step-by-StepDocument121 pagesSQL - The Ultimate Beginner - S Guide To Learn SQL Programming Step-by-StepAndi 01100% (1)

- Tutorial 4Document2 pagesTutorial 4Jaeson SisonNo ratings yet

- Base Sas Interview Questions by TopicDocument15 pagesBase Sas Interview Questions by TopicSneha NagaruruNo ratings yet

- Field List Icons in Power BI Desktop - POWER BI WITH PRASADDocument3 pagesField List Icons in Power BI Desktop - POWER BI WITH PRASADtynoe geeNo ratings yet

- Msbi SsisDocument164 pagesMsbi SsisSubrahmanyam SudiNo ratings yet

- TAO - SSW - Assessment - PATEL - HARSH - 20211001 - Rev0.1Document186 pagesTAO - SSW - Assessment - PATEL - HARSH - 20211001 - Rev0.1khushbu HasanNo ratings yet

- Research Methods OverviewDocument16 pagesResearch Methods OverviewFatema ShoshiNo ratings yet

- 220 - HRD - APEC Closing The Digital Skills Gap Report - RevDocument41 pages220 - HRD - APEC Closing The Digital Skills Gap Report - Revokky2006No ratings yet

- The Effectiveness of Data Processors in Correlation To GDPRDocument12 pagesThe Effectiveness of Data Processors in Correlation To GDPROliver SmithNo ratings yet

- Final - DBMS UNIT-3Document170 pagesFinal - DBMS UNIT-3Sunil KumerNo ratings yet

- 11 Create Netcdf PythonDocument22 pages11 Create Netcdf PythonAli JalalyNo ratings yet

- Sap Bw4hana Content Add On enDocument936 pagesSap Bw4hana Content Add On enTiago Carrilho100% (4)

- INFORMS Job Task Analysis 2012 2019Document16 pagesINFORMS Job Task Analysis 2012 2019Francisco GalindoNo ratings yet

- Electronic Evidence Cases (As Listed in TheDocument11 pagesElectronic Evidence Cases (As Listed in Themina villamorNo ratings yet

- Catalogo Cartas Atualizacao 30setembro2023Document174 pagesCatalogo Cartas Atualizacao 30setembro2023joaosaraiva1307No ratings yet

- HCM Extracts Worked ExampleDocument10 pagesHCM Extracts Worked ExampleGoutamNo ratings yet

- Gis and Information SystemsDocument9 pagesGis and Information SystemsVaishnavi ChockalingamNo ratings yet

- Databases 2 Course MaterialDocument13 pagesDatabases 2 Course MaterialcyliteNo ratings yet

- File Handling in Python: Open, Read, Write & CountDocument24 pagesFile Handling in Python: Open, Read, Write & CountAman JainNo ratings yet

- MySQL History and FeaturesDocument13 pagesMySQL History and FeaturesRachita RamanNo ratings yet