Professional Documents

Culture Documents

Puertas de Entrada y Salida

Uploaded by

kapri1001Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Puertas de Entrada y Salida

Uploaded by

kapri1001Copyright:

Available Formats

ITSS - Puertas de Entrada y Salida

PUERTAS DE ENTRADA Y SALIDA

Paola Lizzet Esparza Godoy

e-mail: lizzetpao1991@hotmail.com RESUMEN: en este capitulo se encuentra claramente

especificado la funcionalidad de una entra o salida de las puertas del dsPIC30F, sus caracteristias y configuraciones. PALABRAS registros. CLAVE: latch, entrada, salida, est configurada como entrada o salida. Si el bit TRIS asociado a una patita de E/S 1, entonces la patita estar configurada como entrada. En caso contrario, si vale 0, la patita estar configurada como salida. Todas las patitas de las puertas estn configuradas por defecto como entradas, siendo dicho valor el que toma despus de un Reset.

2.2 LOS REGISTROS PORT

Los datos existentes en las patitas de E/S son accedidos a travs del registro PORTx. Mediante una lectura del registro PORTx se lee el valor que soportan o reciben las patitas de E/S, mientras que una escritura en dicha puerta escribe el valor en el registro latch correspondiente. Muchas instrucciones, tales como BSET y BCLR, son operaciones de lectura, modificacin y escritura. Por tanto, escribir en una puerta implica que sus patitas son ledas, se modifique su valor y despus se escriba el latch de datos. Se debe tener precaucin cuando se utiliza instrucciones de lectura y escritura en los registros PORTx, especialmente cuando algunas patitas de E/S asociadas al mismo se configuran como entradas. Si una patita de E/S configurada como entrada, transcurrido un tiempo se cambia a salida, puede producir un valor de salida inesperado. Este efecto ocurre porque una instruccin de lectura y escritura lee el valor instantneo de la patita de entrada y lo carga en el latch de datos.

1 INTRODUCCIN

Las puertas de entrada y salida son los conjuntos de patitas que soportan las seales que entran y salen del dispositivo. El nmero y tipo de las puertas dependen del modelo dsPIC30F que se trate. En general, cada puerta de E/S consta de ocho patitas. Todas las patitas del dispositivo, salvo VDD, VSS, MCLR# y OSC1/CLKI se reparten entre las seales que requieren los perifricos y las lneas de E/S de propsito general. Las puertas de propsito general de E/S son las que permiten que el sdPIC30F supervise y controle otros dispositivos externos. La mayor parte de las patitas de E/S soportan varias funciones alternativas multiplexadas en el tiempo. Por lo general, cuando una patita se dedica a un perifrico no puede emplearse al mismo tiempo como patitas de propsito general.

2.2 LOS REGISTROS LAT

El registro LATx asociado a una patita de E/S elimina los problemas que puedan ocurrir con las instrucciones de lectura, modificacin y escritura. Una lectura del registro LATx devuelve los valores guardados en los registros cerrojos de salida de la puerta, E/S el lugar de los valores de las patitas de E/S. Una operacin de lectura-modificacin-escritura en el registro LAT asociada a una puerta de E/S, evita la posibilidad de escribir los valores de la patita de entrada en los latch de la puerta. Una escritura en los registros LATx tiene el mismo efecto que hacerlo en el registro PORTx. Las diferencias entre los registros PORT y LAT son las siguientes: Una escritura en el registro PORTx escribe el valor de los datos en el registro cerrojo de la puerta. Una escritura en el registro LATx escribe el valor de los datos en el registro cerrojo de la puerta. Una lectura del registro PORTx lee el valor de los datos de las patitas de E/S. Una lectura del registro LATx lee el valor de los datos guardados en el registro cerrojo de la puerta.

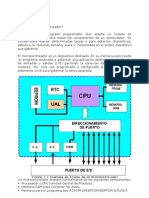

2 REGISTROS DECONTROL DE LAS PUERTAS DE E/S

Todas las puertas de e/s tienen tres registros directamente asociados con la operacin de la puerta, donde <<x>> es la letra que referencia la puerta particular de E/S. TRISx: Registro de la direccin de los datos que determina si las lneas son entrada o salida. PORTx: Registro de la puerta de E/S que contiene el valor de las lneas de entrada. LATx: Registro cerrojo o latch de E/S que almacena el valor que sacan las lneas de salida. Cada patita de E/S en el dispositivo dispone de un bit directamente asociado en cada uno de los registros TRIS, PORT y LAT.

2.1 LOS REGISTROS TRIS

Los bits del registro TRISx son los que determinan si cada patita asociada de lnea de E/S correspondiente

ITSS - Puertas de Entrada y Salida

.

Cuando un modelo de dispositivo no dispone en su arquitectura de una puerta determinada se desactivan sus registros y datos asociados.

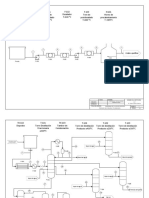

4 DESCRIPCION DE LAS PUERTAS

El numero de puertas de patitas de E/S disponibles para un dispositivo dado depende e la variante del mismo, porque es posible que para un dispositivo concreto no estn implementados algunos de los registros de control de las puertas que se conectan. En la siguiente figura se muestra un modelo dsPIC30F de 80 patitas, con gran cantidad de funciones implementadas y multiplexadas en cada una de sus patitas.

3 MULTIPLEXACIN DE LAS SEALES DE LOSPERIFERICOS

Cuando se habilita un perifrico todas las patitas que tiene asociadas para soportar sus seales se desactivan como patitas de E/S de propsito general. Por eso la mayora de las patitas de E/S son multifuncin y pueden soportar distintas funciones multiplexadas en el tiempo. Los datos del buffer de salida del perifrico y las seales de control se conectan a una pareja de multiplexores. Estos multiplexores seleccionan si es el perifrico o la puerta asociada quien toma el control. Nota: Para utilizar las patitas PORTB como E/S digitales, los bits correspondientes al registro ADPCFG deben valer 1, incluso si el modulo conversor analgico/digital se encuentra desconectado.

3.1 MULTIPLEXACION DE MLTIPLES SEALES DE PERIFERICOS

Algunos dispositivos dsPIC30F, especialmente los que tienen un nmero pequeo de patitas de E/S, tienen multiplexadas diversas funciones de los perifricos sobre cada una de ellas. El nombre de la patita de E/S se elige de tal manera que el usuario pueda determinar fcilmente la prioridad de las funciones que se les ha asignado a las mismas. Control de patitas de entrada por software Algunas de las funciones asignadas a una patita de E/S son funciones de entrada que toman el control del <<driver>> de salida de la propia patita. Un ejemplo de un perifrico que utiliza una funcin de este tipo es el modulo de captura de entrada. Los siguientes perifricos permiten que sus patitas de entrada sean controladas manualmente a travs de los registros PORT. Patitas de interrupcin externas. Patitas de entrad de reloj de un Timer Patitas de captura de entrada. Patitas de PWM Fault.

4.1 DIAGRAMA DEL CONEXIONADO

A continuacin se muestra las puertas mas importantes con una breve descripcin de su funcionamiento, asi como la misin de las seales, como las de alimentacin y de reloj que conforman el dsPIC. Alimentacin VDD: Esta patita sirve para el suministro de voltaje positivo de alimentacin para la lgica y las patitas de E/S del dispositivo. VSS: Esta patita se emplea como voltaje de referencia (GND) del dispositivo. VREF+ (E): Voltaje positivo de referencia para seales analgicas. VREF- (E): Voltaje negativo de referencia para seales analgicas. AVDD: Suministro de alimentacin positiva para el modulo analgico. AVSS: Suministro de alimentacin negativa para el mdulo analgico. LVDIN (E): Entrada del detector de voltaje bajo. Seal de Reset MCLR#: entrada Master Clear Reset. Es una lnea activa para el nivel bajo que produce un Reset del dispositivo. Seales digitales de E/S

La mayor parte de los perifricos de comunicacin serie, cuando estn activos, toman el control absoluto de las patitas de E/S para que las que estn asociadas con el perifrico no puedan ser afectadas atreves de los registros PORT. Estos perifricos son los siguientes: SPI. I2C. DCI. UART. CAN.

ITSS - Puertas de Entrada y Salida

. RAx, RBx, RCx, RDx, RFx y RGx (E/S): son

U1TX (S): Transmisor del mdulo UART1 U2RX (E): Receptor del mdulo U2TX (X): Transmisor del mdulo UART2 U1ARX (E): Receptor alternativo del mdulo UART1 U1ATX (S): Transmisor alternativo del mdulo UART1. Seales de Interrupcin INTx (E): Lneas de entrada para peticin de las interrupciones. Seales de Captura de la Entrada ICx (E): Lneas de entrada que se emplean para la captura de entradas. Seales de Comparacin OCFA: Lneas de entrada que compara la entrada Fallo A OCFB: Lneas de entrada que compara la entrada Fallo B. OSCx (S): Es una lnea de salida del mdulo comparador. Seales de Propagacin del Circuito de Entrada Serie PGD (E/S): Lnea de entrada/salida de los datos de grabacin. PGC (S): Lnea de salida de impulsos de reloj para la programacin del circuito. 5 REGISTROS DE NOTIFICACIN DE CAMBIO DE ESTADO (CN) Las patitas de notificacin de estado (CN) proporcionan a los dispositivos dsPIC30F la capacidad de generar peticiones de interrupcin al procesador en respuesta a un cambio del estado en las patitas de entrada seleccionadas. Se pueden seleccionar hasta 24 patitas de entrada para generar interrupciones de CN. El nmero total de entradas CN disponibles depende del modelo de dispositivos dsPIC30F seleccionado. 6 FUNCIONAMIENTO EN LOS MODULOS SLEEP E IDLE El modulo continua funcionando durante los mdulos Sleep e Idle. Si una de las patitas CN activadas cambia de estado, entonces el bit de estado CNIF (IFSO<15>) se activara. Al activarse el dispositivo despierta de modo sleep o del modo Idle y continuar normalmente su funcionamiento. Si el nivel de prioridad de la interrupcin CN asignado es igual o menor que el nivel actual de la prioridad de la CPU, la ejecucin del dispositivo continuara desde la instruccin inmediatamente despus de la instruccin SLEEP o la IDLE. Si, por el contrario, el nivel asociado a la interrupcin es mayor que el nivel actual de la prioridad de la CPU, la ejecucin continuar desde la direccin del vector de interrupcin del CN correspondiente.

lneas digitales tanto de entrada como salida y se asocian con sus respectivas puertas. Seale analgicas de entrada ANx (E): patitas por las que se introduce seale analgicas, de las cuales AN0 y AN1 se emplean para entrada de datos y aplicacin de una seal de reloj en la fase de grabacin del dispositivo. Seales de reloj CLKI (E): Entrada de reloj externo siempre asociada con la funcin de la patita OSC1. CLKO (S): Salida de reloj en los modos RC y EC, que se conectan al resonador de cristal. TXCK (E): Entrada de reloj externo TimerX. Seales del oscilador OSC1 (E): Entrada del cristal oscilador OSC2 (S): Salida del cristal oscilador conectada al resonador del cristal SOSCI (E): Entrada del oscilador de baja potencia. SOSCO (S): Salida del oscilador de baja potencia. Seales de notificacin de cambio CNx: Estas patitas son las entradas de notificacin de cambio de estado y se pueden programar por software para trabajar con pullup. Seales de comunicacin con interfaz conversor de datos (ICD) C0FS: Patita de sincronizacin del marco de ICD. CSCK: Patita para la E/S del reloj serie de ICD. CSDI: Patita de entrada de datos serie de ICD. CSDO: Patita de salida de datos serie ICD. EMUD-EMUD3: patita de E/S de datos para el canal ICD EMUC-EMUC3: Patitas de entrada de reloj para el canal ICD. Seales para el bus CAN C1RX (E): patita de recepcin del bus CAN1 C1TX (S): patita de recepcin del bus CAN1 C2RX (E): patita de recepcin del bus CAN2 C2RX (S): patita de recepcin del bus CAN2 Seales de para SPI SCKx (E/S): Entrada o salida del reloj sncrono serie para SPIX SDIx(E): lnea de entrada de datos SPIX SDOx(S): lnea de salida de datos SPIX SSx(E): lnea de sincronizacin con el esclavo SPIX Seales para el bus I2 C SCL (E/S): lnea de entrada y salida del reloj sncrono serie para I2C. SDA(E/S): lnea de entrada y salida de datos sncrono serie para I2C. Seales para transmisin UART U1RX (E): Receptor del mdulo UART1

BIBLIOGRAFIA:

ITSS - Puertas de Entrada y Salida

.

Microcontroladores avanzados dsPIC, controladores digitales de seales arquitectura programacin y aplicaciones, capitulo 17, la memoria de datos.

You might also like

- Prácticas de redes de datos e industrialesFrom EverandPrácticas de redes de datos e industrialesRating: 4 out of 5 stars4/5 (5)

- Puertas de Entrada y SalidaDocument3 pagesPuertas de Entrada y Salidakapri1001100% (1)

- CAPITULOIDocument27 pagesCAPITULOIAland Bravo VecorenaNo ratings yet

- C4 PuertosESParalelos PDFDocument66 pagesC4 PuertosESParalelos PDFMi KelNo ratings yet

- Micro Lab1Document9 pagesMicro Lab1Alex MercerNo ratings yet

- S04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16Document41 pagesS04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16renatto2089No ratings yet

- Programacion de Entradas y Salidas de Un MicrocontroladorDocument6 pagesProgramacion de Entradas y Salidas de Un MicrocontroladorMiguel Angel AburtoNo ratings yet

- Automatizacion Con PlcsDocument129 pagesAutomatizacion Con PlcsPreceptor SomaNo ratings yet

- Interfaces de E/S básicas y sus instruccionesDocument72 pagesInterfaces de E/S básicas y sus instruccionesJorge Gianotti HidalgoNo ratings yet

- Tipos y Partes de Un PLCDocument48 pagesTipos y Partes de Un PLCPatricia PerlacioNo ratings yet

- Automatizacion de Sistemas de Manufactura Sesion 3 PLC HornerDocument102 pagesAutomatizacion de Sistemas de Manufactura Sesion 3 PLC HornerCarlos PelaezNo ratings yet

- PICDocument53 pagesPICRosemberg Torres DominguezNo ratings yet

- Interfaces de Entrada y Salida de Un PLCDocument26 pagesInterfaces de Entrada y Salida de Un PLCGãtx JâčkNo ratings yet

- Para Que Nuestro Pic Funcione FísicamenteDocument7 pagesPara Que Nuestro Pic Funcione FísicamenteAna Suggey100% (1)

- Tutorial PIC16F877A (Algunas Mejoras)Document26 pagesTutorial PIC16F877A (Algunas Mejoras)rodrick7790% (10)

- Instalación de sistemas de automatización con PLCDocument70 pagesInstalación de sistemas de automatización con PLCGilberto MottoNo ratings yet

- Microprocesador Intel 8085: arquitectura, componentes e interrupcionesDocument11 pagesMicroprocesador Intel 8085: arquitectura, componentes e interrupcionesADRIÁN DOMÍNGUEZ CALVONo ratings yet

- Introduccion A Los MicroDocument9 pagesIntroduccion A Los MicroPabloNo ratings yet

- 4-001contador ProgramableDocument11 pages4-001contador ProgramableDiego LaviniNo ratings yet

- Unidad 1 - IntroduccionDocument35 pagesUnidad 1 - IntroduccionJavier CardenasNo ratings yet

- Configuración de DsPIC30F4011Document10 pagesConfiguración de DsPIC30F4011randdyNo ratings yet

- Tarea 6.1.francisco Elio Cerino de La CruzDocument18 pagesTarea 6.1.francisco Elio Cerino de La CruzFranciscoNo ratings yet

- PLC TSX17Document12 pagesPLC TSX17Alex Asdasd MC100% (1)

- PLC TSX17Document12 pagesPLC TSX17FredyNo ratings yet

- El Microprocesador 8085Document11 pagesEl Microprocesador 8085neptuno97No ratings yet

- Curso Controladores Lógicos PLC ModiconDocument222 pagesCurso Controladores Lógicos PLC ModiconJuanelo HernándezNo ratings yet

- Sesion11-Comunicación Serial 2021-n Sesion11Document39 pagesSesion11-Comunicación Serial 2021-n Sesion11Johan Christhofer Armas ValenciaNo ratings yet

- Laboratorio 4 TemporizadoresDocument24 pagesLaboratorio 4 Temporizadorescarlos mgNo ratings yet

- Qué Es Un PLCDocument9 pagesQué Es Un PLCCarlos Montalvo MarinNo ratings yet

- Clase 01 - PuertosDocument10 pagesClase 01 - PuertosElvys EmersonNo ratings yet

- Introducción A Los Controladores Logicos ProgramablesDocument38 pagesIntroducción A Los Controladores Logicos ProgramablesGeorge LizarragaNo ratings yet

- 3-Gestion de MemoriaDocument43 pages3-Gestion de MemoriaPedro CasanovaNo ratings yet

- UNSAM SPD 08 ES Interrupciones DMA PDFDocument58 pagesUNSAM SPD 08 ES Interrupciones DMA PDFKenton OrtizNo ratings yet

- PuertosDocument21 pagesPuertosErick BravoNo ratings yet

- Tutorial PIC16F877A Algunas MejorasDocument26 pagesTutorial PIC16F877A Algunas MejorasJose Luis Sovero AstoamanNo ratings yet

- EXCELENTE Curso PLC ModiconDocument222 pagesEXCELENTE Curso PLC Modiconyahyamoummou100% (1)

- Informe Poleas y BandasDocument15 pagesInforme Poleas y BandasChurosLocosNo ratings yet

- MICROCONTROLADORES PIC16F690Document13 pagesMICROCONTROLADORES PIC16F690Carlos RomoNo ratings yet

- Foro TematicoDocument14 pagesForo TematicoSandra Sosa PérezNo ratings yet

- Introducción A Los MicroprocesadoresDocument10 pagesIntroducción A Los MicroprocesadoresBibiano Cortés ToledoNo ratings yet

- Introduccion A Los PLCDocument23 pagesIntroduccion A Los PLCJuan Suarez TapiaNo ratings yet

- Practica 15 RelojDocument12 pagesPractica 15 RelojEmmanuel GonzalezNo ratings yet

- Memoria 24LC512 Con Interfaz I2CDocument23 pagesMemoria 24LC512 Con Interfaz I2CRay ValecillosNo ratings yet

- Microcontrolador PIC18F2550Document12 pagesMicrocontrolador PIC18F2550Franco Quispe ClementeNo ratings yet

- Teoria 82c55aDocument6 pagesTeoria 82c55aErick Moreno100% (2)

- Descripcion Pic 16F877ADocument9 pagesDescripcion Pic 16F877AAndres Camilo RubianoNo ratings yet

- PLC S7-300 MódulosDocument6 pagesPLC S7-300 MódulosMiguel A. MartínNo ratings yet

- Descripción Del CircuitoDocument7 pagesDescripción Del CircuitoJavier SarangoNo ratings yet

- LE002-Introduccion A Los MicrocontroladoresDocument296 pagesLE002-Introduccion A Los MicrocontroladoresDorian HidalgoNo ratings yet

- Micro Control Adores PicDocument28 pagesMicro Control Adores PicAntonio MartínezNo ratings yet

- Instructivo Control de Un Motor Trifasico PLCDocument56 pagesInstructivo Control de Un Motor Trifasico PLCDarwin Jesús Arela QuispeNo ratings yet

- Curso Basico PLCDocument49 pagesCurso Basico PLCSaul Garcia AguilarNo ratings yet

- Laboratorio 4 Introduccion Al Manejo y Programacion de PLC PDFDocument16 pagesLaboratorio 4 Introduccion Al Manejo y Programacion de PLC PDFMiltonNo ratings yet

- Laboratorio 4 Introduccion Al Manejo y Programacion de PLC PDFDocument16 pagesLaboratorio 4 Introduccion Al Manejo y Programacion de PLC PDFAnonymous HbgFhBANo ratings yet

- Modulos PLCDocument9 pagesModulos PLCArtz MosaresNo ratings yet

- 100 circuitos de shields para arduino (español)From Everand100 circuitos de shields para arduino (español)Rating: 3.5 out of 5 stars3.5/5 (3)

- Xavier Aldemar Jumbo Sarango: 1. Introduccion Al Modulo Can 1.3 Formato de MensajeDocument8 pagesXavier Aldemar Jumbo Sarango: 1. Introduccion Al Modulo Can 1.3 Formato de Mensajekapri1001No ratings yet

- Modulos I2C y DCI - PaoDocument6 pagesModulos I2C y DCI - PaoPaola EsparzaNo ratings yet

- PWMDocument7 pagesPWMkapri1001No ratings yet

- Modulo de Captura de EntradaDocument3 pagesModulo de Captura de Entradakapri1001No ratings yet

- Modulos I2c y DciDocument5 pagesModulos I2c y Dcikapri1001No ratings yet

- Tipos de RuidoDocument6 pagesTipos de Ruidokapri1001No ratings yet

- Modulacion de Simple Banda Lateral (SSB)Document3 pagesModulacion de Simple Banda Lateral (SSB)kapri1001No ratings yet

- Modulos I2C y DCI - PaoDocument6 pagesModulos I2C y DCI - PaoPaola EsparzaNo ratings yet

- Conversores Ad de 10 y 12 BitsDocument8 pagesConversores Ad de 10 y 12 Bitskapri1001No ratings yet

- Tipos de RuidoDocument6 pagesTipos de Ruidokapri1001No ratings yet

- Relacion Señal A RuidoDocument4 pagesRelacion Señal A Ruidokapri100189% (9)

- Tipos de RuidoDocument6 pagesTipos de Ruidokapri1001No ratings yet

- Puertas de Entrda y SalidaDocument3 pagesPuertas de Entrda y Salidakapri1001No ratings yet

- Grabacion de Las FLASH y EEPROMDocument7 pagesGrabacion de Las FLASH y EEPROMkapri1001No ratings yet

- Paper WestherDocument3 pagesPaper Westherkapri1001No ratings yet

- SeebeckDocument5 pagesSeebeckJacob García NegreNo ratings yet

- Brazo RoboticoDocument42 pagesBrazo Roboticokapri1001No ratings yet

- Musgos y Briofitas en EcuadorDocument25 pagesMusgos y Briofitas en Ecuadorkapri1001No ratings yet

- Sistemas DiscretosDocument3 pagesSistemas DiscretosXavi JumboNo ratings yet

- AnhidridosDocument4 pagesAnhidridosKevin LopezNo ratings yet

- Ejemplo LonMakerDocument17 pagesEjemplo LonMakerbambizNo ratings yet

- Provisoria: BOSCH Valores de Comprobación EP, Equipo de Inyección DieselDocument1 pageProvisoria: BOSCH Valores de Comprobación EP, Equipo de Inyección DieselFabi MontefioriNo ratings yet

- Lección 1Document20 pagesLección 1Angelica GómezNo ratings yet

- Ingenieria de Transito en VenezuelaDocument9 pagesIngenieria de Transito en Venezuelagabriela galindezNo ratings yet

- Bal - 13300-03-10 LTM 1200 - 1Document999 pagesBal - 13300-03-10 LTM 1200 - 1francisco caroselliNo ratings yet

- 12 Personajes en Busca de PsiquiatraDocument2 pages12 Personajes en Busca de Psiquiatraelpadrinno4100% (1)

- Procedimiento para Mantenimiento PreventivoDocument7 pagesProcedimiento para Mantenimiento PreventivoJorge VillacisNo ratings yet

- Pelco CM6700 Bfi Optilas Manual (Espanol)Document83 pagesPelco CM6700 Bfi Optilas Manual (Espanol)Joaquin BlancoNo ratings yet

- Frederick Winslow Taylor, Resumen de Su TeoriaDocument20 pagesFrederick Winslow Taylor, Resumen de Su TeoriaSantiagoNo ratings yet

- TDR Odel ArtesaniaDocument84 pagesTDR Odel Artesaniaruth yisela colque surco100% (1)

- Telefonos Meridian Serie 3900Document166 pagesTelefonos Meridian Serie 3900caperolNo ratings yet

- Autodata Renault Laguna Motor K4M-720Document4 pagesAutodata Renault Laguna Motor K4M-720Irving Alexander RujanoNo ratings yet

- Pci - Cetpro-San Antonio de Padua - 2017-2019 - CorregidoDocument69 pagesPci - Cetpro-San Antonio de Padua - 2017-2019 - Corregidoitogamy93% (15)

- Disparo DC Con SCRDocument4 pagesDisparo DC Con SCRLuigi875421100% (1)

- Informe de PPDocument2 pagesInforme de PPJorge Wilder Bazán LópezNo ratings yet

- Sonoras Calculos FinalizadosDocument5 pagesSonoras Calculos FinalizadosLuis Alexander EPNo ratings yet

- Tutorial. Crea Un Tornado Con Autodesk MayaDocument21 pagesTutorial. Crea Un Tornado Con Autodesk MayaJuan RamónNo ratings yet

- Diagrama de Refinación de PetroleoDocument10 pagesDiagrama de Refinación de PetroleoAndreyNo ratings yet

- Mantenimiento Basado en La CondiciónDocument8 pagesMantenimiento Basado en La CondiciónJean Piere Chamorro TorresNo ratings yet

- Procedimiento para Demoliciones Julio SalasDocument4 pagesProcedimiento para Demoliciones Julio SalasXimena Andrea Salas SalasNo ratings yet

- Estudio Impacto Ambiental Proyecto La MoralejaDocument177 pagesEstudio Impacto Ambiental Proyecto La MoralejaJoffre Enrique Contento100% (1)

- Fase 5 - Evaluacion de SoftwareDocument44 pagesFase 5 - Evaluacion de SoftwarehgerardplNo ratings yet

- Adan Y Eva XXI PDFDocument13 pagesAdan Y Eva XXI PDFHansel MontejoNo ratings yet

- Practica Semaforo - PLCDocument5 pagesPractica Semaforo - PLCHunter ZIINo ratings yet

- Cabezón de Vault-Tec - El Refugio - FANDOM Powered by WikiaDocument3 pagesCabezón de Vault-Tec - El Refugio - FANDOM Powered by WikiaMónica Fernández EnríquezNo ratings yet

- Leica Absolute Tracker AT402 Brochure EsDocument16 pagesLeica Absolute Tracker AT402 Brochure EstheflamebearerNo ratings yet

- Firewalls e IptablesDocument34 pagesFirewalls e IptablesCristian Alejandro Vergara FariasNo ratings yet

- EC-062 Pantoscopio PDFDocument1 pageEC-062 Pantoscopio PDFRichard PerezNo ratings yet

- Catalago Eslingas de Cable de Acero Especiales Fajas de CablesV1Document1 pageCatalago Eslingas de Cable de Acero Especiales Fajas de CablesV1Camilo Andrés Ibarra SánchezNo ratings yet