Professional Documents

Culture Documents

Digital (Logic Gates)

Uploaded by

Bibin LeeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital (Logic Gates)

Uploaded by

Bibin LeeCopyright:

Available Formats

Nguyen Thanh Kien

Department of Computer Engineering

Faculty of Information Technology

Hanoi University of Technology

Digital Logic Design

Page 2

About

Author: Nguyen Thanh Kien

Office:

Department of Computer Engineering

Faculty of Information Technology

Hanoi University of Technology

Mobile: +84 983 588 135

Email: kiennt-fit@mail.hut.edu.vn

thanhkien84@yahoo.com

ftp://dce.hut.edu.vn/kiennt

Page 3

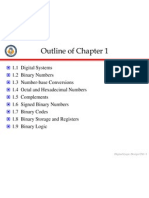

Content

1. Introduction

2. Function Minimization Methods

3. Larger Combinational Systems

4. Sequential Systems

5. Hardware Design Languages

Page 4

Acknowledge

The following materials are used as reference for this slide:

Logic Circuits slide, Dr. Trinh Van Loan.

Introduction to Logic Design, 2nd Ed, Alan B. Marcovitz, Mc. Graw

Hill,2005

Foundation of Digital Logic Design, G.Langholz, A. Kandel, J. Mott,

World Scientific, 1998

Page 5

Reference textbooks

Introduction to Logic Design, 2

nd

Ed,, Alan B, Marcovitz, Mc.

Graw Hill,2005

Foundation of Digital Logic Design, G.Langholz, A. Kandel, J.

Mott, World Scientific, 1998

Page 6

Grading policy

Homework: 20%

Lab work: 20%

Midterm: 30%

Final Exam (multichoice and writing): 30%

Page 7

1. Introduction

1.1. Review of Number Systems

1.2. Switching Algebra and Logic Circuits

Page 8

Chapter 1. Introduction

Page 9

1.1. Review of Number Systems

1.1.1 Number Representation

1.1.2 Binary Addition

1.1.3 Signed Numbers

1.1.4 Binary Subtraction

1.1.5 Binary Coded Decimal (BCD)

1.1.6 Other Codes

Page 10

1.1. Review of Number Systems

1.1.1 Number Representation

1.1.2 Binary Addition

1.1.3 Signed Numbers

1.1.4 Binary Subtraction

1.1.5 Binary Coded Decimal (BCD)

1.1.6 Other Codes

Page 11

1.1.1. Number Representation

Numbers are normally written using a positional number system:

Base/radix: b (the number of digits)

Digits: 0..(b-1)

0 a

i

(b-1)

Binary: b=2, digits:0,1

Decimal: b=10, digits: 0,1,2,3,4,5,6,7,8,9

Octal: b=8, digits: 0,1,2,3,4,5,6,7

Hexadecimal: b=16, digits: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

m n n n b

a a a a a a a a N

= ... . ...

2 1 0 1 2 1 ) (

Page 12

1.1.1. Number Representation

m n n n b

a a a a a a a a N

= ... . ...

2 1 0 1 2 1 ) (

m

m

n

n

n

n

b a b a b a b a b a b a N

+ + + + + + + = . ... . . . ... . .

1

1

0

0

1

1

1

1 ) 10 (

=

=

n

m i

i

i

b a N .

) 10 (

11101.11

(2)

= 1x2

4

+1x2

3

+1x2

2

+0x2

1

+1x2

0

+1x2

-1

+1x2

-2

= 29.75

(10)

Page 13

1.1.1. Number Representation

Decimal:

b=10

Digits: 0,1,2,3,4,5,6,7,8,9

Eg:

539.45

(10)

= 5x10

2

+3x10

1

+9x10

0

+4x10

-1

+5x10

-2

m n n n

a a a a a a a a N

= ... . ...

2 1 0 1 2 1 ) 10 (

ai = 0..9

Page 14

1.1.1. Number Representation

Binary:

b=2

Digits: 0,1

Eg:

1011.011(2) = 11 + 0*2

-1

+ 1*2

-2

+1*2

-3

=11 + 0 + 0.25 + 0.125

= 11.375

(10)

m n n n

a a a a a a a a N

= ... . ...

2 1 0 1 2 1 ) 2 (

ai = 0,1

bit binary digit

=

=

n

m i

i

i

a N 2 .

) 10 (

Page 15

1.1.1. Number Representation

Binary (cnt)

n-bit binary number can represent which range?

a

n-1

...a

1

a

0

from 0 to 2

n

-1

MSB Most Significant Bit

LSB Least Significant Bit

0001 = 1 1001 = 9

0010 = 2 1010 = 10

0011 = 3 1011 = 11

0100 = 4 1100 = 12

0101 = 5 1101 = 13

0110 = 6 1110 = 14

0111 = 7 1111 = 15

1000 = 8

Page 16

1.1.1. Number Representation

Octal:

b=8

Digits: 0,1,2,3,4,5,6,7

Eg:

503.071

(8)

= 5x8

2

+ 0x8

1

+ 3x8

0

+ 0x8

-1

+ 7x8

-2

+ 1x8

-3

m n n

a a a a a a a N

= ... . ...

2 1 0 1 1 ) 8 (

ai = 0..7

Hexadecimal:

b=16

Digits: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

Eg:

1010 0011(2)= A3(16)

503.071

(16)

= 5x16

2

+ 0x16

1

+ 3x16

0

+ 0x16

-1

+ 7x16

-2

+ 1x16

-3

ai = 0..F

m n n

a a a a a a a N

= ... . ...

2 1 0 1 1 ) 16 (

Page 17

Convert from base b to base 10

Base b to base 10 conversion

Eg:0

1010.11

(2)

= 10.75

1010.11

(8)

= 0*8

0

+1*8

1

+0*8

2

+1*8

3

+ 1*8

-

1

+1*8

-2

= 0+8+0+512+0.125+0.015625

A12

(16)

= 10572 = 2*16

0

+ 1*16

1

+ 10*16

2

= 2 + 16 + 2560= 2578

m n n n b

a a a a a a a a N

= ... . ...

2 1 0 1 2 1 ) (

m

m

n

n

n

n

b a b a b a b a b a b a N

+ + + + + + + = . ... . . . ... . .

1

1

0

0

1

1

1

1 ) 10 (

Page 18

110.011(2)=?(10) 6.375

110.011(8)=?(10) 72.0175

110.011(16)=?(10) 272.039...

Page 19

Convert from base 10 to base b

Base 10 to base b conversion

For integer part:

Divide integer part by b until the result is 0

Write remainders in reverse order to get the converted result.

For the odd part after .

Multiply by b until the result is 0

Page 20

Convert from base 10 to base 2

Eg1: 6.625

(10)

= ?

(2)

The integer part

Eg2: 20.75

(10)

= ?

(2)

6 2

0 3 2

1 1 2

1 0

The odd part after .

0.625 x 2 = 1.25

0.25 x 2 = 0.5

0.5 x 2 = 1.0

6.625

(10)

= 110.101

(2)

Page 21

20.75

(10)

= ?

(2)

10100.11(2)

20 2 0.75 * 2 = 1.5

0 10 2 0.5 * 2 = 1.0

0 5 2

1 2 2

0 1 2

1 0

Page 22

20.75

(10)

=?

(8)

=10100.11

(2)

= 24.6

(8)

20 8 0.75 * 8 = 6.0

4 2 8

2 0

Page 23

Convert from base 2 to base 2

n

Group from right to left n-bit groups and replace the

equivalent values in base 2

n

Eg:

101011(2) = ?(8) 1010.110

(2)

=12.6

(8)

101011(2) = ?(16) 1010.110

(2)

=A.C

(16)

Page 24

Convert from base 2

n

to base 2

Each digit in base 2

n

is replaced by n bit in base 2.

Eg:

37A.B(16)=?(2) = 0011 0111 1010 . 1011(2)

Page 25

Convert from base i to base j

If both i and j are powers of 2, use base 2 as an intermediate

base:

Eg: base 8 base 2 base 16

735.37

(8)

= 000111011101.01111100(2) = 1DD.7C ?

(16)

Else, use base 10 as an intermediate base:

Eg: base 5 base 10 base 2

Page 26

1.1. Review of Number Systems

1.1.1 Number Representation

1.1.2 Binary Addition

1.1.3 Signed Numbers

1.1.4 Binary Subtraction

1.1.5 Binary Coded Decimal (BCD)

1.1.6 Other Codes

Page 27

1.1.2 Binary Addition

Binary long addition similar to decimal long addition.

decimal binary

carry 110 11110

A 2565 10110

B 6754 11011

sum 9319 110001

Eg: 10101

(2)

+ 11011

(2)

= 110000 ?

(2)

Page 28

1.1.2 Binary Addition

Overflow:

Occur when the result of addition is out of range of representation

(the result can not be stored in the predefined number of bits)

In 8-bit computer, the result of addition of two binary numbers

10101010 and 11010011 is 9-bit binary number which can not be

stored in 8-bit => overflow

Page 29

1.1.2 Binary Addition

n-bit adder in computer:

A = a

n-1

a

n-2

...a

1

a

0

B = b

n-1

b

n-2

...b

1

b

0

Page 30

1.1. Review of Number Systems

1.1.1 Number Representation

1.1.2 Binary Addition

1.1.3 Signed Numbers

1.1.4 Binary Subtraction

1.1.5 Binary Coded Decimal (BCD)

1.1.6 Other Codes

Page 31

1.1.3 Signed Numbers

Represent sign and amplitude

Use the most-left-bit to represent sign:

0: positive, 1: negative

Eg: represent signed numbers using 4 bit:

+5 = 0101, -5 = 1101, -3 = 1011

Using 3 right bits to represent amplitude, we can represent from -7 to

+7.

Drawbacks:

+0 = 0000, -0 = 1000 => complex when calculating

=> need an other representation

Page 32

2s complement representation

Most left bit is still sign bit

Positive and 0 numbers are expressed in usual binary

format.

The largest number can be represented is 2

n-1

-1

n=8 => largest signed number: 2

8-1

-1 = 127

Negative number a is stored as the binary equivalent of 2

n

-

a in a n-bit system.

-3 is stored as 2

8

-3=11111101 in a 8-bit system

The most negative number can be stored is -2

n-1

Page 33

2s complement representation

+10 = 0000 1010

- 10 = 2

8

-10 = 1 0000 0000

0000 1010

1111 0110

- 10 = 1111 0110

+10 + (-10) = ? 0000 1010

1111 0110

1 0000 0000

Page 34

2s complement representation

Procedure to find binary representation of negative number

in 2s complement:

Find the binary equivalent of the magnitude

Complement each bit (0=>1, 1=>0)

Add 1

Eg: find representation of -13 in 8-bit signed number

system using 2s complement:

Magnitude: 13 = 0000 1101

Complement: 1111 0010

Add 1: 1

-13 = 1111 0011

+

Page 35

2s complement representation

Range of representation:

Use n bit to represent 2s complement numbers

Range: -2

n-1

=> 2

n-1

-1

Page 36

4 bit representation of unsigned and signed (2s complement)

Binary format Unsigned Signed

0000 0 0

0001 1 +1

0010 2 +2

0011 3 +3

0100 4 +4

0101 5 +5

0110 6 +6

0111 7 +7

1000 8 -8

1001 9 -7

1010 10 -6

1011 11 -5

1100 12 -4

1101 13 -3

1110 14 -2

1111 15 -1

Page 37

2s complement representation

To find the magnitude of a negative number:

Complement each bit

Add 1

Eg: 1001 0110(2) = -106?

0110 1001

+ 1

01101010 = 106

Page 38

Addition of signed numbers

The reason that 2s complement is so popular is the simplicity

of addition.

To add any two numbers, no matter what the sign of each is,

we just do binary addition on their representation.

-5 1011 -5 1011 -5 1011

+7 0111 +5 0101 +3 0011

+2 0010 0 0000 -2 1110

Page 39

Addition of signed numbers

Overflow

Occur when?

Add two numbers of the opposite sign?

Add two positive numbers?

Add two negative numbers?

maybe

Overflow occurs when adding two numbers with the

same sign and the result is in different sign

0110 0101 = 101

+ 0101 0010 = 82

1011 0111

Page 40

1.1. Review of Number Systems

1.1.1 Number Representation

1.1.2 Binary Addition

1.1.3 Signed Numbers

1.1.4 Binary Subtraction

1.1.5 Binary Coded Decimal (BCD)

1.1.6 Other Codes

Page 41

1.1.4 Binary Subtraction

Find the 2s complement of the second operand, then add.

a b = a + (-b)

Eg: 7 5 = ?

5 0101 7 0111

1010 -5 +1011

+ 1 2 0010

-5 1011

Page 42

1.1. Review of Number Systems

1.1.1 Number Representation

1.1.2 Binary Addition

1.1.3 Signed Numbers

1.1.4 Binary Subtraction

1.1.5 Binary Coded Decimal (BCD)

1.1.6 Other Codes

Page 43

Binary-Coded Decimal - BCD

BCD:

Use four bits (a nibble) to represent

each of the decimal digits 0 through

9.

Eg:

375 = 0011 0111 0101

(BCD)

Decimal Binary BCD

0 0000 0000

1 0001 0001

2 0010 0010

3 0011 0011

4 0100 0100

5 0101 0101

6 0110 0110

7 0111 0111

8 1000 1000

9 1001 1001

10 1010 0001 0000

11 1011 0001 0001

12 1100 0001 0010

13 1101 0001 0011

14 1110 0001 0100

15 1111 0001 0101

Page 44

1.1. Review of Number Systems

1.1.1 Number Representation

1.1.2 Binary Addition

1.1.3 Signed Numbers

1.1.4 Binary Subtraction

1.1.5 Binary Coded Decimal (BCD)

1.1.6 Other Codes

Page 45

ASCII

American Standard Code for Information Interchange - ASCII

Use seven bits to represent various characters on the

standard keyboard as well as a number of control signal

Page 46

Page 47

Problems

1. Convert the following unsigned numbers:

a. 98.625

(10)

=?

(2)

b. 11011.011

(2)

=?

(10)

c. 6A1.1E

(16)

=?

(8)

2. Represent the following signed numbers:

a. -74 in 8-bit signed 2s complement.

b. -74 in 16-bit signed 2s complement.

Page 48

1. Introduction

1.1. Review of Number Systems

1.2. Switching Algebra and Logic Circuits

Page 49

1.2. Switching Algebra and Logic Circuits

1.2.1 Definition of Switching Algebra

1.2.2 Basic Properties of Switching Algebra

1.2.3 Manipulation of Algebraic Functions

1.2.4 Representations of Algebraic Functions

1.2.5 Implementation of Functions with AND, OR, NOT, NAND,

NOR, XOR Gates

Page 50

1.2. Switching Algebra and Logic Circuits

1.2.1 Definition of Switching Algebra

1.2.2 Basic Properties of Switching Algebra

1.2.3 Manipulation of Algebraic Functions

1.2.3 Representations of Algebraic Functions

1.2.4 Implementation of Functions with AND, OR, NOT, NAND,

NOR, XOR Gates

Page 51

1.2.1 Definition of Switching Algebra

Switching algebra is binary:

All variables and constant take on 0 or 1.

Light on/off, switch: up/down, voltage: low/high...

Quantities which are not naturally binary must be coded into binary

format.

Three operators:

OR: a+b

AND: a.b

NOT: a

Page 52

1.2. Switching Algebra and Logic Circuits

1.2.1 Definition of Switching Algebra

1.2.2 Basic Properties of Switching Algebra

1.2.3 Manipulation of Algebraic Functions

1.2.3 Representations of Algebraic Functions

1.2.4 Implementation of Functions with AND, OR, NOT, NAND,

NOR, XOR Gates

Page 53

Basic Properties of Switching Algebra

P1: Commutative:

a + b = b + a a.b = b.a

P2: Associative:

a + (b + c) = (a + b) + c a.(b.c) = (a.b).c

P3:

a + 0 = a a . 1 = a

P4:

a + 1 = 1 a . 0 = 0

Page 54

Basic Properties of Switching Algebra

P5:

a + a = 1 a . a = 0

P6: no coefficient and no exponent

a + a = a a . a = a

n.a=a (a)

n

=a

P7: complement

(a) = a

P8: distributive:

a.(b+c) = a.b + a.c a + b.c = (a+b).(a+c)

Page 55

P9: adjacency

ab + ab = a (a+b)(a+b)=a

P10:

a + ab = a +b a(a+b) = ab

P11: De Morgan

(a + b) = ab (ab) = a + b

P12: absorption

a + ab = a a(a+b) = a

Basic Properties of Switching Algebra

Basic Properties of Switching Algebra

Page 56

P13: redundant

ab+bc+ac = ab+bc

A B

C

Basic Properties of Switching Algebra

Page 57

Problems

1. Prove the following equalities:

a. xy+y=x+y

b. xy+xz+yz=xy+xz => prove it incorrect

c. xyz+yz+xz=z

d. (x+y)[x(y+z)]+xy+xz = 1

Page 58

1.2. Switching Algebra and Logic Circuits

1.2.1 Definition of Switching Algebra

1.2.2 Basic Properties of Switching Algebra

1.2.3 Manipulation of Algebraic Functions

1.2.4 Representations of Algebraic Functions

1.2.5 Implementation of Functions with AND, OR, NOT, NAND,

NOR, XOR Gates

Page 59

Manipulation of Algebraic Functions

A literal:

Is the appearance of a variable or its complement

Eg: x and x are two different literals

Expression ab+bcd+ad+e has 8 literals

A product term:

Is one or more literal connected by AND operators

Expression ab+bcd+ad+ehas 4 product terms

Note: A single literal is also a product term

Page 60

A standard product term - minterm:

Is a product term which includes every variable of the

function, either uncomplemented or complemented.

Eg: for a function of four variables a,b,c,d:

the product term abcd is a standard product term

the product term abd is not

Manipulation of Algebraic Functions

Manipulation of Algebraic Functions

Page 61

A sum of product - SOP:

Is one or more product terms connected by OR operators

Eg: abc+abc+ac+a

d

A canonical sum sum of standard product term

Is a sum of products expression where all terms are

standard product terms.

Eg: A function of three variables a,b,c:

abc + abc + abc is a canonical sum

abc + abc + a is not

Manipulation of Algebraic Functions

Manipulation of Algebraic Functions

Page 62

A minimum sum of products:

Is one of those SOP expression for a function that has

the fewest number of product terms.

If there is more than one expression with fewest number

of terms, then minimum is defined as one or more of

those expressions with the fewest number of literals.

Eg:

F1(x,y,z) = xyz+xyz+ xyz+xyz+xyz

F2(x,y,z) = xy+xy+xyz

F3(x,y,z) = xy+xy+xz

F4(x,y,z) = xy+xy+yz

Manipulation of Algebraic Functions

F3,F4 are minimum SOP of F1

Manipulation of Algebraic Functions

Page 63

A sum term:

Is one or more literals connected by OR operators

Eg:

a + b + c

b

A standard sum term - maxterm:

Is a sum term that includes each variable of the problem,

either uncomplemented or complemented

Eg: For a function of four variables x,y,z,t

x+y+z+t is a maxterm

x+y+t is not

Manipulation of Algebraic Functions

Manipulation of Algebraic Functions

Page 64

A product of sum POS:

Is one or more sum terms connected by AND

Eg:

(w+x+y)(w+y+z)(w+x+z)

w

A canonical product product of standard sum

terms:

Is a product of sum term where all sum terms are standard

Manipulation of Algebraic Functions

Manipulation of Algebraic Functions

Page 65

A minimum POS is defined the same way as SOP:

fewest number of terms

the same number of terms => fewest number of literals

Manipulation of Algebraic Functions

Manipulation of Algebraic Functions

Page 66

Canonical forms

Three-variable minterm and Maxterm

Decimal x y z minterm Maxterm

0 0 0 0 xyz (m

0

) x+y+z (M0)

1 0 0 1 xyz (m

1

) x+y+z (M1)

2 0 1 0 x'yz (m2) x+y+z (M2)

3 0 1 1 x'yz (m3) x+y+z (M3)

4 1 0 0 xyz (m4) x+y+z (M4)

5 1 0 1 xy'z (m5) x'+y+z (M5)

6 1 1 0 xyz' (m6) x'+y+z (M6)

7 1 1 1 xyz (m7) x'+y+z (M7)

Page 67

Canonical forms

Properties of minterm/Maxterm:

m

i

m

j

=0 if ij

=m

i

if i=j

M

i

+M

j

=1 if ij

= M

i

if i=j

m

i

=M

i

and M

i

=m

i

for every i

Page 68

Canonical forms

An algebraic expression of a Boolean function can

be derived from a given truth table in two ways:

By summing (ORing) those minterm for which the function

takes a value 1.

By multiplying (ANDing) those maxterm for which the

function takes a value 0.

Page 69

Canonical forms

Decimal x2 x1 x0 f

0 0 0 0 0

1 0 0 1 1

2 0 1 0 0

3 0 1 1 0

4 1 0 0 1

5 1 0 1 1

6 1 1 0 1

7 1 1 1 1

f(x2,x1,x0)=m

1

+m

4

+m

5

+m

6

+m

7

=(1,4,5,6,7)

f(x2,x1,x0)=M

0

M

2

M

3

= (0,2,3)

Canonical sum-of-products (SOP)

Canonical product-of-sums (POS)

Page 70

F(a,b,c)= abc+ab

F(a,b,c)=m0+m1+m6

(0,1,6)

Decimal a b c f

0 0 0 0 1

1 0 0 1 1

2 0 1 0 0

3 0 1 1 0

4 1 0 0 0

5 1 0 1 0

6 1 1 0 1

7 1 1 1 0

Page 71

1.2. Switching Algebra and Logic Circuits

1.2.1 Definition of Switching Algebra

1.2.2 Basic Properties of Switching Algebra

1.2.3 Manipulation of Algebraic Functions

1.2.4 Representations of Algebraic Functions

1.2.5 Implementation of Functions with AND, OR, NOT, NAND,

NOR, XOR Gates

Page 72

1.2.4 Representations of Algebraic Functions

Truth table

Venn diagram

Karnaugh map

Page 73

Truth table

List all the possible binary combinations of the independent

variables and display the corresponding binary values of

dependant variables.

Page 74

Truth table

n independent variables and m dependant functions:

2

n

rows

n+m columns

3 independent

variables

2 dependent

functions

2

3

rows

Page 75

Venn diagram

Venn diagram using space to present logic

F(A,B)=A.B

A B

C

F(A,B,C)=C.not(B)

Page 76

Venn diagram

A A

A+B

A.B

A.B

A+B

Page 77

Karnaugh map

BC

A

00 01 11 10

0

0

1

3

2

1

4

5

7

6

C

AB

0 1

00

0

1

01

2

3

11

6

7

10

4

5

A Karnaugh map is a graphical method for

representing the true table of a Boolean function.

K-map may be used for any variables number, but

often at most six.

Page 78

Karnaugh map (K-map)

If variables number is n => 2

n

cells in K-map.

2

n

cells are arranged in logical pattern for minimization

purpose.

BC

A

00 01 11 10

0

0

1

3

2

1

4

5

7

6

Page 79

Two-variable K-map

F(A,B)

0

1

2

3

A

B

0 1

0

1

0

2

1

3

B

A

0 1

0

1

Page 80

Two-variable K-map

F(A,B) = AB

0 0

0 1

A

B

0 1

0

1

Page 81

Three-variable K-map

F(A,B,C)

BC

A

00 01 11 10

0

0

1

3

2

1

4

5

7

6

C

AB

0 1

00

0

1

01

2

3

11

6

7

10

4

5

Page 82

Three-variable K-map

F(x,y,z) = xyz + yz + x

x y z F

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 1

yz

x

00 01 11 10

0

0 0 0 1

1

1 1 1 1

z

xy 0 1

00

0 0

01

1 0

11

1 1

10

1 1

Page 83

Four-variable K-map

CD

AB

00 01 11 10

00

01

11

10

F(A,B,C,D)

Page 84

Four-variable K-map

F(A,B,C,D) = AB + CD + BCD

CD

AB

00 01 11 10

00

0 0 0 1

01

0 0 1 1

11

1 1 1 1

10

0 0 0 1

Page 85

Five-variable K-map

00 01 11 10

AB

CD

00

01

11

10

00 01 11 10

AB

CD

00

01

11

10

E 0 1

5 variables Karnaugh Map consists of two

4 variables Karnaugh Map connected up/down.

Page 86

Six-variable K-map

1 1

1 1

1 1

00 01 11 10

AB

CD

00

01

11

10

1 1

1 1

1 1

00 01 11 10

AB

CD

00

01

11

10

E

0 1

1 1

1 1

1 1

00 01 11 10

AB

CD

00

01

11

10

1 1

1 1

1 1

00 01 11 10

AB

CD

00

01

11

10

F

0

1

Page 87

Karnaugh map with dont care

CD

00 01 11 10

00

01

11

10

AB

1 1

1 1

dont care ~ input conditions that not occur

Page 88

1.2. Switching Algebra and Logic Circuits

1.2.1 Definition of Switching Algebra

1.2.2 Basic Properties of Switching Algebra

1.2.3 Manipulation of Algebraic Functions

1.2.4 Representations of Algebraic Functions

1.2.5 Implementation of Functions with AND, OR, NOT, NAND,

NOR, XOR Gates

Page 89

Basic logic gates

AND OR NOT

A B out

0 0 0

0 1 0

1 0 0

1 1 1

A B out

0 0 0

0 1 1

1 0 1

1 1 1

A out

0 1

1 0

Page 90

Basic logic gates

NAND NOR XOR

A B out

0 0 1

0 1 1

1 0 1

1 1 0

A B out

0 0 1

0 1 0

1 0 0

1 1 0

A B out

0 0 0

0 1 1

1 0 1

1 1 0

Page 91

Implementation of Functions with AND, OR

Assume all inputs are available in uncomplemented and

complemented

F1 = xyz+xyz+xyz+xyz+xyz

F2 = xy+xy+xz

Page 92

Implementation of Functions with AND, OR, NOT

Complemented inputs can be produced using inverters NOT:

X

Y

Z

F

Page 93

Multilevel circuits

A circuit is called n-level circuit if the maximum number of

gates through which one signal must pass from input to

output

two-level circuit

three-level circuit

Page 94

Implementation of Functions with NAND

Using equivalent change steps, every expression can be

represented using only NAND gates.

NOT

AND

OR

A

B

A.B (A.B)

=A+B

A

B

Page 95

Implementation of Functions with NAND

Represent the following expression using only NAND:

F(a,b,c) = ab + bc + b

=

b c b ab b c b ab b c b ab . . = + + = + +

Page 96

Implementation of Functions with NOR

Using equivalent change steps, every expression can be

represented using only NOR gates.

U10A

7402N

U11A

7402N

U7A

7402N

U8A

7402N

U9A

7402N

A

B

(A'+B')'=A.B

A'

B'

U3A

7402N

A

(A+A)'=A'

Page 97

Implementation of Functions with NOR

Represent the following expression using only NOR:

F(a,b,c) = ab + bc + b

Page 98

Chapter 2.

Logic Function Minimization Methods

Page 99

2. Function Minimization Methods

2.1 Algebraic Method

2.2 The Karnaugh Map Method

2.3 Quine-McCluskey Method

Page 100

What is minimization?

Number of operands is minimal and number of literal in each operand is

minimal

Why minimization needed?

Minimize electronic components used to construct the circuit to

implement that expression

2. Function Minimization Methods

Page 101

2. Function Minimization Methods

2.1 Algebraic Method

2.2 The Karnaugh Map Method

2.3 Quine-McCluskey Method

Page 102

2.1. Algebraic Method

Use algebraic properties to minimize expressions

Drawback:

Heuristic, depending on experience no formal method/procedure

Manually

Not sure whether the last expression is minimal or not

Page 103

2.1. Algebraic Method

Eg: Minimize these expressions using algebraic method:

F0(x,y,z)=xyz+xyz+xyz+xyz

F1(a,b,c,d)=ab+abc+acd+acd+abcd

F2(A,B,C,D)=

F3(x,y,z)=(x+y)(x+y+z)+y

F4(a,b,c,d)=(a+b+c)(a+c)(a+b+c)(a+c+d)

) )( .( ) ( C AD C B A BC A + + + +

Page 104

2. Function Minimization Methods

2.1 Algebraic Method

2.2 The Karnaugh Map Method

2.3 Quine-McCluskey Method

Page 105

2.2 The Karnaugh Map Method

1. Minimum Sum of Product Expressions Using the Karnaugh

Map

2. Dont Cares

3. Product of Sums

4. Minimum Cost Gate Implementation

5. Five- and Six-Variable Maps

6. Multiple Output Problems

Page 106

Implicant, Prime Implicant

An implicant of a function is a product term that can be used in a SOP

CD

AB

00 01 11 10

00 1 1

01 1

11 1 1 1 1

10

Implicants of F

Minterm Groups of 2 Groups of 4

ABCD ACD AB

ABCD BCD

ABCD ABC

ABCD ABD

ABCD ABC

ABCD ABD

ABCD

Page 107

Implicant, Prime Implicant

A prime Implicant is an implicant which can not be contained

in any other implicants.

CD

AB

00 01 11 10

00 1 1 1

01 1 1

11 1 1

10 1 1 1 1

B C

*

B D

*

B D

A D

A B

C D

Page 108

Essential Prime Implicant

Essential PI is a PI which contains at least one minterm which

is not contained in other PI.

CD

AB

00 01 11 10

00 1 1 1

01 1 1

11 1 1

10 1 1 1 1

B C

*

B D

*

B D

A D

A B

C D

minterm 0 is only contained in PI BD

minterm 5 is only contained in PI BD

=> BD & BD are two Essential PI

Page 109

2.2.1 Minimum Sum of Product Expressions

Rules to minimize using K-map:

Rule 1: Fill K-map cells with corresponding values

Rule 2: Group adjacent cells whose values are 1. Number of cells is 2

n

.

Rule 3: Each group will be a part of result. Variables in each group will

be excluded: 2

n

cells => exclude n variables.

Page 110

2.2.1 Minimum Sum of Product Expressions

Step 2: Group adjacent cells whose values are 1. Number

of cells is 2

n

.

CD

AB

00 01 11 10

00

01

1

1

11

1 1

10

1 1

CD

AB

00 01 11 10

00

1

1

01

1 1

11

1 1

10

1 1

Page 111

Step 3: Each group will be a part of result. Variables in each

group will be excluded: 2

n

cells => exclude n variables.

CD

AB

00 01 11 10

00

01

1 1

11

1 1

10

1 1

2

1

cells => eliminate 1 variable

2

2

cells => eliminate 2 variables

F(A,B,C,D) = ABC + AC

2.2.1 Minimum Sum of Product Expressions

Page 112

Example 1: Minimize these functions using K-map:

a. F(A,B,C,D) = R(0,2,5,6,9,11,13,14)

b. F(A,B,C,D) = R(1,3,5,8,9,13,14,15)

c. F(A,B,C,D) = R(2,4,5,6,7,9,12,13)

d. F(A,B,C,D)= R(1,3,4,5,7,9,13,14,15)

e. F(A,B,C,D)=R(1,3,4,6,9,11,12,14)

2.2.1 Minimum Sum of Product Expressions

Page 113

a. F(A,B,C,D) = R(0,2,5,6,9,11,13,14)

= BCD + ABD + BCD + ABD

CD

AB

00 01 11 10

00

1

1

01

1

1

11

1

1

10

1

1

Page 114

b. F(A,B,C,D) = R(1,3,4,6,9,11,12,14)

= BD + BD

CD

AB

00 01 11 10

00

1 1

01

1

1

11

1

1

10

1

1

Page 115

2.2 The Karnaugh Map

1. Minimum Sum of Product Expressions Using the Karnaugh

Map

2. Dont Cares

3. Product of Sums

4. Minimum Cost Gate Implementation

5. Five- and Six-Variable Maps

6. Multiple Output Problems

Page 116

2.2.2 Dont care

If the function has dont care values in cells:

Cells with dont care values

can be grouped with 1 cells

Do not group only dont

care cells in one group.

CD

00 01 11 10

00

01

11

10

AB

1 1

1 1

C B C B D C B A F + = ) , , , (

Page 117

Examples:

F(a,b,c,d)=R(1,3,5,7,12,13)

dont care (0,4,10,15)

CD

AB

00 01 11 10

00

-

1

1

01

- 1

1

11

1

1

-

10

-

Page 118

2. Function Minimization Methods

2.1 Algebraic Method

2.2 The Karnaugh Map Method

2.3 Quine-McCluskey Method

Page 119

2.3 Quine-McCluskey Method

1. Quine-McCluskey Method for One Output

2. Iterated Consensus for One Output

3. Prime Implicant Tables for One Output

4. Quine-McCluskey for Multiple Output Problems

5. Iterated Consensus for Multiple Output Problems

6. Prime Implicant Tables for Multiple Output Problems

Page 120

2.3. Quine-Mcluskey method

Karnaugh map cannot handle more than 6 variables.

Quine-McCluskey method has no limitation with number of

variables, and is suitable for computer algorithm.

0 1

00

01 1

11 1 1

10 1 1

AB

C

ABC+ABC+ABC+ABC+ABC

010

*10 11* 1*0 1*1 10*

110 111 100 101

1**

find a pair of numbers of 1 bit difference

Page 121

Quine-Mcluskey Procedure

1: Represent minterms in binary numbers

2: Group each minterm by the number of 1 appearance

3: Make set of 1 bit different numbers between neighboring

group

write the difference within parenthesis

mark * to the number which is not included in a set

4: Make set of 1 bit different sets with the same number in a

parenthesis

append the difference to parenthesis

mark + to the set which is not included in a set

5: Iterate these step until all the generated set is marked *

6: Select prime implicants

7: Convert to logic variable

Page 122

S1. Represent minterms in binary numbers

f = ABCDEF+ABCDEF+ABCDEF+ABCDEF+ABCDEF

+ABCDEF+ABCDEF +ABCDEF+ABCDEF+ABCDEF

f = 000000+000010+000110+000111+001110

+001000+101001+001100+001111+001010

f(A,B,C,D,E,F)=(0,2,6,7,14,8,41,12,15,10)

Page 123

S2. Grouping

f = 000000+000010+000110+000111+001110

+001000+101001+001100+001111+001010

000000

once twice three times

000010

001000

000110

001100

001010

000111

001110

101001

four times

001111

group 0 group 1 group 2

group 3 group 4

group each term by the appearance of 1

no times

Page 124

S3 & S4. Making set (1)

000000 0

000010 2

001000 8

000110 6

001010 10

001100 12

000111 7

001110 14

101001 41

001111 15

0,2 (2)

0,8 (8)

2,6(4)

2,10(8)

8,10(2)

8,12(4)

6,7(1)

6,14(8)

10,14(4)

12,14(2)

7,15(8)

14,15(1)

find a pair of 1 bit difference

between neighboring group

write difference within ( )

mark

to the number

not included in any set

group 0

group 1

group 2

group 3

group 4

Page 125

S3 & S4. Making set (2)

0,2 (2)

0,8 (8)

2,6(4)

2,10(8)

8,10(2)

8,12(4)

6,7(1)

6,14(8)

10,14(4)

12,14(2)

7,15(8)

14,15(1)

0,2,8,10(2,8)

2,6,10,14(4,8)

8,10,12,14(2,4)

6,7,14,15(1,8)

mark to the set

not involved

in the next level set

when all the set is marked

finish

Each pair appears in duplicate

find a pair of 1 bit different sets

with the same value in ( )

between neighboring group

append difference within ( )

Page 126

S6. Selecting Prime Implicants (1)

41

0,2,8,10(2,8)

2,6,10,14(4,8)

8,10,12,14(2,4)

6,7,14,15(1,8)

0 2 6 7 8 10 12 14 15 41

x x x x

x

x x x x

x x x x

x x x x

If only one x in a column, then the row is inevitable implicant

minterms (given at first)

P

r

i

m

e

i

m

p

l

i

c

a

n

t

m

a

r

k

e

d

write x into the position where minterm is included

in the prime implicant

inevitable

implicant

Page 127

S6. Selecting Prime Implicants (2)

41

0,2,8,10(2,8)

2,6,10,14(4,8)

8,10,12,14(2,4)

6,7,14,15(1,8)

0 2 6 7 8 10 12 14 15 41

x x x x

x

x x x x

x x x x

x x x x

mini term

p

r

i

m

e

i

m

p

l

i

c

a

n

t

s

mark minterms involved in the

inevitable implicants

inevitable

implicants

Page 128

S7. Conversion to logic variables

41 101001

0,2,8,10(2,8)

000000

000010

001000

001010

8,10,12,14(2,4)

001000

001010

001100

001110

6,7,14,15(1,8)

000110

000111

001110

001111

ABCDEF

ABDF

ABCF

ABDE

F=ABCDEF

+ABDF

+ABCF

+ABDE

Page 129

Examples:

Minimize the following functions using Quine-

Mcluskey method:

a.

b. F(a,b,c,d,e,f) =

(17,21,25,29, 44,45,46,47,49,52,53,54,55,47,61)

f e d b a f d c b f e bc a ef d b a + + + = f) e, d, c, b, F(a,

Page 130

Quine-Mcluskey method with dont care

1: Represent logic function in sum of mini terms ==>A

2: Represent dont care in sum of mini terms ==>B

3: If there exist duplication in A and B, remove from A

4: Apply Quine-McCluskey method for A and B

5: Be careful not to include B in selecting prime implicants

Page 131

Quine-Mcluskey method with dont care

f=ABCD+BCD+ACD+ABCD+ABCD

dont care AD

mini term

ABCD

0000

0001

0010

0011

0101

0111

1011

1101

1111

decimal

0

1

2

3

5

7

11

13

15

first comparison second comparison

0,1(1)

0,2(2)

1,3(2)

1,5(4)

2,3(1)

3,7(4)

3,11(8)

5,7(2)

5,13(8)

7,15(8)

11,15(4)

13,15(2)

0,1,2,3(1,2)

1,3,5,7(2,4)

3,7,11,15(4,8)

5,7,13,15(2,8)

Page 132

Quine-Mcluskey method with dont care

0 2 11 13 15

0,1,2,3(1,2)

1,3,5,7(2,4)

3,7,11,15(4,8)

5,7,13,15(2,8)

x x

x

x

x

x

00**

0**1

**11

*1*1

ABCD

f=AB+CD+BD

Page 133

Chapter 3.

Larger Combinational Systems

Page 134

Introduction

Logic circuits are divided into two classes:

Combinational logic circuits

Output signals only depend on current input signals

Memoryless circuits

Sequential logic circuits

Output signals not only depend on current input signals, but also

depend on those input signals in the past

Memory circuits

Page 135

3. Larger Combinational Systems

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

Page 136

3.1 Delay in Combinational Logic Circuits

Delay through logic gates

When the input to a gate changes, the output of that gate doesnt

change immediately; but there is a small delay .

The output is stable after the longest delay path

A

B

C

F

X

Page 137

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

3. Larger Combinational Systems

Page 138

Half Adder

a

b

E

r

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

E=a b

r = ab

=1

&

a

b

E

r

Half Adder

HA

a

b

E

r

(Result)

(Carry-out)

Page 139

Addition of two n-bit numbers

E

4

E

3

E

2

E

1

E

0

r

3

r

2

r

1

r

0

A =

a

3

a

2

a

1

a

0

+B =

b

3

b

2

b

1

b

0

r

4

E

3

r

3

E

2

r

2

E

1

r

1

E

0

Summation

Page 140

Full Adder

FA

a

i

r

i

b

i

E

i

r

i+1

a

i

b

i

r

i

E

i

r

i+1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

a

i

b

i

r

i

00 01 11 10

0

1 1

1

1 1

E

i

a

i

b

i

r

i

00 01 11 10

0

1

1

1 1 1

r

i+1

E

i

= a

i

b

i

r

i

r

i+1

= a

i

b

i

+ r

i

(a

i

b

i

)

Page 141

Combinational logic circuit design procedure

Problems: design a combinational logic circuit to do smth.

Design procedure:

S1: Find inputs, outputs and relations.

S2: Construct truth table

S3: For each output, using K-map to minimize from truth table.

S4: Draw the circuit.

Page 142

Example 1

Problem: Design a combinational logic circuit to implement

this operation: M=N+3, N is 3-bit binary number, the number

of bit of M is selected properly.

Solution:

S1: three inputs: n

2

n

1

n

0

four outputs: m

3

m

2

m

1

m

0

Page 143

Example 1

S1: three inputs: n

2

n

1

n

0

four outputs: m

3

m

2

m

1

m

0

S2: truth table

n2 n1 n0 m3 m2 m1 m0

0 0 0 0 0 1 1

0 0 1 0 1 0 0

0 1 0 0 1 0 1

0 1 1 0 1 1 0

1 0 0 0 1 1 1

1 0 1 1 0 0 0

1 1 0 1 0 0 1

1 1 1 1 0 1 0

S3:

n1n0

n2

00 01 11 10

0 0 0 0 0

1 0 1 1 1

m

3

= n

2

n

0

+ n

2

n

1

n2

n1

n0

m3

m2

m1

m0

Page 144

Example 2

Problem: design a combinational logic circuit to calculate

square of a 2-bit binary number.

Solution:

Step1: find inputs, outputs

Inputs: a1,a0

Outputs: b3,b2,b1,b0

Ex2

Page 145

Step 2: truth table

Step3: using K-map to minimize outputs

b3 = a1.a0 b1 = 0

b2 = a1.a0 b0 = a0

Example 2

a1 a0 b3 b2 b1 b0

0 0 0 0 0 0

0 1 0 0 0 1

1 0 0 1 0 0

1 1 1 0 0 1

Page 146

Example 2

Step 4: Draw circuit

b3 = a1.a0 b1 = 0

b2 = a1.a0 b0 = a0

a1

a0

b3

b2

b1

b0

U1A

7408N

U1B

7408N

U2A

7404N

X1

2.5 V

X2

2.5 V

X3

2.5 V

X4

2.5 V

R1

100

V1

5 V

J1

Key = A

R2

100

V2

12 V

J2

Key = B

Page 147

Full Adder

=1

&

r

i

a

i

b

i

=1

&

E

i

r

i+1

>1

Page 148

Full Adder

=1

&

r

i

a

i

b

i

=1

&

E

i

r

i+1

>1

HA HA

Page 149

n-bit Adder

Serial n-bit adder

A = a

n-1

a

n-2

...a

1

a

0

, B = b

n-1

b

n-2

...b

1

b

0

FA

a

n-1

b

n-1

r

n-1

r

n

E

n-1

FA

a

n-2

b

n-2

r

n-2

E

n-2

FA

a

1

b

1

r

1

r

2

E

1

FA

a

0

b

0

r

0

= 0

E

0

E

n

Delay = n x ?

Page 150

n-bit Adder

Parallel n-bit adder:

r

i+1

= a

i

b

i

+ r

i

(a

i

b

i

)

P

i

= a

i

b

i

and G

i

= a

i

b

i

r

i+1

= G

i

+ r

i

P

i

r

1

= G

0

+ r

0

P

0

&

> 1 G

0

P

0

r

0

r

1

t

1

t

2

r

2

= G

1

+ G

0

P

1

+ r

0

P

0

P

1

&

> 1 G

1

G

0

P

1

r

2

t

1

t

2

&

P

0

r

0

Page 151

Parallel 4-bit addition

r

4

= E

4

E

3

E

2

E

1

E

0

r

2

r

1

a

2

b

2

a

1

b

1

a

0

b

0

P

3

G

3

P

2

G

2

P

1

G

1

P

0

G

0

Calculate P

i

and G

i

a

3

b

3

a

2

b

2

a

1

b

1

a

0

b

0

Carry calculation

Sum calculation

r

0

a

3

b

3

r

3

r

4

r

0

Page 152

Subtractor

To subtract a-b, simply add a to 2s complement of b.

Second choice:

Half Subtractor => Full Subtractor => n-bit Subtractor

Page 153

Subtractor

Subtractor by using 2s complement

A3

A2 A1 A0

B3 B2

B1 B0

S3 S2

S1 S0

1

C1 C2 C3

C4

A

B

C

S

C+ FA

A

B

C

S

C+ FA

A

B

C

S

C+ FA

A

B

C

S

C+ FA

Page 154

Adder and Subtractor

C1 C2 C3

C4

A

B

C

S

C+ FA

A

B

C

S

C+ FA

A

B

C

S

C+ FA

A

B

C

S

C+ FA

MPX MPX MPX MPX

A3

A2

A1 A0 B3 B2

B1 B0

S3 S2 S1 S0

sel

Page 155

3. Larger Combinational Systems

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

Page 156

Decoder

An nxm decoder is a combinational circuit that converts

binary information from n input lines to m output lines, where

m2

n

.

m = 2

n

=> complete decoder

Fundamental property: only one output is 1 for any given

input combination.

Page 157

Decoder

Complete decoders: m=2

n

Eg:

+ 3 bit inputs x1,x2,x3.

+ 8 bit outputs Y

0

,Y

1

Y

7

nxm

decoder

.

.

.

.

.

.

x

1

x

2

x

n

D

0

D

1

D

m-1

E

3x8

decoder .

.

.

x

1

x

2

x

3

D

0

D

1

D

7

Page 158

Design 3x8 decoder

3x8

decoder .

.

.

x

1

x

2

x

3

D

0

D

1

D

7

En

if (En=0)

Disable or D0...D7=0

else if (En=1)

Function as a 3x8 decoder

Page 159

BCD-to-decimal decoder

BCD

to

decimal

Decoder

A

B

C

D

Y

0

Y

1

Y

i

Y

9

:

:

N

A

B

C

D

Y

0

Y

1

.

.

Y

9

0

0

0

0

0

1

0

.

.

0

1

0

0

0

1

0

1

.

.

0

2

0

0

1

0

0

0

.

.

0

3

0

0

1

1

0

0

.

.

0

4

0

1

0

0

0

0

.

.

0

5

0

1

0

1

0

0

.

.

0

6

0

1

1

0

0

0

.

.

0

7

0

1

1

1

0

0

.

.

0

8

1

0

0

0

0

0

.

.

0

9

1

0

0

1

0

0

.

1

Page 160

BCD-to-decimal decoder

= =

0 1

Y A B C D Y A B C D

=

2

Y BCD

=

=

=

=

=

=

=

3

4

5

6

7

8

9

Y BCD

Y BC D

Y BC D

Y BC D

Y BCD

Y AD

Y AD

CD

AB

00 01 11 10

00 1

01

11

10

Page 161

Decoder

4x16 decoder using two 3x8 decoders

3x8

decoder .

.

.

x

2

x

3

x

4

D

0

D

1

D

7

3x8

decoder .

.

.

x

1

D

8

D

9

D

15

Page 162

Decoder implementation of arbitrary functions

4x16

decoder

x

2

x

3

x

4

D

0

D

1

D

2

x

1

D

3

D

4

D

5

D

6

D

7

D

8

D

9

D

10

D

11

D

12

D

13

D

14

D

15

F1

F1(x1,x2,x3,x4)=(0,1,3,8,12)

Page 163

BCD-to-7segment decoder

a

b

c

d

e

f g

Each segment is a Light

Emitting Diode (LED)

K A

N A B C D a b c d e f g

0 0 0 0 0 1 1 1 1 1 1 0

1 0 0 0 1 0 1 1 0 0 0 0

2 0 0 1 0 1 1 0 1 1 0 1

3 0 0 1 1 1 1 1 1 0 0 1

4 0 1 0 0 0 1 1 0 0 1 1

5 0 1 0 1 1 0 1 1 0 1 1

6 0 1 1 0 1 0 1 1 1 1 1

7 0 1 1 1 1 1 1 0 0 0 0

8 1 0 0 0 1 1 1 1 1 1 1

9 1 0 0 1 1 1 1 1 0 1 1

Page 164

BCD-to-7segment decoder

CD

AB

00 01 11 10

00

1 0 1 1

01

0 1 1 1

11

10

1 1

= + + + a A C BD B D

&

&

B

D

> 1

A

C

Page 165

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

3. Larger Combinational Systems

Page 166

Encoder

An encoder is a circuit that performs the function of a decoder in reverse.

An mxn encoder has m inputs, n outputs where m2

n

. The outputs

generate the binary codes corresponding to m inputs.

For example: encoder for PCs keyboard

Key <=> Character <=> Key code

102 keys, 8 bit ASCII

Page 167

Keyboard encoder

9 keys

4-bit key code.

1

2

i Encoder

9

P

2

P

1

P

i

A

B

C

D

N=i

1

P

9

Page 168

Keyboard encoder

A = 1 if (N=8) or (N=9)

B = 1 if (N=4) or (N=5) or (N=6)

or (N=7)

C = 1 if (N=2) or (N=3) or (N=6)

or (N=7)

D = 1 if (N=1) or (N=3) or (N=5)

or (N=7) or (N=9)

N ABCD

1 0001

2 0010

3 0011

4 0100

5 0101

6 0110

7 0111

8 1000

9 1001

Page 169

Keyboard encoder

> 1

> 1

> 1

> 1

N=9

N=8

N=7

N=6

N=5

N=4

N=3

N=2

N=1

A

B

C

D

Page 170

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders

3.5 Multiplexors

3.6 Demultiplexors

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

3. Larger Combinational Systems

Page 171

Multiplexor

Multiplexor has one output and more than one input.

Function: select one of input for output

X

0

X

1

C

0

Y

MUX 2-1

C

0

Y

0

X

0

1

X

1

C

1

C

0

Y

0

0

X

0

0

1

X

1

1

0

X

2

1

1

X

3

control inputs

X

0

X

1

X

2

X

3

C

0

C

1

Y

MUX 4-1

Page 172

2-to-1 Multiplexor

X

0

X

1

C

0

Y

MUX 2-1

C

0

Y

0

X

0

1

X

1

= +

0 0 1 0

Y X C X C

X

1

X

0

C

0

00 01 11 10

0 1 1

1 1 1

C

0

X

1

X

0

Y

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

0

1

1

0

1

1

1

1

1

Page 173

2-to-1 Multiplexor

Page 174

4-to-1 Multiplexor

Y = s

1

s

0

I

0

+ s

1

s

0

I

1

+s

1

s

0

I

2

+ s

1

s

0

I

3

Page 175

Application of multiplexor

Select source

Source 1 Source 2

Receiver

Y

3

Y

2

Y

1

Y

0

A = a

3

a

2

a

1

a

0

B = b

3

b

2

b

1

b

0

C

0

Page 176

Application of multiplexor

Convert parallel-serial

a

0

a

1

a

2

a

3

C

0

C

1

Y

a

0

a

1

a

2

a

3

Y

C

1

C

0

0

1

0

1

t

t

t

A

Page 177

Application of multiplexor

Implementation of arbitrary functions:

= + + + f(A,B) A Bf(0,0) A Bf(0,1) A Bf(1,0) A Bf(1,1)

= + + +

1 0 0 1 0 1 1 0 2 1 0 3

Y C C X C C X C C X C C X

x

0

x

1

x

2

x

3

C

1

C

0

f(0,0)

f(0,1)

f(1,0)

f(1,1)

A

B

Y = f(A,B)

Inputs to

select

function

Variables

Page 178

Example

F(A,B) = AB + AB

x

0

x

1

x

2

x

3

C

1

C

0

0

1

1

0

A

B

Y = f(A,B)

Inputs to

select

function

Variables

Page 179

3. Larger Combinational Systems

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders and Priority Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

Page 180

Demultiplexor

Demultiplexor has one input and more than one output

Function: select one of outputs for input

E

C

0

S

0

S

1

E C S

E C S

0 1

0 0

=

=

DeMUX 1-2

Page 181

Demultiplexor 1-4

E

C

1

C

0

S

0

S

1

S

2

S

3

Page 182

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders and Priority Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

3. Larger Combinational Systems

Page 183

3.7 Three-State Gates (Tristate)

Three state gates exhibit three states instead of two states.

The three states are:

High : 1

Low : 0

High impedance : z

In this state the output is disconnected which is equal to open circuit.

In the other words in that state circuit has no logic significant. We can

have AND or NAND three-state gates but the most common is three-

state buffer gate

Page 184

3.7 Three-State Gates (Tristate)

We may use conventional gates such as AND or NAND as

three-state gates but the most common is three-state buffer

gate.

Note that buffer produces transfer function and can be used

for power amplification. Three state buffer has extra input

control line entering the bottom of the gate symbol (see next

slide)

Page 185

Three-State buffer

Three-state buffer

C A Y

----------------------

0 0 z

0 1 z

1 0 0

1 1 1

Page 186

Application of three-state buffer

Three-state buffers can be used to implement

multiplexer

Page 187

3. Larger Combinational Systems

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders and Priority Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays - ROMs, PLAs and PALs

3.9 Larger Examples

Page 188

3.8 Gate Arrays - ROM, PLA and PAL

PLA - Programmable Logic Arrays

PAL - Programmable Array Logic

ROM

Page 189

PLA - Programmable logic arrays

Pre-fabricated building block of many AND/OR gates

actually NOR or NAND

"personalized" by making or breaking connections among the gates

programmable array block diagram for sum of products form

inputs

AND

array

outputs

OR

array

product

terms

A B C Z1 Z2

m0 0 0 0 0 1

m1 0 0 1 0 0

m2 0 1 0 1 1

m3 0 1 1 0 0

m4 1 0 0 0 1

m5 1 0 1 1 0

m6 1 1 0 1 1

m7 1 1 1 1 0

Page 190

Before programming

All possible connections are available before "programming"

in reality, all AND and OR gates are NANDs

Page 191

After programming

Unwanted connections are "blown"

fuse (normally connected, break unwanted ones)

anti-fuse (normally disconnected, make wanted connections)

A B C

F1 F2 F3 F0

AB

B'C

AC'

B'C'

A

Page 192

PLA example

Multiple functions of A, B, C

F1 = A B C

F2 = A + B + C

F3 = A' B' C'

F4 = A' + B' + C'

F5 = A xor B xor C

F6 = A xnor B xnor C

A B C F1 F2 F3 F4 F5 F6

0 0 0 0 0 1 1 0 0

0 0 1 0 1 0 1 1 1

0 1 0 0 1 0 1 1 1

0 1 1 0 1 0 1 0 0

1 0 0 0 1 0 1 1 1

1 0 1 0 1 0 1 0 0

1 1 0 0 1 0 1 0 0

1 1 1 1 1 0 0 1 1

A'B'C'

A'B'C

A'BC'

A'BC

AB'C'

AB'C

ABC'

ABC

A B C

F1 F2 F3 F4 F5

F6

full decoder as for memory address

bits stored in memory

Page 193

PALs and PLAs

Programmable logic array (PLA)

what we've seen so far

unconstrained fully-general AND and OR arrays

Programmable array logic (PAL)

constrained topology of the OR array

innovation by Monolithic Memories

faster and smaller OR plane

a given column of the OR array

has access to only a subset of

the possible product terms

Page 194

ROM Read Only Memories

Two dimensional array of 1s and 0s

entry (row) is called a "word"

width of row = word-size

index is called an "address"

address is input

selected word is output

decoder

0 n-1

Address

2 -1

n

0

1 1 1 1

word[i] = 0011

word[j] = 1010

bit lines (normally pulled to 1 through

resistor selectively connected to 0

by word line controlled switches)

j

i

internal organization

word lines (only one

is active decoder is

just right for this)

Example:

10 address x 8 data ROM

2

10

words x 8 ROM

1024 words x 8 ROM

1k x 8 ROM

Page 195

ROM Read Only Memories

F0 = A' B' C + A B' C' + A B' C

F1 = A' B' C + A' B C' + A B C

F2 = A' B' C' + A' B' C + A B' C'

F3 = A' B C + A B' C' + A B C'

truth table

A B C F0 F1 F2 F3

0 0 0 0 0 1 0

0 0 1 1 1 1 0

0 1 0 0 1 0 0

0 1 1 0 0 0 1

1 0 0 1 0 1 1

1 0 1 1 0 0 0

1 1 0 0 0 0 1

1 1 1 0 1 0 0

block diagram

ROM

8 words x 4 bits/word

address outputs

A B C F0 F1 F2 F3

Combinational logic implementation (two-level canonical

form) using a ROM

Page 196

ROM structure

Similar to a PLA structure but with a fully decoded AND array

completely flexible OR array (unlike PAL)

n address lines

inputs

decoder

2

n

word

lines

outputs

memory

array

(2

n

words

by m bits)

m data lines

Page 197

3. Larger Combinational Systems

3.1 Delay in Combinational Logic Circuits

3.2 Adders and Other Arithmetic Circuits

3.3 Decoders

3.4 Encoders and Priority Encoders

3.5 Multiplexers

3.6 Demultiplexers

3.7 Three-State Gates

3.8 Gate Arrays-ROMs, PLAs and PALs

3.9 Larger Examples

Page 198

3.9 Larger Examples

1. Seven-segment displays

2. Comparator

Page 199

Comparator

1-bit full comparator:

1bit

Full

Comparator

a

i

b

i

G

i

L

i

E

i

i i i

i i i

i i i

b a E

b a L

b a G

=

=

=

.

. a

i

> b

i

G

i

=1

a

i

< b

i

L

i

=1

a

i

= bi E

i

=1

Page 200

Comparator

N-bit parallel comparator:

Page 201

Midterm examination (90)

1. Represent the following function in the canonical form SOP:

F(A,B,C)=(A+B)C

2. Use the Quine-McCluskey method to obtain the minimal sum for the

following function:

F(A,B,C,D,E)= (1,4,6,7,8,9,10,11,15)

3. Design 4x16 decoder using only 2x4 decoders.

4. Design a combinational logic circuit to calculate the following function:

M=N+3 where N is BCD number (Binary-Coded Decimal).

Page 202

Midterm examination 2 (90)

1. Represent the following function in the canonical form SOP and POS:

F(A,B,C)=C

2. Use the Quine-McCluskey method to obtain the minimal sum for the

following function:

F(A,B,C,D,E)= (1,4,6,7,8,11,12,13,15)

3. Using 3x8 decoder to implement the following function:

F(A,B,C) = AB + BC

4. Design a combinational logic circuit to calculate the following function:

M=N+5 where N is BCD number (Binary-Coded Decimal).

Page 203

Chapter 4.

Sequential Systems

Page 204

4. Sequential Systems

4.1 Definitions

4.2 State Tables and Diagrams

4.3 Latches and Flip Flops

4.4 Analysis of Sequential Systems

4.5 Design of Sequential Systems

4.6 Solving Larger Sequential Problems

Page 205

4.1 Definitions

Combinatorial circuit is memoryless.

In a circuit with memory, an output value at t

n+1

must be a

function not only of the inputs at t

n+1

but also of the outputs at

t

n

.

To achieve this, the circuit must have some feedback

connections from its outputs to its inputs.

A circuit with memory is a combinatorial circuit

incorporating some feedback connections.

Page 206

Feedback and memory devices

To implement feedback, signals are fed back from outputs to

inputs using memory devices.

A memory device stores an output value at time t

n

so that it

can be input to the circuit at t

n+1

.

But then, output at t

n

depends on input at t

n-1

, which in turn

depends on t

n-2

The circuit maps input sequences to output sequences

Page 207

Sequential circuit model

Circuits with memory are called sequential circuits.

Combinatorial

circuit

.

.

.

x

1

x

2

x

n

.

.

.

z

1

z

2

Memory

device

Memory

device

.

.

.

Y

k

Y

1

y

k

y

1

Circuit inputs Circuit outputs

Present state

Next state

Page 208

Sequential circuit model

Mealy model:

X : finite inputs. m inputs: x

1

,x

2

...,x

m

S : finite states. n states: s

1

,s

2

...,s

n

Y: finite outputs. l outputs: y

1

,y

2

...,y

l

Fs: state function. s = Fs(X,S)

Fy : output function. y = Fy(X,S)

Moore: ~Mealy

Difference: Fy = Fy(S)

Page 209

Asynchronous/Synchronous sequential circuits

The timing of the signal in the circuit determine two types of

sequential circuits:

Synchronous

Asynchronous.

Page 210

Synchronous sequential circuits

In a synchronous sequential circuit, the state can change only at

discrete instants of time.

To achieve that, the circuit uses a timing device, called a clock

generator, that produce trains of periodic or aperiodic clock pulses.

The clock pulses are input to the memory devices so that they can

change state only in response to the arrival of a pulse and only

once for each pulse occurrence.

The operation of the circuit is synchronized with the clock pulse input.

Page 211

Asynchronous sequential circuits

The behavior of an asynchronous sequential circuit depends

only on the order in which the inputs change and can be

affected at any instant of time.

There is no timing device in asynchronous sequential circuit

(unclocked memory).

Page 212

4. Sequential Systems

4.1 Definitions

4.2 State Tables and Diagrams

4.3 Latches and Flip Flops

4.4 Analysis of Sequential Systems

4.5 Design of Sequential Systems

4.6 Solving Larger Sequential Problems

Page 213

State diagram

Depict graphically the operation of a sequential circuit.

Mealy state diagram

a b c d

0/0 1/0 0/0

0/0

0/0

1/0

1/1

Page 214

Example of state diagram

A B C D

0/0

1/0

0/0

1/0

1/0

0/0

0/0

1/1

Example: a sequential circuit is used to detect the string

0101 from one input.

Page 215

State diagram

Depict graphically the operation of a sequential circuit.

Moore state diagram

a/0

b/0

c/0

d/0

e/1

f/1

0

1

0

0

0

0

0

1

1

1

1

1

Page 216

State table

State table presents in a tabular form the same information

contained in the state diagram.

Mealy state table

Moore state table

Page 217

Mealy state table

PS NS Output (z)

x=0 x=1 x=0 x=1

a b a 0 0

b b c 0 0

c d a 0 0

d b c 0 1

PS NS/Output (z)

x=0 x=1

a b/0 a/0

b b/0 c/0

c d/0 a/0

d b/0 c/1

PS: Present State

NS: Next State

k memory devices => 2

k

rows

n circuit inputs => NS portion contains 2

n

columns

Output portion also contains 2

n

columns

a b c d

0/0 1/0 0/0

0/0

0/0

1/0

1/1

Page 218

Moore state table

PS NS Output

x=0 x=1 z

a b a 0

b b c 0

c d c 0

d d e 0

e f e 1

f f a 1

The output portion always contains a single column.

The entry at the intersection of any row with the output column indicates the

output values corresponding to the PS associated with that row.

a/0

b/0

c/0

d/0

e/1

f/1

0

1

0

0

0

0

0

1

1

1

1

1

Page 219

Incompletely specified Mealy state table

Two inputs: x1,x2

A single output: z

PS NS/Output (z)

00 01 11 10

a -/- c/1 b/- e/1

b e/0 -/- -/- -/-

c f/0 f/1 -/- -/-

d a/- -/- e/- b/1

e -/- f/0 d/1 a/0

f c/0 -/- c/1 b/0

Page 220

4. Sequential Systems

4.1 Definitions

4.2 State Tables and Diagrams

4.3 Latches and Flip Flops

4.4 Analysis of Sequential Systems

4.5 Design of Sequential Systems

4.6 Solving Larger Sequential Problems

Page 221

4.3. Latches and Flip-Flops

Simplest memory devices: Delay element

T

Yi

yi

yi(t+T) = Yi(t)

T

Yi

yi

In practice, we dont have to actually insert delay elements

because propagation time delays between the inputs and

the outputs of the combinatorial part of the circuit provide

sufficient delay across the feedback loops.

Page 222

4.3. Latches and Flip-Flops

Bistable devices:

Two stable states:

Q=0 : the device is reset (reset state)

Q=1: the device is set (set state)

A bistable device remains in one of two states indefinitely until directed

by an input signal to change state.

Two types:

Latch

Flip-flop

Page 223

SR Latch

Two inputs: S (set), R (reset)

Two complementary outputs: Q, Q

S Q

R Q

Q

Q'

S

R

S R Q Q

+

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 -

1 1 1 -

Indeterminate

Next state

Current state

Q = (R+Q)

Q= (S+Q)

Page 224

4.3. Latches and Flip-Flops

Latch: transparency property:

Change state when the input values change

The new output state is delayed only by the propagation time delays of

the gates between inputs and outputs of the latch.

Used to implement the memory part of asynchronous circuits.

Flip-flop: no transparency property

Has a control (triggering) input, called clock.

The state change only in response to a transition of a clock pulse at

clock input.

Used to implement memory part of synchronous circuits

Page 225

SR Latch

S Q

R Q

Q

Q'

S

R

S R Q

+

0 0 Q

0 1 0

1 0 1

1 1 Indeterminate

Equivalent characteristic table

SR=00 => Output no change

A logic 1 at inputs can change outputs states

=> active-HIGH latch

Page 226

SR Latch

S Q

R Q

Q

Q'

S

R

active-HIGH SR Latch

S Q

R Q

S

R

Q

Q'

active-LOW SR Latch

Page 227

SR Latch

Timing chart (NOR implementation)

S

R

Q

Q

set reset reset set

Q

Q'

S

R

Page 228

SR Latch

Timing chart (NAND implementation)

Q

Q

S

R

set reset set reset

S

R

Q

Q'

Page 229

SR Latch

R

S

Q

Circuit showing feedback

Q

+

= RQ + RS

SR=0 => Q

+

= RQ + RS + RS = RQ + S

for active-HIGH SR Latch

Q Q

+

S R

0 0 0 -

0 1 1 0

1 0 0 1

1 1 - 0

Excitation table

Page 230

D Latch

D Q

Q

S Q

R Q

D

D Q

*

0 0

1 1

Q Q

*

D

0 0 0

0 1 1

1 0 0

1 1 1

Graphic symbol Implementation using SR Latch

Equivalent characteristic table

Excitation table

Q

*

= D

Page 231

Gated Latches

S Q

E

R Q

S

R

Q

Q'

E

E: Enable input control

The latch will not change state as long as E=0

E=1 SR=10 => Set

E=1 SR=01 => Reset

The operation of latch is synchronized

with the E input => E: synchronous input

A latch with synchronous input is called

gated latch.

Page 232

Flip-flops

Latches implement memory part in asynchronous sequential

circuits