Professional Documents

Culture Documents

Analog Device Micro Converter

Uploaded by

shailesh0 ratings0% found this document useful (0 votes)

115 views20 pagesThis document describes the Micro Converter analog-to-digital converter (ADC) chip from Analog Devices. It has an embedded high-speed 8052 microcontroller core and integrates an 8-channel 12-bit ADC, dual digital-to-analog converters (DACs), and other peripherals onto a single chip. The ADC can operate at speeds up to 420 kilosamples per second and features on-chip voltage reference, calibration functions, and direct memory access controller to rapidly transfer conversion results. The chip supports various applications including optical networking, instrumentation, and data acquisition systems.

Original Description:

ppt

Original Title

ADuC842

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document describes the Micro Converter analog-to-digital converter (ADC) chip from Analog Devices. It has an embedded high-speed 8052 microcontroller core and integrates an 8-channel 12-bit ADC, dual digital-to-analog converters (DACs), and other peripherals onto a single chip. The ADC can operate at speeds up to 420 kilosamples per second and features on-chip voltage reference, calibration functions, and direct memory access controller to rapidly transfer conversion results. The chip supports various applications including optical networking, instrumentation, and data acquisition systems.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

115 views20 pagesAnalog Device Micro Converter

Uploaded by

shaileshThis document describes the Micro Converter analog-to-digital converter (ADC) chip from Analog Devices. It has an embedded high-speed 8052 microcontroller core and integrates an 8-channel 12-bit ADC, dual digital-to-analog converters (DACs), and other peripherals onto a single chip. The ADC can operate at speeds up to 420 kilosamples per second and features on-chip voltage reference, calibration functions, and direct memory access controller to rapidly transfer conversion results. The chip supports various applications including optical networking, instrumentation, and data acquisition systems.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

You are on page 1of 20

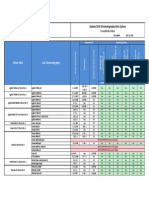

AD C842

Micro Converter (Analog Device)

12-Bit ADCs and DACs with

Embedded High Speed 62-kB Flash MCU

FEATURES

Increased performance:

Single-cycle 20 MIPS 8052 core

High speed 420 kSPS 12-bit ADC

Increased memory:

Up to 62 kB on-chip Flash/EE program memory

4 kB on-chip Flash/EE data memory

Analog I/O:

8-channel, 420 kSPS high accuracy, 12-bit ADC On-chip, 15 ppm/C

voltage reference

DMA controller, high speed ADC-to-RAM capture

Two 12-bit voltage output DACs

Dual output PWM - DACs

On-chip temperature monitor function

FEATURES (CONTINUE)

8052 based core:

8051 compatible instruction set (20 MHz max)

32 kHz external crystal, on-chip programmable PLL

12 interrupt sources, 2 priority levels

Dual data pointers, extended 11-bit stack pointer

On-chip peripherals:

Time interval counter (TIC)

UART, I2C, and SPI Serial I/O

Watchdog timer (WDT)

Power supply monitor (PSM)

Power ON reset (POR)

Development tools:

IDE based assembly and C source debugging

APPLICATIONS

Optical networking laser power control

Base station systems

Precision instrumentation, smart sensors

Transient capture systems

DAS and communications systems

GENERAL DESCRIPTION

It is a complete smart transducer front end, that integrates

a high performance self calibrating multichannel ADC,

a dual DAC, and

an optimized single-cycle 20 MHz 8-bit MCU (8051 instruction set

compatible) on a single chip.

The ADuC842 uses a 32 kHz crystal with an on-chip PLL generating a

programmable core clock up to 16.78 MHz.

The microcontroller is an optimized 8052 core offering up to 20 MIPS

peak performance.

GENERAL DESCRIPTION (CONTINUE)

Three different memory options are available

4 kB of nonvolatile Flash/EE data memory

256 bytes RAM

2 kB of extended RAM (XRAM)

Offering up to 62 kB of nonvolatile Flash/EE program memory.

The I2C and SPI interfaces share some of the same pins.

However, there is an option to allow SPI operate separately on P3.3,

P3.4, and P3.5, while I2C uses the standard pins.

The I2C interface has also been enhanced to offer repeated start,

general call, and quad addressing.

PIN DIAGRAM

PIN DESCRIPTION

Mnemonic Type Function

DVDD P Digital Positive Supply Voltage. 3 V or 5 V nominal.

AVDD P Analog Positive Supply Voltage. 3 V or 5 V nominal.

CREF I/O

Decoupling Input for On-Chip Reference. Connect a 0.47 F capacitor between

this pin and AGND.

VREF NC

Not connected. This was reference out on the ADuC812; the CREF pin should be

used instead.

AGND G Analog Ground. Ground reference point for the analog circuitry.

P1.0P1.7 I

Port 1 is an 8-bit input port only. Unlike other ports, Port 1 defaults to analog

input mode. To configure any of these port pins as a digital input, write a 0 to the

port bit.

ADC0

ADC7

I

Analog Inputs. Eight single-ended analog inputs. Channel selection is via

ADCCON2 SFR.

T2 I

Timer 2 Digital Input. Input to Timer/Counter 2. When enabled, Counter 2 is

incremented in response to a 1-to-0 transition of the T2 input.

T2EX I

Digital Input. Capture/reload trigger for Counter 2; also functions as an up/down

control input for Counter 2.

SS I Slave Select Input for the SPI Interface.

SDATA I/O User Selectable, I2C Compatible, or SPI Data Input/output Pin.

SCLOCK I/O Serial Clock Pin for I2C Compatible or for SPI Serial Interface Clock.

MOSI I/O SPI Master Output/Slave Input Data I/O Pin for SPI Interface.

MISO I/O SPI Master Input/Slave Output Data I/O Pin for SPI Serial Interface.

PIN DESCRIPTION (CONTINUE)

Mnemonic Type Function

DAC0 O Voltage Output from DAC0. This pin is a no connect on the ADuC843.

DAC1 O Voltage Output from DAC1. This pin is a no connect on the ADuC843.

RESET I

Digital Input. A high level on this pin for 24 master clock cycles while the

oscillator is running resets the device.

P3.0P3.7 I/O

Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have

1s written to them are pulled high by the internal pull-up resistors, and in that

state can be used as inputs. As inputs, Port 3 pins being pulled externally low

source current because of the internal pull-up resistors. Port 3 pins also contain

various secondary functions, which are described below.

PWMC I PWM Clock Input.

PWM0 O

PWM0 Voltage Output. PWM outputs can be configured to use Ports 2.6 and 2.7

or Ports 3.4 and 3.3.

PWM1 O PWM1 Voltage Output. See the CFG841/CFG842 register for further information.

RxD I/O

Receiver Data Input (Asynchronous) or Data Input/output (Synchronous) of the

Serial (UART) Port.

TxD O

Transmitter Data Output (Asynchronous) or Clock Output (Synchronous) of the

Serial (UART) Port.

INT0 I

Interrupt 0. Programmable edge or level triggered interrupt input; can be

programmed to one of two priority levels. This pin can also be used as a gate

control input to Timer 0.

INT1 I

Interrupt 1. Programmable edge or level triggered interrupt input; can be

programmed to one of two priority levels. This pin can also be used as a gate

control input to Timer 1.

PIN DESCRIPTION (CONTINUE)

Mnemonic Type Function

T0 I Timer/Counter 0 Input.

T1 I Timer/Counter 1 Input.

CONVST I

Active Low Convert Start Logic Input for the ADC Block when the External

Convert Start Function is Enabled. A low-to-high transition on this input puts the

track-and-hold into hold mode and starts the conversion.

EXTCLK I Input for External Clock Signal. Has to be enabled via the CFG842 register.

WR O

Write Control Signal, Logic Output. Latches the data byte from Port 0 into the

external data memory.

RD O Read Control Signal, Logic Output. Enables the external data memory to Port 0.

XTAL2 O Output of the Inverting Oscillator Amplifier.

XTAL1 I Input to the Inverting Oscillator Amplifier.

DGND G Digital Ground. Ground reference point for the digital circuitry.

P2.0P2.7

(A8A15)

(A16A23)

I/O

Port 2 is a bidirectional port with internal pull-up resistors. Port 2 pins that have

1s written to them are pulled high by the internal pull-up resistors, and in that

state can be used as inputs. As inputs, Port 2 pins being pulled externally low

source current because of the internal pull-up resistors. Port 2 emits the middle

and high-order address bytes during accesses to the external 24-bit external data

memory space.

PIN DESCRIPTION (CONTINUE)

Mnemonic Type Function

PSEN O

Program Store Enable, Logic Output. This pin remains low during internal

program execution. PSEN is used to enable serial download mode when pulled

low through a resistor on power-up or reset. On reset this pin will momentarily

become an input and the status of the pin is sampled. If there is no pull down

resistor in place the pin will go momentarily high and then user code will execute.

If a pull-down resistor is in place, the embedded serial download/debug kernel will

execute.

ALE O

Address Latch Enable, Logic Output. This output is used to latch the low byte and

page byte for 24-bit address space accesses of the address into external data

memory.

EA I

External Access Enable, Logic Input. When held high, this input enables the

device to fetch code from internal program memory locations. The parts do not

support external code memory. This pin should not be left floating.

P0.7P0.0

(A0-A7)

I/O

Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written

to them float, and in that state can be used as high impedance inputs. Port 0 is

also the multiplexed low-order address and data bus during accesses to external

data memory. In this application, it uses strong internal pull-ups when emitting 1s.

FUNCTIONAL BLOCK DIAGRAM

ADC

The ADC conversion block incorporates a fast, 8-channel, 12-bit,

single-supply ADC.

This block provides the user with multichannel mux, track-and-hold,

on-chip reference, calibration features, and ADC.

All components in this block are easily configured via a 3-register SFR

interface.

The ADC converter consists of a conventional successive

approximation converter based around a capacitor DAC.

The converter accepts an analog input range of 0 V to VREF.

A high precision, 15 ppm, low drift, factory calibrated 2.5 V reference

is provided on-chip.

INTERNAL ADC STRUCTURE AND

ADC TRANSFER FUNCTION

ADC (CONTINUE)

Single-step or continuous conversion modes can be initiated in

software or alternatively by applying a convert signal to an external

pin.

The ADC may be configured to operate in a DMA mode whereby the

ADC block continuously converts and captures samples to an

external RAM space without any interaction from the MCU core.

This automatic capture facility can extend through a 16 MB external

data memory space.

ADC (CONTINUE)

Once configured via the ADCCON 13 SFRs, the ADC converts the

analog input and provides an ADC 12-bit result word in the

ADCDATAH/L SFRs.

The top 4 bits of the ADCDATAH SFR are written with the channel

selection bits to identify the channel result.

The format of the ADC 12-bit result word is shown in Figure.

CALIBRATING THE ADC

Two hardware calibration modes are provided, which can be easily

initiated by user software.

The ADCCON3 SFR is used to calibrate the ADC. Bit 1 (typical) and

CS3 to CS0 (ADCCON2) set up the calibration modes.

Device calibration can be initiated to compensate for significant

changes in operating condition frequency, analog input range,

reference voltage, and supply voltages.

In this calibration mode, offset calibration uses internal AGND

selected via ADCCON2 register Bits CS3 to CS0 (1011), and gain

calibration uses internal VREF selected by Bits CS3 to CS0 (1100).

Offset calibration should be executed first, followed by gain

calibration. System calibration can be initiated to compensate for both

internal and external system errors.

CALIBRATING THE ADC (CONTINUE)

To perform system calibration by using an external reference, tie the

system ground and reference to any two of the six selectable inputs.

Enable external reference mode (ADCCON1.6).

Select the channel connected to AGND via Bits CS3 to CS0 and

perform system offset calibration.

Select the channel connected to VREF via Bits CS3 to CS0 and

perform system gain calibration.

DAC

The ADC842 incorporate two 12-bit voltage output DACs on-chip.

Each has a rail-to-rail voltage output buffer capable of driving

10k/100pF. Each has two selectable ranges, 0 V to VREF (the internal

band gap 2.5 V reference) and 0 V to AVDD.

Each can operate in 12-bit or 8-bit mode.

ON-CHIP PLL

The ADuC842 is intended for use with a 32.768 kHz watch crystal.

A PLL locks onto a multiple (512) of this to provide a stable 16.78 MHz

clock for the system.

The core can operate at this frequency or at binary submultiples of it

to allow power saving in cases where maximum core performance is

not required. The default core clock is the PLL clock divided by 8 or

2.097152 MHz.

The ADC clocks are also derived from the PLL clock, with the

modulator rate being the same as the crystal oscillator frequency. The

preceding choice of frequencies ensures that the modulators and the

core are synchronous, regardless of the core clock rate. The PLL

control register is PLLCON.

You might also like

- Softening PointDocument8 pagesSoftening PointMauricio CruzNo ratings yet

- TAXT PlusDocument7 pagesTAXT Plusdéborah_rosalesNo ratings yet

- BioStamp 2C - BST2C02Document3 pagesBioStamp 2C - BST2C02Resilient TechnologiesNo ratings yet

- VpodDocument2 pagesVpodAkash SoodNo ratings yet

- Introduction of KUT650 Ultrasonic Flaw Detector - HongTuoDocument3 pagesIntroduction of KUT650 Ultrasonic Flaw Detector - HongTuolovaldes62No ratings yet

- An Evaluation System Interfacing The TSL230/TSL235/TSL245 Light-To - Frequency Converters To A MicrocontrollerDocument15 pagesAn Evaluation System Interfacing The TSL230/TSL235/TSL245 Light-To - Frequency Converters To A MicrocontrollerOscarNo ratings yet

- Manual de Operación Densimetro Mettler Toledo DE40Document96 pagesManual de Operación Densimetro Mettler Toledo DE40Laura GuarguatiNo ratings yet

- Counting Scale: FC-50Ki FC-20Ki FC-10Ki FC-5000iDocument64 pagesCounting Scale: FC-50Ki FC-20Ki FC-10Ki FC-5000iHigo UcNo ratings yet

- Mil STD 883 - 1014Document13 pagesMil STD 883 - 1014dados_fNo ratings yet

- Essae Scale Utility ManualDocument11 pagesEssae Scale Utility ManualnstomarNo ratings yet

- ADM 4280 C - V2说明书Document5 pagesADM 4280 C - V2说明书l1f3b00kNo ratings yet

- Motor LogicDocument48 pagesMotor LogicJose LunaNo ratings yet

- HDT 3 & 6 VICAT Instrument for Quality Control TestingDocument6 pagesHDT 3 & 6 VICAT Instrument for Quality Control TestingDiego Fernado AvendañoNo ratings yet

- Ascott Manual S Ip RangeDocument80 pagesAscott Manual S Ip Rangejeremias100% (1)

- Inertial Measurement Unit in ArduinoDocument7 pagesInertial Measurement Unit in ArduinoWhizzWrNo ratings yet

- Datos TecnicosDocument2 pagesDatos TecnicosCeleynes RTNo ratings yet

- Safety (IEC) Report ZK-D3180S ZK-D2180S ZK-D1065SDocument72 pagesSafety (IEC) Report ZK-D3180S ZK-D2180S ZK-D1065SOscar Danilo Erazo Pecillo100% (1)

- MAP17-ST Catalogue PDFDocument277 pagesMAP17-ST Catalogue PDFDwi PanjayaNo ratings yet

- St332b XDSL Tester v1.1 User ManualDocument55 pagesSt332b XDSL Tester v1.1 User ManualFHERNo ratings yet

- B-324 Operationmanual en D LowresDocument32 pagesB-324 Operationmanual en D LowresOchie Yusuf100% (1)

- Astm D 2269Document3 pagesAstm D 2269Faisal RahmadNo ratings yet

- Espectofotometro Perkin Elmer Lamdad 3BDocument6 pagesEspectofotometro Perkin Elmer Lamdad 3BRonys HernandezNo ratings yet

- Wire Pull Test StandardsDocument1 pageWire Pull Test Standardsmst1ckmaNo ratings yet

- Ficha Tecnica Manometro Modelo 1320 RithermDocument2 pagesFicha Tecnica Manometro Modelo 1320 RithermSmith Alexito HuamanNo ratings yet

- Calibration of Radiation Thermometers below Silver PointDocument41 pagesCalibration of Radiation Thermometers below Silver PointebalideNo ratings yet

- PosiTector 6000 Manual PDFDocument39 pagesPosiTector 6000 Manual PDFPepe PedroNo ratings yet

- Calibration Procedure FOR Power Meter Nrp2 Opt B1: Technical ManualDocument4 pagesCalibration Procedure FOR Power Meter Nrp2 Opt B1: Technical Manualentico100% (1)

- Gas Book PLCDocument119 pagesGas Book PLCLucas MeloNo ratings yet

- CS200 PreinstallDocument7 pagesCS200 PreinstallEdariel Huaman AquinoNo ratings yet

- ASU-24005g: Broadband Wireless Access Point Solutions (AP/Client/Bridge/Repeater) ModelDocument2 pagesASU-24005g: Broadband Wireless Access Point Solutions (AP/Client/Bridge/Repeater) Modelmaecassiopeia100% (1)

- DLC32 Wiring ManualDocument14 pagesDLC32 Wiring ManualPaulo F CunhaNo ratings yet

- Application Report DMA 80 Evo Coal USREV061019Document4 pagesApplication Report DMA 80 Evo Coal USREV061019Roni GustiwaNo ratings yet

- Black Body Temperature Source Bcal 502-V1Document6 pagesBlack Body Temperature Source Bcal 502-V1TPM BMPNo ratings yet

- s2 Puma Petro Brochure Doc-b80-Exs019 en HighDocument8 pagess2 Puma Petro Brochure Doc-b80-Exs019 en HighIan RidzuanNo ratings yet

- SPUD 604 ManualDocument37 pagesSPUD 604 ManualfbarrazaisaNo ratings yet

- ELAN Improvements Service Training RevBDocument19 pagesELAN Improvements Service Training RevBJOSE ABADNo ratings yet

- 500 104 MTESTQuattroCalibration Rev2Document5 pages500 104 MTESTQuattroCalibration Rev2Javier RochaNo ratings yet

- BioChem Pinch Valve User ManualDocument33 pagesBioChem Pinch Valve User ManualthynameisraymondNo ratings yet

- Galaxie 2010 Chromatography CompatibilityDocument3 pagesGalaxie 2010 Chromatography CompatibilitymardonioandradeNo ratings yet

- Mitutoyo 183-109 Data SheetDocument1 pageMitutoyo 183-109 Data SheetLaboratorio AveNo ratings yet

- MM850242-3 MicroCal PDocument54 pagesMM850242-3 MicroCal Pctmtectrol100% (1)

- Chemical Analysis Group Document Provides Helpful Cabling DiagramsDocument21 pagesChemical Analysis Group Document Provides Helpful Cabling DiagramsBaroto Setyo SuryoNo ratings yet

- Shimadzu Spectrophotometer UV1700 & UV1650PCDocument24 pagesShimadzu Spectrophotometer UV1700 & UV1650PCAldi Igniel100% (1)

- Equotip 3Document6 pagesEquotip 3raveeceeNo ratings yet

- Manual Vertex 70vsDocument156 pagesManual Vertex 70vsbbtnNo ratings yet

- Charge-Sensitive PreamplifierWith Continuous ResetDocument5 pagesCharge-Sensitive PreamplifierWith Continuous ResetGaus87No ratings yet

- SotaxDocument2 pagesSotaxI SunnahNo ratings yet

- Tinius Olsen - Ref 30 - 60000lb Cal Super L - B117GDocument8 pagesTinius Olsen - Ref 30 - 60000lb Cal Super L - B117Gjr_satish6965No ratings yet

- JCGM - 106 - 2012 (M C 7)Document14 pagesJCGM - 106 - 2012 (M C 7)Quốc Tuấn ĐặngNo ratings yet

- Ohaus Pa214Document34 pagesOhaus Pa214Cesar Emiliano GeraceNo ratings yet

- Jai Balaji Limit Switches PDFDocument2 pagesJai Balaji Limit Switches PDFSuresh kannanNo ratings yet

- Manuals - Omega ABU - Including Pumpset and Smart Pumps Master Copy - Issue Level 09Document118 pagesManuals - Omega ABU - Including Pumpset and Smart Pumps Master Copy - Issue Level 09manuelNo ratings yet

- Test Report No. 7191250395-EEC21-WBH: Dated 07 Jan 2021Document5 pagesTest Report No. 7191250395-EEC21-WBH: Dated 07 Jan 2021edwin morrisonNo ratings yet

- EPOCH 600 Training Presentation 3-2014Document193 pagesEPOCH 600 Training Presentation 3-2014Raul MedinaNo ratings yet

- Master StationDocument138 pagesMaster StationWilmer Quishpe AndradeNo ratings yet

- Stanhope Seta Product Catalogue 2010 72Document180 pagesStanhope Seta Product Catalogue 2010 72Reinaldo Alexandre Fonseca100% (3)

- IEEE 1149-7 Embedded TutorialDocument10 pagesIEEE 1149-7 Embedded TutorialDarshan PatelNo ratings yet

- Enhanced 8-Bit Microcontroller With 32 KB Flash Memory: AT89C51AC2 T89C51AC2Document121 pagesEnhanced 8-Bit Microcontroller With 32 KB Flash Memory: AT89C51AC2 T89C51AC2mukhi2006No ratings yet

- Industrial Fault Indication System With Over Voltage Over TemperatureDocument46 pagesIndustrial Fault Indication System With Over Voltage Over Temperaturedivanshu16decNo ratings yet

- AtMega32 Data SheetDocument313 pagesAtMega32 Data SheetSumeet TiwanaNo ratings yet

- Chapter-1. Introduction To Communication Systems:-: (April-2010) (07) (2.1 & 2.2)Document6 pagesChapter-1. Introduction To Communication Systems:-: (April-2010) (07) (2.1 & 2.2)shaileshNo ratings yet

- Lecture12 TimersDocument20 pagesLecture12 TimersshaileshNo ratings yet

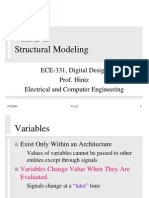

- Vhdl-Ii Structural Modeling: ECE-331, Digital Design Prof. Hintz Electrical and Computer EngineeringDocument33 pagesVhdl-Ii Structural Modeling: ECE-331, Digital Design Prof. Hintz Electrical and Computer EngineeringshaileshNo ratings yet

- Basic Fpga Arch XilinxDocument45 pagesBasic Fpga Arch Xilinxdeepak_thakur_0015822No ratings yet

- Altera Device Package Information DatasheetDocument514 pagesAltera Device Package Information DatasheetshaileshNo ratings yet

- Cadance OrCAD LayoutDocument32 pagesCadance OrCAD LayoutshaileshNo ratings yet

- S5PV210 Rev1.0 Section1-3Document559 pagesS5PV210 Rev1.0 Section1-3mrezagholiNo ratings yet

- Renesas RX62N MicrocontrollerDocument524 pagesRenesas RX62N MicrocontrollereditronikxNo ratings yet

- HC05Document9 pagesHC05suraj kumarNo ratings yet

- VS1003B DatasheetDocument61 pagesVS1003B Datasheetjohndoe1395No ratings yet

- PIC18 (L) F24/25K42: 28-Pin, Low-Power, High-Performance Microcontrollers With XLP TechnologyDocument785 pagesPIC18 (L) F24/25K42: 28-Pin, Low-Power, High-Performance Microcontrollers With XLP TechnologyRicardo UrioNo ratings yet

- NuMicro Nano100 (B) Series Product Brief en V1.00Document72 pagesNuMicro Nano100 (B) Series Product Brief en V1.00HanhoaiNguyenNo ratings yet

- 3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xDocument56 pages3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xYusuf Ilker öztürkNo ratings yet

- MC9S08SH32Document328 pagesMC9S08SH32jahenNo ratings yet

- Manuale Di Programmazione Stm32Document856 pagesManuale Di Programmazione Stm32Miriam AstrologoNo ratings yet

- SPI Protocol For STPM01 - STPM10 Metering DevicesDocument23 pagesSPI Protocol For STPM01 - STPM10 Metering DevicesMontassar Ben Abdallah100% (1)

- PIC32-WEB Development Board Users Manual: All Boards Produced by Olimex Are ROHS CompliantDocument20 pagesPIC32-WEB Development Board Users Manual: All Boards Produced by Olimex Are ROHS CompliantFernando Piedade100% (3)

- Practical 4Document6 pagesPractical 4Louis StephenNo ratings yet

- FM25V05 PDFDocument16 pagesFM25V05 PDFMichaelAzizNo ratings yet

- MSP 430 G 2452Document63 pagesMSP 430 G 2452Marckius GarcíaNo ratings yet

- Tutorial Simulation and Code Generation of TI InstaSPIN Using DRV8305 EVMDocument22 pagesTutorial Simulation and Code Generation of TI InstaSPIN Using DRV8305 EVMbajarfileNo ratings yet

- Atmega 328 PDocument344 pagesAtmega 328 PAlexandre100% (1)

- Raspberry Pi - Expansion Boards (Elinux)Document30 pagesRaspberry Pi - Expansion Boards (Elinux)sher123No ratings yet

- User Manual For 8051 Development KitDocument26 pagesUser Manual For 8051 Development KitArokiaraj RajNo ratings yet

- Arm7 ExamplesDocument16 pagesArm7 ExamplescontrasterNo ratings yet

- Datasheet csr8645Document114 pagesDatasheet csr8645Eric Lúcio Silva RodriguesNo ratings yet

- 1Document29 pages1Ronniel de RamosNo ratings yet

- ILI9225BDocument118 pagesILI9225BSpecShareNo ratings yet

- LCD TELEVISION SERVICE MANUAL CHASSIS LS03Document30 pagesLCD TELEVISION SERVICE MANUAL CHASSIS LS03Luděk Csiba100% (1)

- CMX7164FI 2 4 2dsDocument91 pagesCMX7164FI 2 4 2dsbilou57No ratings yet

- LPC2138Document39 pagesLPC2138yuvaraja_703No ratings yet

- Autosar Sws Spi HandlerdriverDocument76 pagesAutosar Sws Spi Handlerdriverkrnl386No ratings yet

- 6541Document144 pages6541naveenp85No ratings yet

- CRM100 - Precision Navigation and Pointing GyroscopeDocument34 pagesCRM100 - Precision Navigation and Pointing GyroscopeStanley Ochieng' OumaNo ratings yet

- Shield WiFi 802.11b PDFDocument8 pagesShield WiFi 802.11b PDFmilenyNo ratings yet

- Raspberry Pi As Internet of Things Hardware Performances and ConstraintsDocument6 pagesRaspberry Pi As Internet of Things Hardware Performances and ConstraintsescanusNo ratings yet