Professional Documents

Culture Documents

Process

Uploaded by

YashCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Process

Uploaded by

YashCopyright:

Available Formats

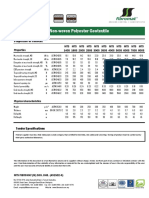

CMOS

Manufacturing

Process

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

CMOS Process

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Circuit Under Design

VDD VDD

M2

M4

Vin Vout Vout2

M1 M3

This two-inverter circuit (of Figure 3.25 in the text) will be

manufactured in a twin-well process.

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Circuit Layout

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Process Flow

These slides only present only a couple of snapshots of the

manufacturing process for the circuits presented in the textbook.

For a complete overview of all 62 steps, please refer to:

http://tanqueray.eecs.berkeley.edu/~ehab/inv.html.

Credits for these pictures go to Ehab Hakeem, Prof. Andrew Neureuther

and the Simpl program.

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Start Material

A

Starting wafer: n-type with

13 3

A doping level = 10 /cm

* Cross-sections will be

shown along vertical line A-A

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

N-well Construction

(1) Oxidize wafer

(2) Deposit silicon nitride

(3) Deposit photoresist

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

N-well Construction

(4) Expose resist using n-well

mask

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

N-well Construction

(5) Develop resist

(6) Etch nitride and

(7) Grow thick oxide

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

N-well Construction

(8) Implant n-dopants (phosphorus)

(up to 1.5 mm deep)

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

P-well Construction

Repeat previous steps

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Grow Gate Oxide

0.055 mm thin

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Grow Thick Field Oxide

0.9 mm thick

Uses Active Area mask

Is followed by

threshold-adjusting implants

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Polysilicon layer

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Source-Drain Implants

n+ source-drain implant

(using n+ select mask)

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Source-Drain Implants

p+ source-drain implant

(using p+ select mask)

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Contact-Hole Definition

(1) Deposit inter-level

dielectric (SiO2) 0.75 mm

(2) Define contact opening

using contact mask

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Aluminum-1 Layer

Aluminum evaporated

(0.8 mm thick)

followed by other metal

layers and glass

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

Advanced Metalization

Digital Integrated Circuits Manufacturing Process Prentice Hall 1995

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Ms-Mech-10, Ms Fabrication of PipingDocument13 pagesMs-Mech-10, Ms Fabrication of PipingBabar Manzoor GhauriNo ratings yet

- IGCSE Topical Past Papers PhysicsDocument64 pagesIGCSE Topical Past Papers PhysicsHubert DMelloNo ratings yet

- Lifetime Extension Steam TurbineDocument10 pagesLifetime Extension Steam Turbineramakantinamdar100% (1)

- SATIP-H-100-01 Rev 8Document4 pagesSATIP-H-100-01 Rev 8SajjadPervaiz100% (2)

- Chapter 6-Agitated LiquidDocument48 pagesChapter 6-Agitated LiquidAhmad SiddiqNo ratings yet

- Astm B187Document9 pagesAstm B187Plata Elpidio100% (3)

- CN 8sem 1Document1 pageCN 8sem 1YashNo ratings yet

- Lecture 1Document23 pagesLecture 1Vikas DhimanNo ratings yet

- Introduction To CMOS VLSI Design: Credits: David HarrisDocument62 pagesIntroduction To CMOS VLSI Design: Credits: David HarrisYashNo ratings yet

- ProcedureDocument6 pagesProcedureYashNo ratings yet

- Iisc CutOff Report For M Tech-WebDocument4 pagesIisc CutOff Report For M Tech-WebAlok Bikash SadangiNo ratings yet

- Introduction To CMOS VLSI Design: Credits: David HarrisDocument62 pagesIntroduction To CMOS VLSI Design: Credits: David HarrisYashNo ratings yet

- Environmental Engineering - Civil Engineering - McGill UniversityDocument4 pagesEnvironmental Engineering - Civil Engineering - McGill Universityamrin jannatNo ratings yet

- Static Analysis of VMC Spindle For Maximum Cutting Force: Mahesh M. Ghadage Prof. Anurag V. KarandeDocument5 pagesStatic Analysis of VMC Spindle For Maximum Cutting Force: Mahesh M. Ghadage Prof. Anurag V. Karandefujy fujyNo ratings yet

- Create Custom Pane Programmatically For Panels in Drupal 7Document2 pagesCreate Custom Pane Programmatically For Panels in Drupal 7CoklatNo ratings yet

- QSEE6800+H Signal Monitor Video and Thumbnail Streamer: Installation and Operation ManualDocument86 pagesQSEE6800+H Signal Monitor Video and Thumbnail Streamer: Installation and Operation ManualTechne PhobosNo ratings yet

- Indigo GdpiDocument1 pageIndigo Gdpimanoj agrawallaNo ratings yet

- MESL - Differential Equation 2Document9 pagesMESL - Differential Equation 2Mark-Lorie Duculan NonesNo ratings yet

- Furniture Plans How To Build A Rocking ChairDocument10 pagesFurniture Plans How To Build A Rocking ChairAntónio SousaNo ratings yet

- 2012 JBLM MILCON Tacoma Chamber of Commerce Oct2012Document13 pages2012 JBLM MILCON Tacoma Chamber of Commerce Oct2012Brackett427No ratings yet

- Balancing Redox ReactionsDocument2 pagesBalancing Redox ReactionsblobmarleyNo ratings yet

- Banyule Standard DrawingsDocument103 pagesBanyule Standard DrawingsTarek AbulailNo ratings yet

- Building A Big Data Platform For Smart Cities: Experience and Lessons From SantanderDocument8 pagesBuilding A Big Data Platform For Smart Cities: Experience and Lessons From SantanderDylan GuedesNo ratings yet

- Thermocouple & PRT Cable Selection GuideDocument15 pagesThermocouple & PRT Cable Selection Guidetees220510No ratings yet

- Instruction Manual Manuel D'Instruction Manual de InstruccionesDocument136 pagesInstruction Manual Manuel D'Instruction Manual de InstruccionesPrabish KumarNo ratings yet

- Aegis Multifunction RelayDocument4 pagesAegis Multifunction RelaySuranjana DasNo ratings yet

- Desmodure-Rfe-Tds CROSSLİNKİNG AGENTDocument2 pagesDesmodure-Rfe-Tds CROSSLİNKİNG AGENTGİZEM DEMİRNo ratings yet

- Silent Sound TechnologyDocument22 pagesSilent Sound TechnologyPurnima K100% (2)

- Tobaco VaccDocument19 pagesTobaco VaccSisay KebebeNo ratings yet

- Database Normalization Is The Process of Organizing The Fields and Tables of A Relational Database To Minimize RedundancyDocument2 pagesDatabase Normalization Is The Process of Organizing The Fields and Tables of A Relational Database To Minimize RedundancyStan DitonaNo ratings yet

- List of Organisations SAR147 Apr2012Document2 pagesList of Organisations SAR147 Apr2012Tan Lian KiatNo ratings yet

- Catalogue Cable Tray RevDocument40 pagesCatalogue Cable Tray RevhardiyantodonniNo ratings yet

- Westinghouse Manuals PDFDocument38 pagesWestinghouse Manuals PDFCarl HensonNo ratings yet

- Net Positive Suction HeadDocument4 pagesNet Positive Suction Headjorge alarconNo ratings yet

- FibrotexDocument2 pagesFibrotexMan ChupingNo ratings yet

- Accumulation-Mode Varactor Optimization for 200Q RF ICsDocument2 pagesAccumulation-Mode Varactor Optimization for 200Q RF ICsmenguemengueNo ratings yet